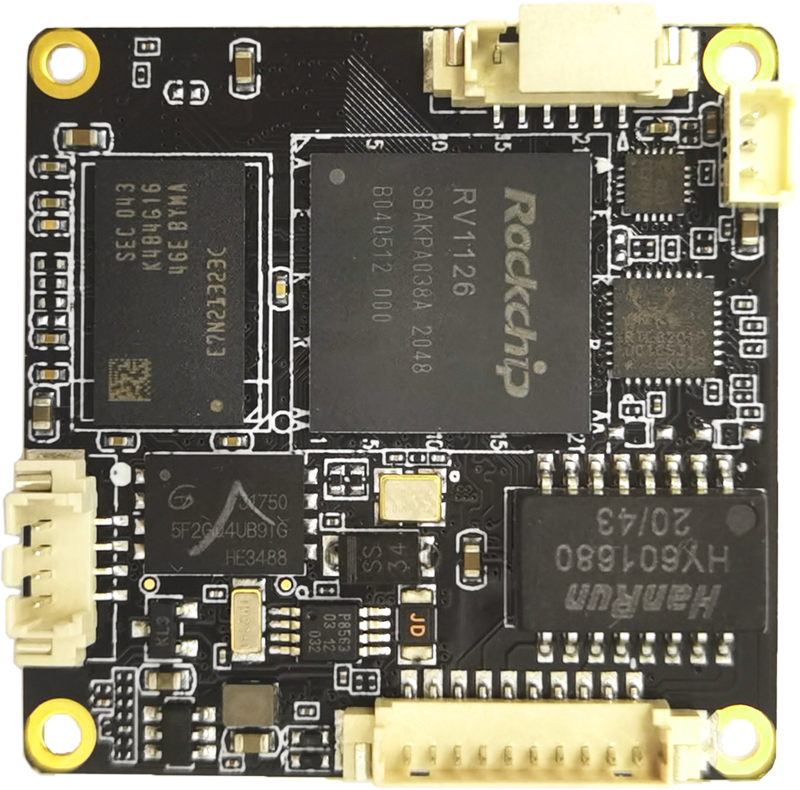

一、概述

Hi3519V101核心板是一款基于海思Hi3519V101多媒体处理芯片的核心板。Hi3519V101作为新一代行业专用HD IP摄像机SoC,集成新一代ISP,采用业界最新的H.265视频压缩编码器,基于先进低功耗工艺和低功耗架构设计,使其在低码率、高图像质量和低功耗方面引领行业水平。硬件支持90度/270度旋转功能和镜头几何校正功能,可以满足监控应用的各种场景需求。集成POR、RTC、Audio Codec、并支持多种Sensor电平及各种时钟输出等功能。 Hi3519V101核心板集成了Hi3519V101芯片、1GB DDR3 RAM、千兆以太网卡以及电源电路等,通过连接器与底板连接,可实现以太网、HDMI、USB、SD、CSI、BT1120等外设接口的扩展。

二、资源介绍

处理器

Hi3519V101 A7@800MHz,32KB I-Cache,32KB D-Cache /128KB L2 cache

A17@1.25GHz,32KB I-Cache,32KB D-Cache /256KB L2 cache

支持Neon加速,集成FPU处理单元

支持ARM® big.LITTLE大小核架构

视频编码

H.264 BP/MP/HP

H.265 Main Profile

H.264/H.265支持I/P/B帧,支持双P帧参考

支持MJPEG/JPEG Baseline编码

视频编码处理性能

H.264/H.265编码可支持最大分辨率为16M (4608x3456) Pixel

H.264/H.265多码流实时编码能力:3840*2160@30fps+1080P@30fps+3840*2160@2fps抓拍

支持最大JPEG抓拍性能3840*2160@30fps

支持CBR/VBR/FIXQP/AVBR/QPMAP五种码率控制模式

输出码率最高支持100Mbps

支持8个感兴趣区域(ROI)编码

智能视频分析

集成智能分析加速引擎,支持智能运动侦测、周界防范、视频诊断等多种智能分析应用

视频与图形处理

支持3D去噪、图像增强、动态对比度增强处理功能

支持视频、图形输出抗闪烁处理

支持视频1/30~16x缩放功能

支持两路视频无缝拼接

支持图形1/2~2x缩放功能

8个区域的编码前处理OSD叠加

ISP

支持两路独立ISP处理

支持3A (AE/AWB/AF) 功能,3A的控制用户可调节

支持去固定模式噪声(FPN)功能

支持强光抑制、背光补偿、Gamma、色彩增强

支持坏点校正、去噪、数字防抖

支持去雾

支持镜头畸变校正,支持鱼眼矫正

支持图像90度/270度旋转

支持图像Mirror、Flip

支持Sensor Build-In WDR、4F/3F/2F - Frame base/Line base WDR和Local Tone

mapping,其中第二路ISP只支持Sensor Build-In WDR、2F - Frame base/Line base

WDR和Local Tone mapping

提供PC端ISP tuning tools

音频编解码

通过软件实现多协议语音编解码

协议支持G.711、G.726、ADPCM

支持音频3A (AEC/ANR/ALC) 处理

安全引擎

硬件实现AES/DES/3DES三种加解密算法

硬件实现RSA1024/2048/4096签名校验算法

硬件实现HASH防篡改算法,支持HASH-SHA1/256、HMAC_SHA1/256算法

内部集成512Bit OTP存储空间和硬件随机数发生器

视频接口

输入

− 支持两路sensor输入,其中主通道最大分辨率支持到16M (4608x3456),第二路最大分辨率支持8M (4096x2160)

− 支持8/10/12/14 Bit RGB Bayer DC时序视频输入,时钟频率最高150MHz

− 支持BT.601、BT.656、BT.1120视频输入接口

− 主通路最大支持到12xLane MIPI/LVDS/Sub-LVDS/HiSPi接口

− 第二路Sensor接口最大支持4xLane MIPI/LVDS/Sub-LVDS/HiSPi接口

− 支持与SONY、Aptina、OmniVision、Panasonic等主流高清CMOS Sensor对接

− 兼容多种Sensor并行/差分接口电气特性

− 提供可编程Sensor时钟输出

输出

− 支持1路PAL/NTSC输出,支持负载自动检测

− 提供1个BT.1120/BT.656视频输出接口,用于外扩HDMI或SDI接口,最大支持1080P@60fps输出

− 支持LCD输出音频接口

集成Audio codec,支持16bit语音输入和输出

支持I2S接口,支持对接外部Audio codec

支持双声道Mic差分输入,降低底噪

外围接口

支持POR

支持外部复位输入

支持内部RTC

集成3通道LSADC

5个UART接口

IR接口、I2C接口、SSP主接口、GPIO接口

8个PWM接口(4个独立,4个复用其它管脚)

2个SD3.0/SDIO3.0接口,支持SDXC

1个USB3.0/2.0 Host/Device接口

1个PCIe2.0主/从模式

支持RGMII和RMII模式;支持10/100Mbps全双工或半双工模式,支持1000Mbps全双工模式;支持TSO网络加速

外部存储器接口

DDR4/DDR3/DDR3L/LPDDR3接口

− 支持32bit LPDDR3最高800MHz (1.6 Gbps)

− 支持32bit DDR4/3/3L最高933MHz (1.866Gbps)

− 单颗16bit DDR颗粒最大容量支持1024MB

− 两颗16bit DDR颗粒最大容量支持2048MB

SPI Nor Flash接口

− 支持1、2、4线模式

− 支持3Byte、4Byte地址模式

− 最大容量支持32MB

SPI Nand Flash接口

− 最大容量支持512MB

支持eMMC5.0接口

− 最大容量支持2TB

NAND Flash接口

− 8bit数据位宽

− 支持SLC、MLC

− 4、8、24、40、64Bit ECC

− 支持8GB以上容量器件

可选择从SPI Nor Flash、SPI Nand Flash或NAND Flash启动

支持从eMMC、PCIe启动

三、机械参数

接口定义

引脚信息

Hi3519V101核心板将Hi3519V101处理器引脚复用功能维持原定义、扩展或转换功能重新定义,用户可参考设计,以配合产品标准驱动的开发。为了保证产品设计具有良好的兼容性和稳定性,用户没有使用到的引脚资源请务必悬空处理。

Hi3531D核心板引脚定义

Hi3531D核心板所有引脚功能均按下表的“默认功能”作了规定,请勿轻易修改,否则可能和出厂驱动冲突。如有疑问,请及时联系我们的销售或技术支持。

(详细引脚定义请参照手册)

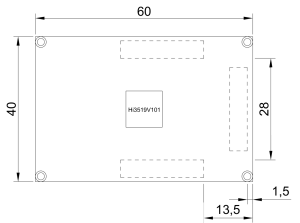

机械尺寸

Hi3519V101核心板机械尺寸如下图所示(单位:mm)。图中4个定位孔的内孔直径为2mm。

关注微信公众号

实时接收新的回答提醒和评论通知

客服微信: xxqk158820 / Ebaina-CN

客服微信: xxqk158820 / Ebaina-CN 客服手机: 17714209983

客服手机: 17714209983  客服邮箱: service@ebaina.com

客服邮箱: service@ebaina.com

QQ好友

QQ好友