奥利给~~

1363

- 收藏

- 点赞

- 分享

- 举报

当接收的数据没有标志位的时候,如何让计数器和数对齐?

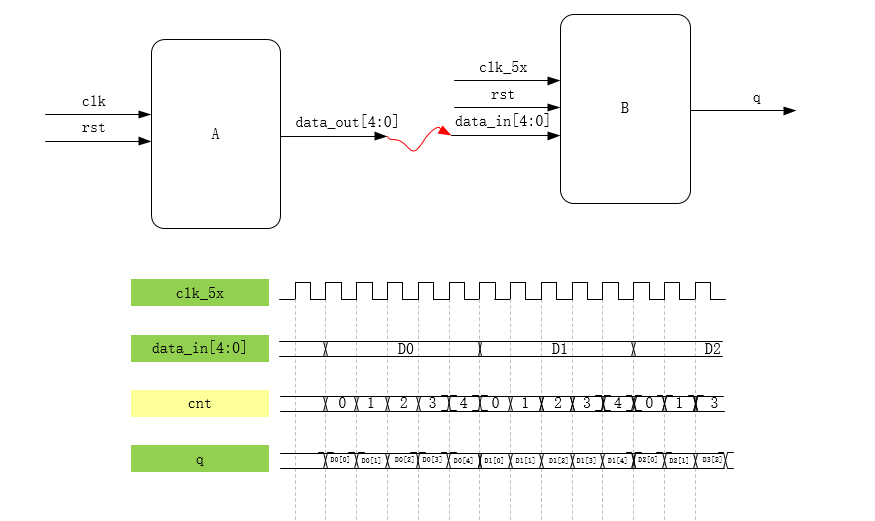

问题来源于2个模块之间需要传递数据,模块A负责每个时钟产生5bit并行数据,模块B(工作时钟是A的5倍)负责将接收的该数据以模块A的时钟频率的5倍串行发送出去,我的想法是用一个模5的加一计数器,作为发送数据的节拍,比如:计数0的时候发送数据的0位,计数1的时候发送数据的1位……计数4的时候发送数据的4位。

但是问题是,作为模块B,我其实不知道A的数据什么时候发来,如果我把计数器的计数值作为约束条件,有可能和数据之间是错位的,就会导致我发送的bit是不对的。

有什么好的解决方法吗?

我来回答

回答0个

时间排序

认可量排序

暂无数据

暂无数据

或将文件直接拖到这里

悬赏:

E币

网盘

* 网盘链接:

* 提取码:

悬赏:

E币

Markdown 语法

- 加粗**内容**

- 斜体*内容*

- 删除线~~内容~~

- 引用> 引用内容

- 代码`代码`

- 代码块```编程语言↵代码```

- 链接[链接标题](url)

- 无序列表- 内容

- 有序列表1. 内容

- 缩进内容

- 图片

相关问答

-

2012-12-24 14:52:36

-

2013-08-24 22:32:51

-

2015-11-04 12:05:37

-

2018-10-29 11:56:13

-

2020-11-22 18:03:55

-

2012-12-24 14:54:59

-

2013-08-27 16:11:25

-

2008-07-15 17:42:45

-

2013-11-16 10:13:44

-

2013-11-16 10:09:59

-

2023-08-08 12:24:20

-

2018-12-11 10:49:33

-

2021-01-06 16:19:08

-

2013-11-26 20:06:00

-

2012-12-24 14:56:39

-

2018-12-06 10:41:12

-

2018-11-08 16:32:10

-

2020-10-12 16:22:54

-

2008-10-02 20:40:04

无更多相似问答 去提问

点击登录

-- 积分

-- E币

提问

—

收益

—

被采纳

—

我要提问

切换马甲

上一页

下一页

悬赏问答

-

100hi3516cv610 通过易百纳官方SDK中编译出的uboot env kernel,移植到自己的工程中,MPP初始化时出现内核拷贝数据到用户端时出现错误导致内核进入pain模式进而时内核重启

-

5hisi3519 gs2972 bt1120 转sdi 无法正常显示问题

-

5hisi3516cv610 + gc4336p 夜晚很模糊

-

5AIISP(功能演示,SC4336P为BGGR,强制转RGGB,会导致颜色异常)

-

5rv1106使用luckfox的SDK,设备树和驱动都写好了,结果设备文件没有生成

-

5海思3516cv610中如何进行SD卡升级,根据官方文档操作,烧录进板子时,走的默认uboot,没有执行uboot升级。

-

5G610Q-IPC-38E 夜晚很暗 有什么办法解决吗 已经补光了

-

10转换模型时,SoC版本里没显示hi3516cv610芯片

-

5hisi3516cv610 使用 yolov8n 模型训练 要如何提高 这里识别的是人

-

10有人在海思平台接过SC035HGS吗

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

提醒

你的问题还没有最佳答案,是否结题,结题后将扣除20%的悬赏金

取消

确认

提醒

你的问题还没有最佳答案,是否结题,结题后将根据回答情况扣除相应悬赏金(1回答=1E币)

取消

确认

微信扫码分享

微信扫码分享 QQ好友

QQ好友