6565

- 收藏

- 点赞

- 分享

- 举报

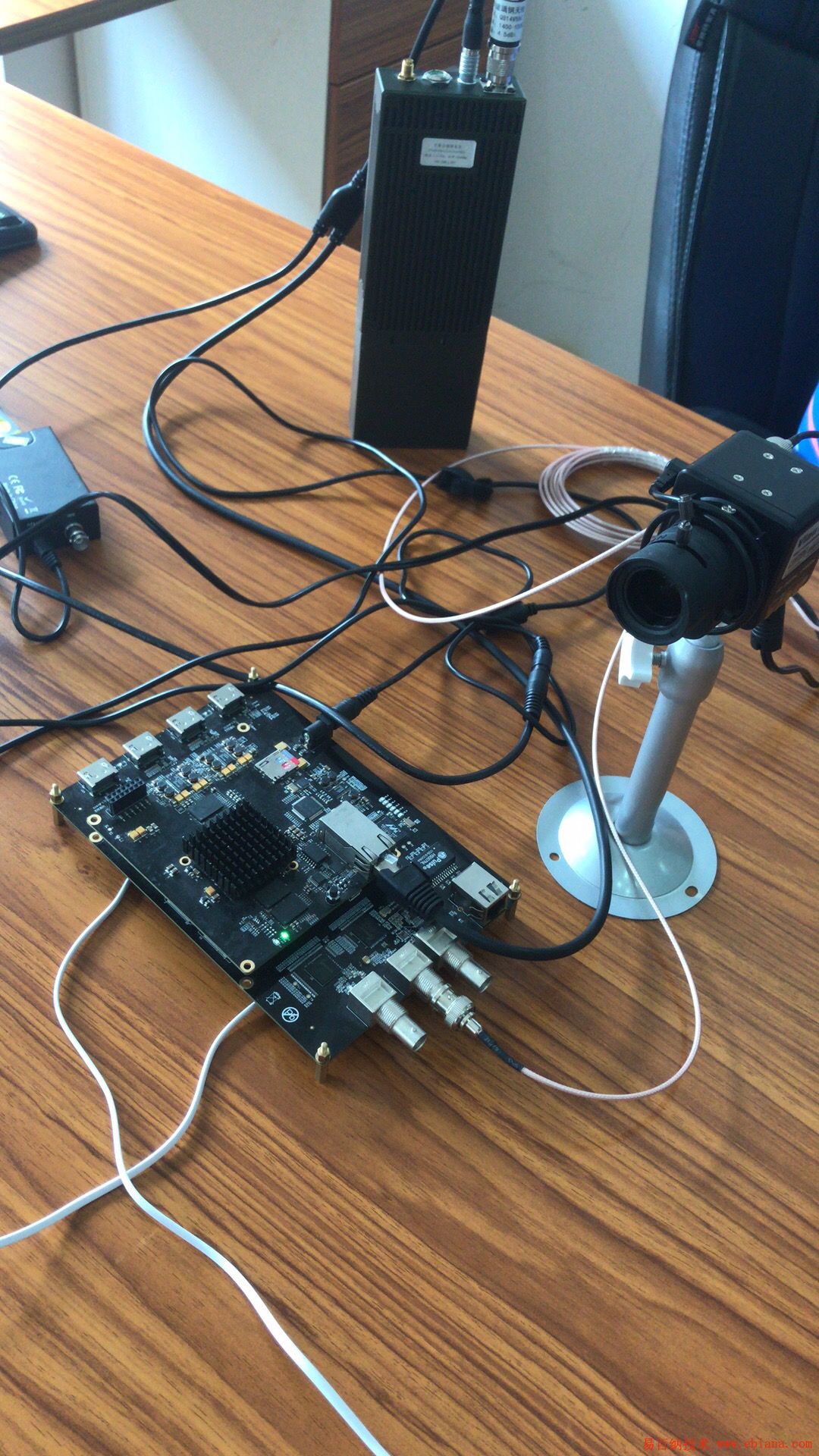

H.264视频编解码纯FPGA低延迟解决方案演示DEMO

本帖最后由 qn1525681036 于 2018-7-4 14:45 编辑

[url=https://v.qq.com/x/page/t0711t5fvhz.html]H.264视频编解码低延迟解决方案配合自组网电台[/url]

[url=https://v.qq.com/x/page/e0710rdfh52.html]H.264视频编解码低延迟解决方案多路输入输出[/url]

[url=https://v.qq.com/x/page/k0646tri3jx.html]H.264视频编解码FPGA解决方案原理讲解[/url]

[url=https://v.qq.com/x/page/o064633uglq.html]H.264视频编解码FPGA解决方案DEMO[/url]

点击以上文字将跳转到腾讯视频网站观看相关DEMO!

附件:H.264视频编解码FPGA解决方案.pdf

附件:H.264 IP core特点及性能介绍.pdf

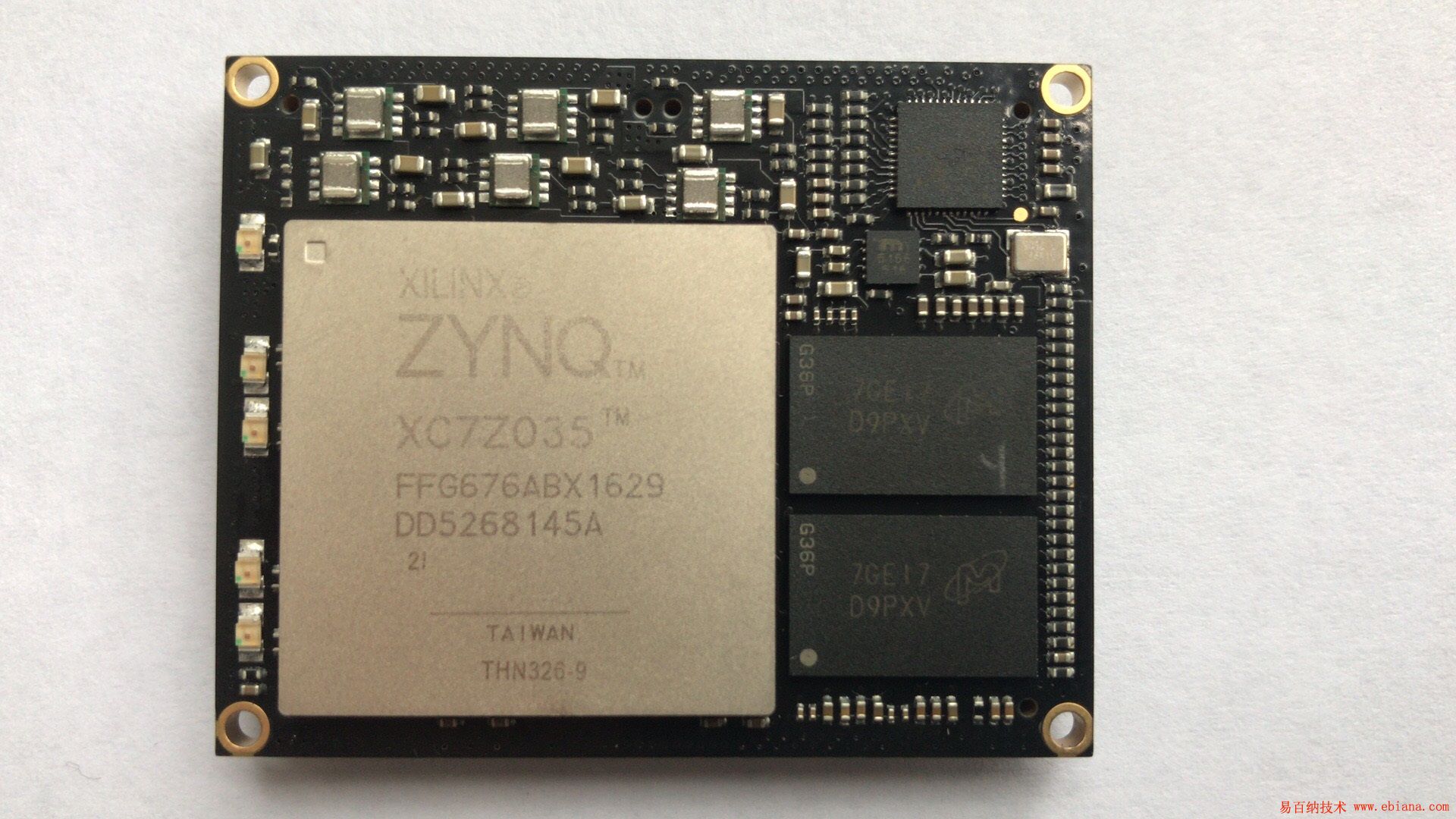

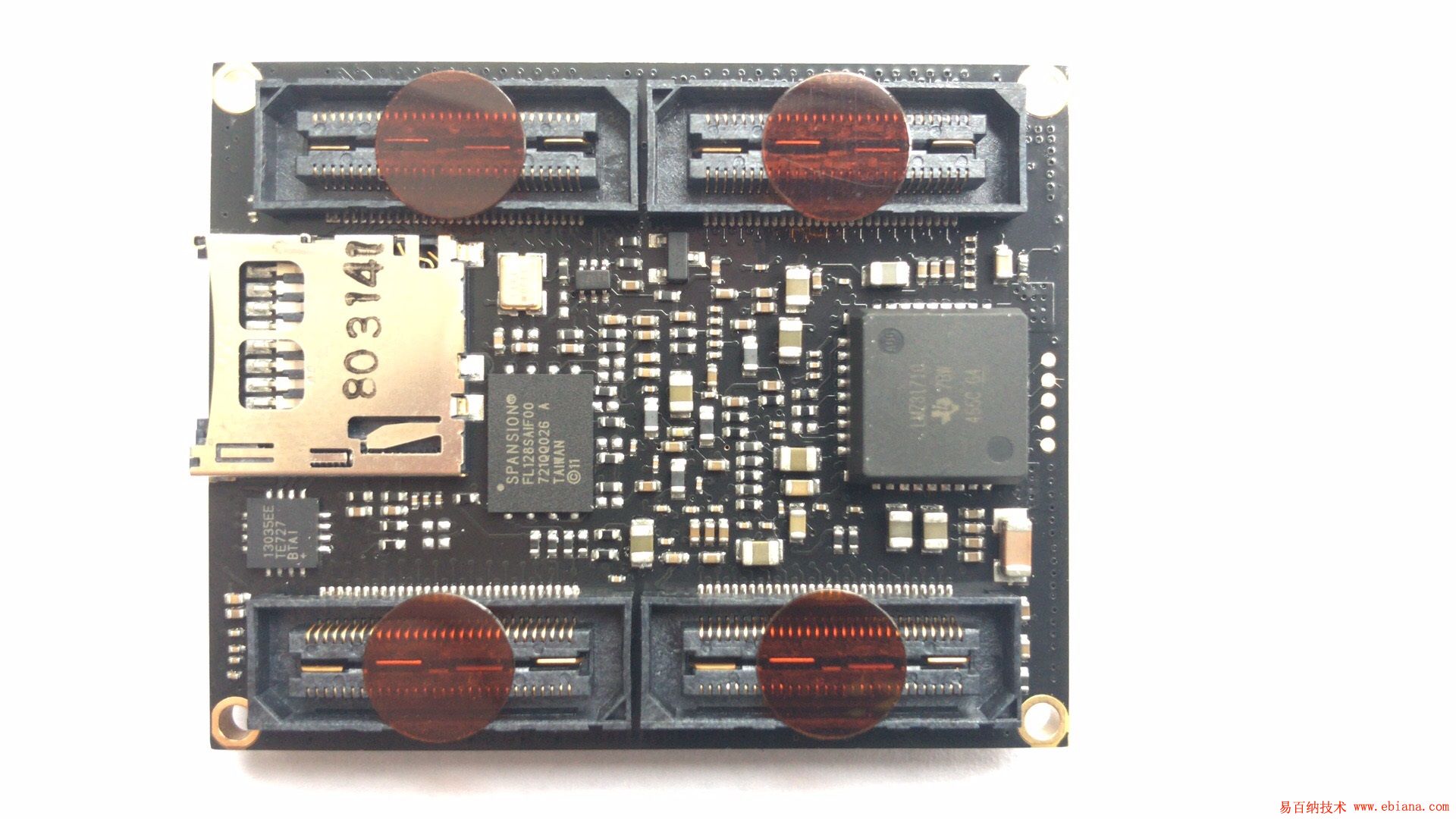

西安银亿电子科技有限公司基于多年的技术沉淀和工程化应用,提出该解决方案。该解决方案是全部代码自主研发,使用FPGA为核心器件,实现H.264编解码的IP核。此解决方案为纯硬件的解决方案,启动时间可以忽略,编解码延迟为固定的延迟,在一定的优化情况下,可以最大限度提升图像的压缩比。

该H264_Lite视频编解码器(encoder&decoder),其由硬件描述语言verilog实现,此设计经过FPGA EDA工具编译后可集成于可编程逻辑器件(FPGA)平台;也可以使用Synopsys Design Compiler综合后作为ASIC芯片的IP核使用。该视频编码器输出码流完全符合H.264视频编码标准;解码器能解码H264_Lite自己编码的码流。 该设计针对硬件面积,编码帧率,综合频率做了设计结构上的优化。 该设计对FPGA实现做了特别的时序优化,例如,在Xilinx Zynq7020上可以单核就能够实现1080P@60fps的FPGA应用场景,双核可以实现4K@30fps以上的应用场景。

2. 具体特点

1) 支持各种分辨率

单core最大支持的分辨率为4K;视频分辨率配置灵活,支持各种非标分辨率,如1024*1024等;可通过多个core的并行处理,支持4K*2K、4K*4K等超高分辨率。可支持多路不同分辨率视频输入,编解码后输出。

2) 支持各种帧率

单core最大可支持4K/30fps,1080P/120fps。可根据硬件资源和客户需求提供帧率定制,如960P/120fps等。

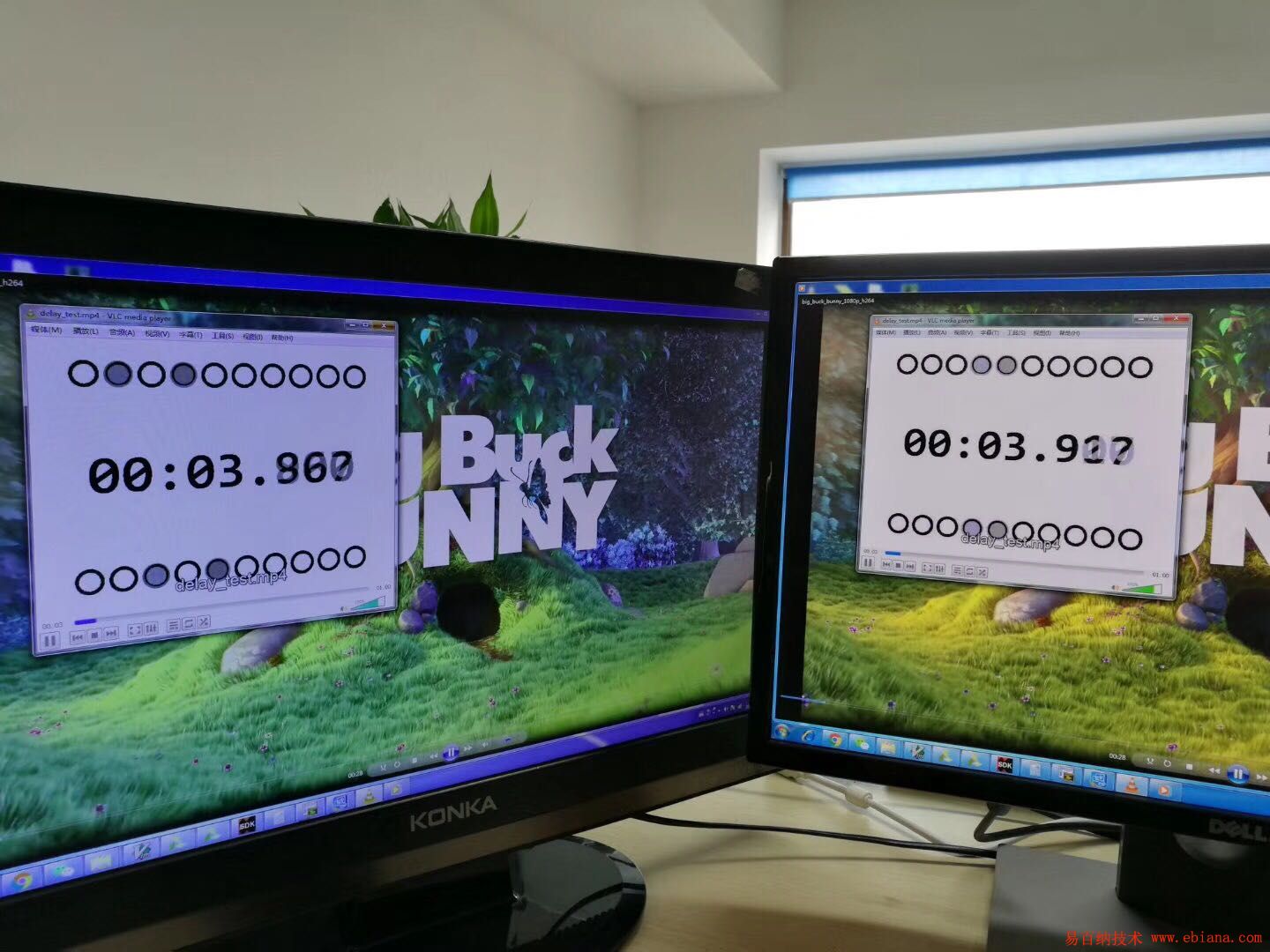

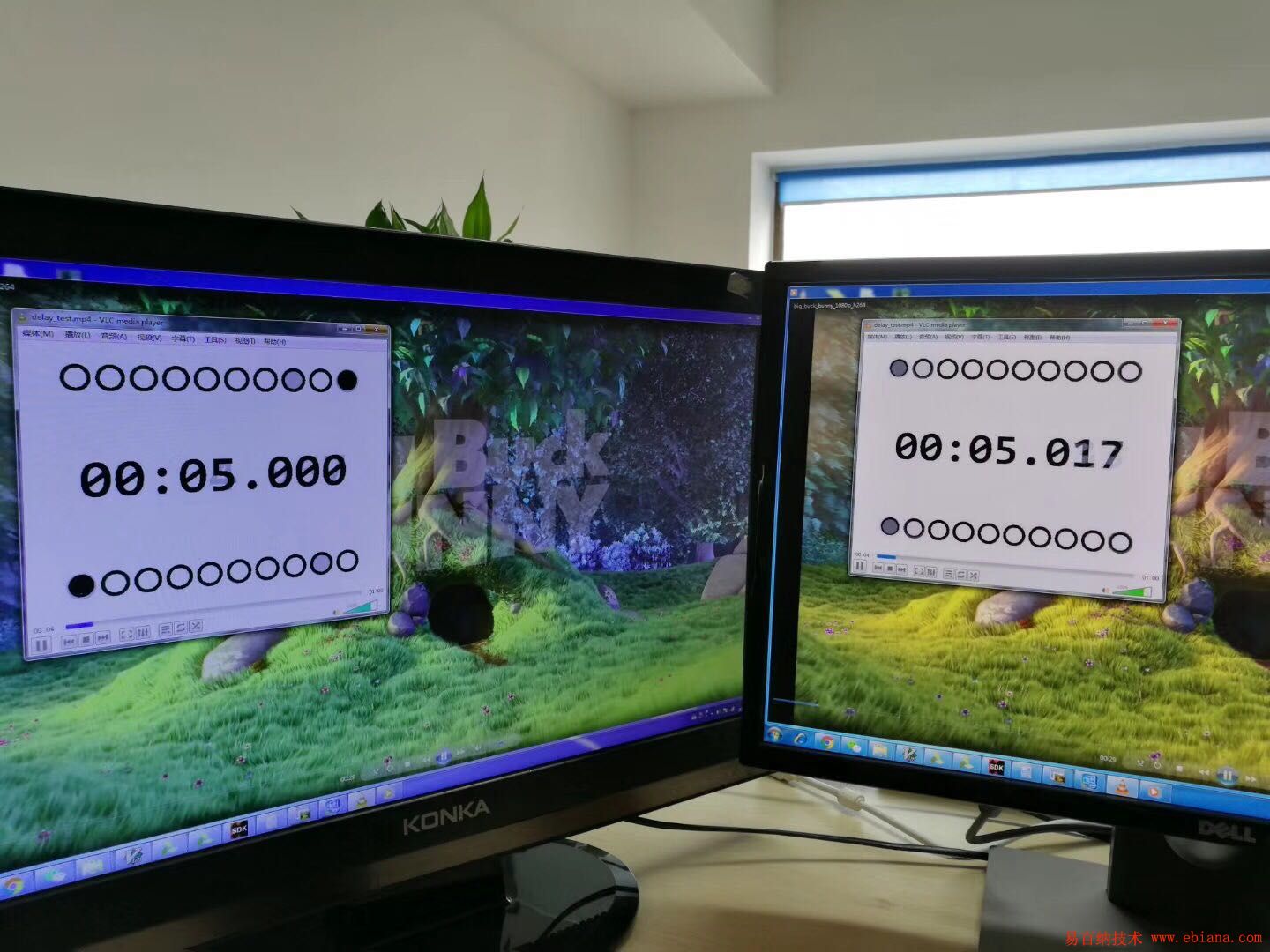

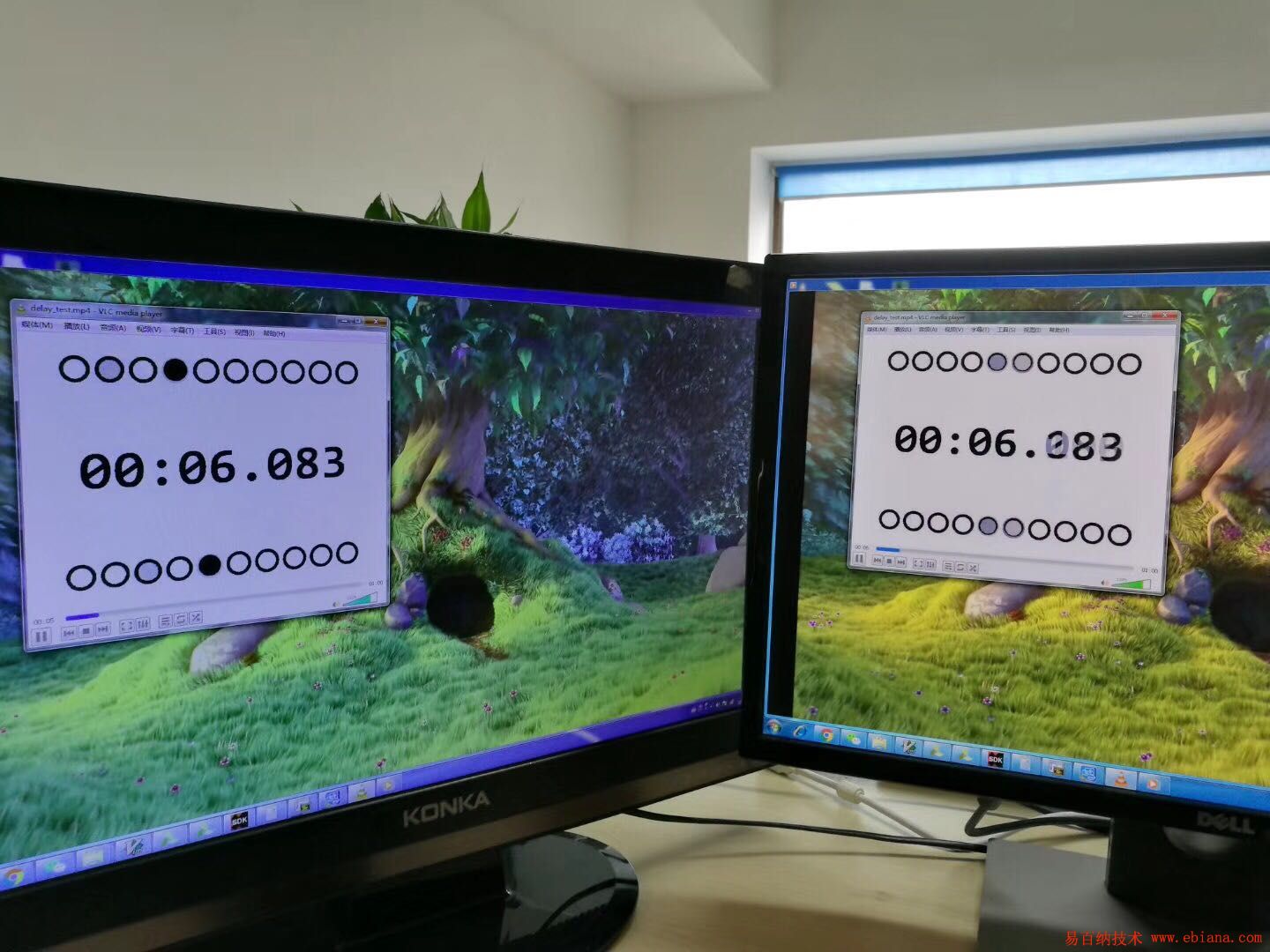

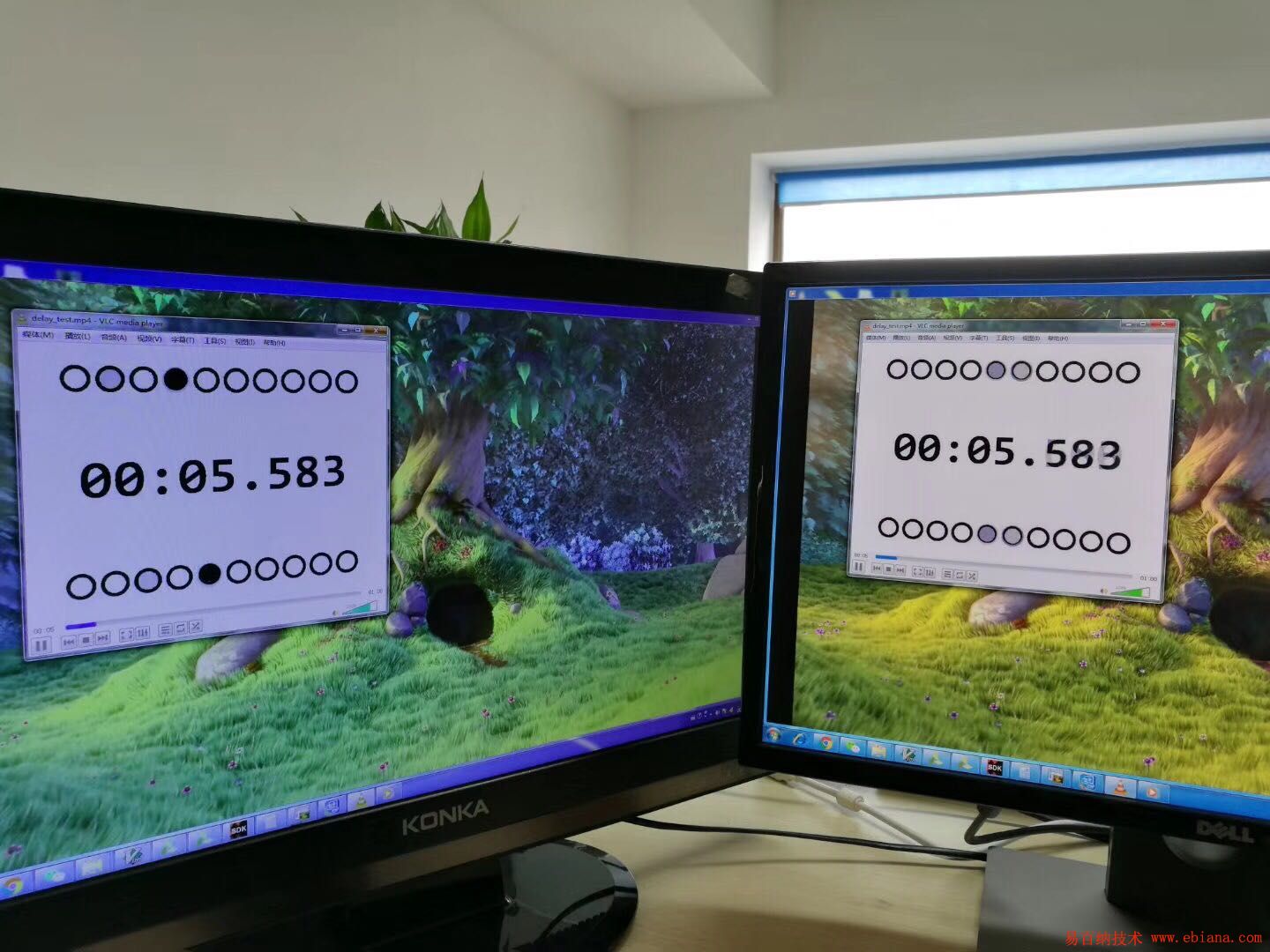

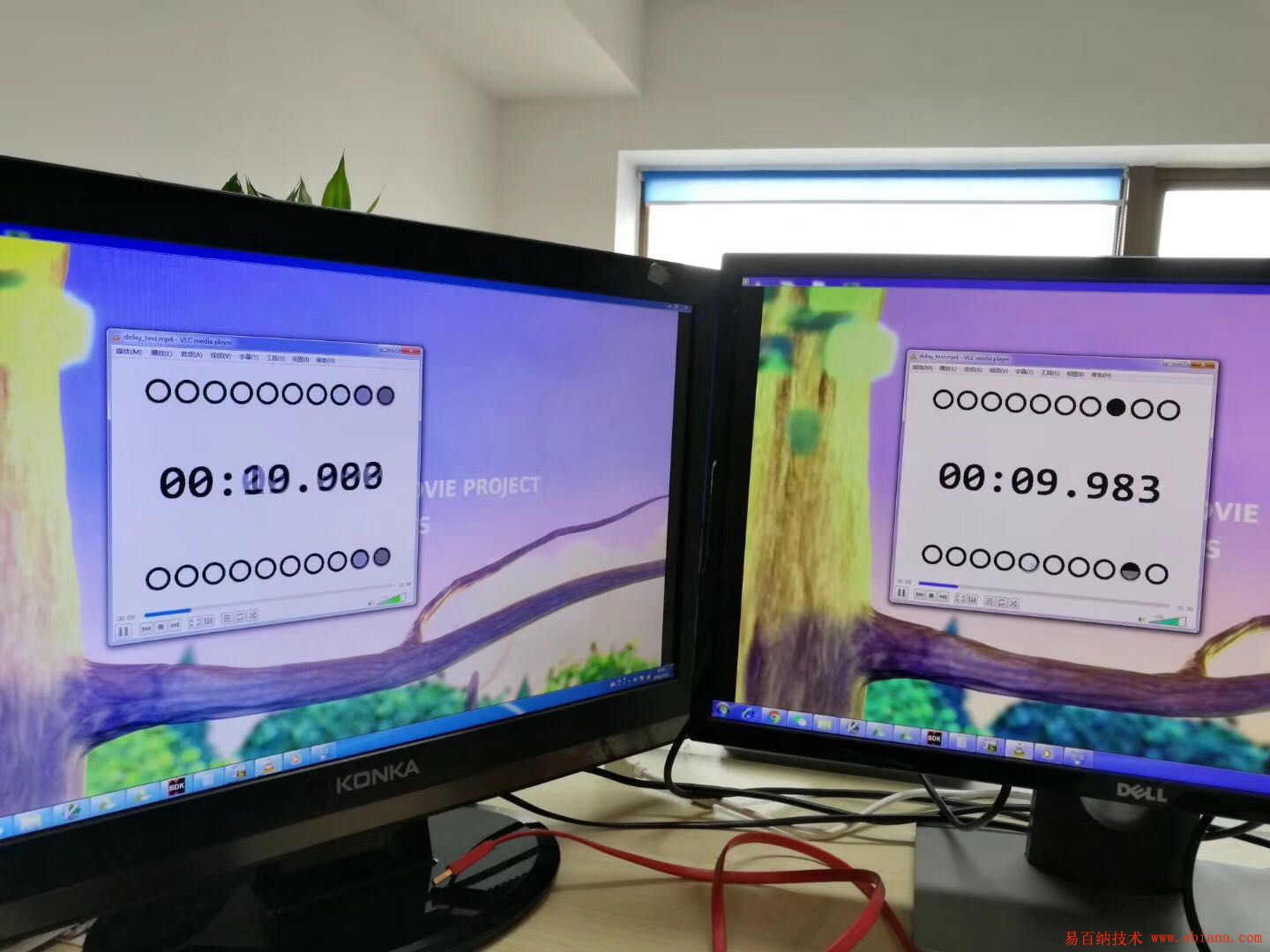

3) 编解码延迟低

编码的延迟低至0.5ms左右,解码的延迟15ms以下,由编码,传输码流,到解码,所组成的完整系统中,延时在30-60ms左右;特殊应用场景解码延时可进一步优化至10ms以下。

4) 占用FPGA资源小

单core所占的资源中,LUT占用最多,约为29000多个,其他的资源在占用率方面,均比LUT占比小。例如,在zynq7020上,只占55%的逻辑资源,硬件功耗超低。

5) 码率控制灵活

带宽受限时,可以通过动态调整QP值(图像质量),将码流控制在要求的带宽之下。在带宽足够时,可以稳定QP值(图像质量),以达到较好的图像质量要求。

6) 超长GOP支持

最大可以256帧才编码一个I frame,削减码流带宽高峰,仍保持优秀的容错性。

7) 定制性强

可根据实际需求优化代码,提供例如局部QP(图像质量)增强等定制化的修改。

8) 可移植性强

在保证硬件资源的情况下,可支持不同厂家的FPGA,兼容性、可移植性超强。

9) 应用领域

低带宽下、超低延时的星载/机载/弹载/车载视频数据链;

需要超高清晰度、超低延时的摄像监控系统;

海量视频数据压缩、存储等。

[url=https://v.qq.com/x/page/t0711t5fvhz.html]H.264视频编解码低延迟解决方案配合自组网电台[/url]

[url=https://v.qq.com/x/page/e0710rdfh52.html]H.264视频编解码低延迟解决方案多路输入输出[/url]

[url=https://v.qq.com/x/page/k0646tri3jx.html]H.264视频编解码FPGA解决方案原理讲解[/url]

[url=https://v.qq.com/x/page/o064633uglq.html]H.264视频编解码FPGA解决方案DEMO[/url]

点击以上文字将跳转到腾讯视频网站观看相关DEMO!

附件:H.264视频编解码FPGA解决方案.pdf

附件:H.264 IP core特点及性能介绍.pdf

西安银亿电子科技有限公司基于多年的技术沉淀和工程化应用,提出该解决方案。该解决方案是全部代码自主研发,使用FPGA为核心器件,实现H.264编解码的IP核。此解决方案为纯硬件的解决方案,启动时间可以忽略,编解码延迟为固定的延迟,在一定的优化情况下,可以最大限度提升图像的压缩比。

该H264_Lite视频编解码器(encoder&decoder),其由硬件描述语言verilog实现,此设计经过FPGA EDA工具编译后可集成于可编程逻辑器件(FPGA)平台;也可以使用Synopsys Design Compiler综合后作为ASIC芯片的IP核使用。该视频编码器输出码流完全符合H.264视频编码标准;解码器能解码H264_Lite自己编码的码流。 该设计针对硬件面积,编码帧率,综合频率做了设计结构上的优化。 该设计对FPGA实现做了特别的时序优化,例如,在Xilinx Zynq7020上可以单核就能够实现1080P@60fps的FPGA应用场景,双核可以实现4K@30fps以上的应用场景。

2. 具体特点

1) 支持各种分辨率

单core最大支持的分辨率为4K;视频分辨率配置灵活,支持各种非标分辨率,如1024*1024等;可通过多个core的并行处理,支持4K*2K、4K*4K等超高分辨率。可支持多路不同分辨率视频输入,编解码后输出。

2) 支持各种帧率

单core最大可支持4K/30fps,1080P/120fps。可根据硬件资源和客户需求提供帧率定制,如960P/120fps等。

3) 编解码延迟低

编码的延迟低至0.5ms左右,解码的延迟15ms以下,由编码,传输码流,到解码,所组成的完整系统中,延时在30-60ms左右;特殊应用场景解码延时可进一步优化至10ms以下。

4) 占用FPGA资源小

单core所占的资源中,LUT占用最多,约为29000多个,其他的资源在占用率方面,均比LUT占比小。例如,在zynq7020上,只占55%的逻辑资源,硬件功耗超低。

5) 码率控制灵活

带宽受限时,可以通过动态调整QP值(图像质量),将码流控制在要求的带宽之下。在带宽足够时,可以稳定QP值(图像质量),以达到较好的图像质量要求。

6) 超长GOP支持

最大可以256帧才编码一个I frame,削减码流带宽高峰,仍保持优秀的容错性。

7) 定制性强

可根据实际需求优化代码,提供例如局部QP(图像质量)增强等定制化的修改。

8) 可移植性强

在保证硬件资源的情况下,可支持不同厂家的FPGA,兼容性、可移植性超强。

9) 应用领域

低带宽下、超低延时的星载/机载/弹载/车载视频数据链;

需要超高清晰度、超低延时的摄像监控系统;

海量视频数据压缩、存储等。

文件: H.264 IP core特点及性能介绍.pdf

文件: H.264 IP core特点及性能介绍.pdf

下载

文件: H.264视频编解码FPGA解决方案.pdf

文件: H.264视频编解码FPGA解决方案.pdf

下载

我来回答

回答6个

时间排序

认可量排序

认可0

认可0

认可0

认可0

认可0

认可0

或将文件直接拖到这里

悬赏:

E币

网盘

* 网盘链接:

* 提取码:

悬赏:

E币

Markdown 语法

- 加粗**内容**

- 斜体*内容*

- 删除线~~内容~~

- 引用> 引用内容

- 代码`代码`

- 代码块```编程语言↵代码```

- 链接[链接标题](url)

- 无序列表- 内容

- 有序列表1. 内容

- 缩进内容

- 图片

相关问答

-

2018-06-25 12:00:02

-

2018-06-22 11:31:34

-

2020-10-06 12:06:08

-

82017-12-07 16:55:14

-

2020-03-12 09:35:44

-

2020-09-25 16:00:20

-

2018-10-12 18:02:28

-

2014-08-10 22:23:09

-

2019-06-08 12:07:02

-

2021-06-17 15:51:50

-

2014-05-23 13:47:17

-

2016-08-18 17:41:33

-

252014-12-29 14:49:27

-

2017-03-09 16:42:56

-

2016-03-19 15:36:24

-

2016-03-27 17:02:45

-

2018-08-16 10:02:22

-

2015-03-09 16:56:23

-

2017-03-10 09:34:16

无更多相似问答 去提问

点击登录

-- 积分

-- E币

提问

—

收益

—

被采纳

—

我要提问

切换马甲

上一页

下一页

悬赏问答

-

5hi3516dv500改了sensor驱动后使用pqtools出图出现彩色的竖条纹

-

10海思3559的VGS模块在VI上画线问题

-

53519dv500接lvds的sensor mn34120,图像出现很多竖线,sensor板接以前的3519v101没问题

-

103403外接hdmi口1024*600显示屏报错

-

5SS928点DC camera的6946,全屏紫色

-

5hi3519 的 网络传输的MTU值可以修改到比1500大嘛?

-

10WS73V100星闪扫描不到设备sle

-

5SS928/SD3403 录像失败 venc stream time out, exit thread; venc 2 stream buffer is full

-

10Hi3516DV500无法运行PQTool软件

-

10君正T23+1084带TF卡插卡(给该主板适配TF卡驱动,电机驱动,适配GPIO)

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

提醒

你的问题还没有最佳答案,是否结题,结题后将扣除20%的悬赏金

取消

确认

提醒

你的问题还没有最佳答案,是否结题,结题后将根据回答情况扣除相应悬赏金(1回答=1E币)

取消

确认

微信扫码分享

微信扫码分享 QQ好友

QQ好友