一个爱徒步的~IT民工

4049

- 收藏

- 点赞

- 分享

- 举报

Hi3519V101 项目讨论组进度

目前项目进展正常:

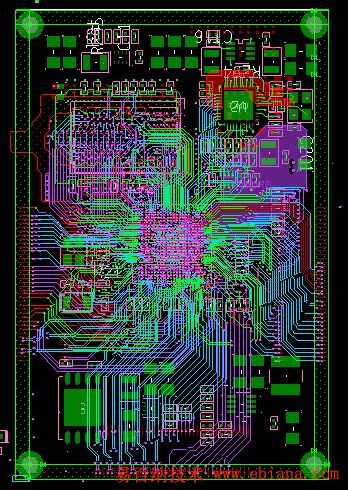

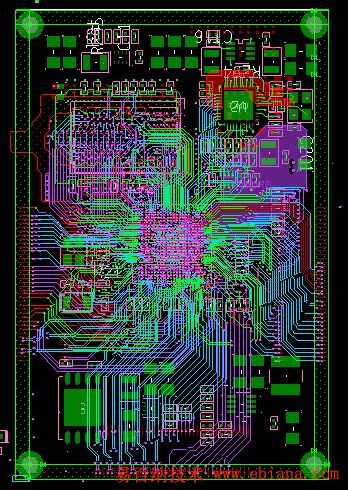

Core Board在做最后审查,因为工艺是八层二阶板子,打板价格昂贵,所以比较谨慎,下面上图,预计节后发板

hi3519V101的性能

Processor Core

800 MHz A7 core, supporting 32 KB I-cache, 32 KB Dcache,

and 128 KB L2 cache

1.25G GHz A17 core, supporting 32 KB I-cache, 32 KB

D-cache, and 256 KB L2 cache

Neon acceleration, integrated FPU

Video Encoding

H.264 BP/MP/HP

H.265 Main Profile

I/P/B frame, dual-P-frame reference

MJPEG/JPEG baseline encoding

性能:

Video Encoding Performance

Maximum 16-megapixel (4608 x 3456) resolution for

H.264/H.265 encoding

Real-time multi-stream H.264/H.265 encoding capability:

3840 x 2160@30 fps+1080p@30 fps + 3840 x 2160@2fps

snapshot

Maximum JPEG snapshot performance of 3840 x

2160@30 fps

CBR, VBR, FIXQP, AVBR, and QPMAP modes

Maximum100 Mbit/s output bit rate

Encoding of eight ROIs

智能分析:

Integrated IVE, supporting various intelligent analysis

applications such as motion detection, perimeter defense,

and video diagnosis

Video and Graphics Processing

3D denoising, image enhancement, and dynamic contrast

improvement

Anti-flicker for output videos and graphics

1/30x to 16x video scaling

Seamless splicing of 2-channel videos

1/2x to 2x graphics scaling

OSD overlaying of eight regions before encoding

Video graphics overlaying of two layers (video layer and

graphics layer)

ISP

2-channel independent ISP processing

Adjustable 3A functions (AE, AWB, and AF)

FPN removal

Highlight compensation, backlight compensation, gamma

correction, and color enhancement

Defect pixel correction, denoising, and digital image

stabilization

Anti-fog

Lens distortion correction and fisheye correction

Picture rotation by 90° or 270°

Picture mirroring and flipping

Sensor built-in WDR, 4F/3F/2F frame-based/line-based

WDR, and local tone mapping. The second channel of ISP

其它参照官方SDK

Core Board在做最后审查,因为工艺是八层二阶板子,打板价格昂贵,所以比较谨慎,下面上图,预计节后发板

hi3519V101的性能

Processor Core

800 MHz A7 core, supporting 32 KB I-cache, 32 KB Dcache,

and 128 KB L2 cache

1.25G GHz A17 core, supporting 32 KB I-cache, 32 KB

D-cache, and 256 KB L2 cache

Neon acceleration, integrated FPU

Video Encoding

H.264 BP/MP/HP

H.265 Main Profile

I/P/B frame, dual-P-frame reference

MJPEG/JPEG baseline encoding

性能:

Video Encoding Performance

Maximum 16-megapixel (4608 x 3456) resolution for

H.264/H.265 encoding

Real-time multi-stream H.264/H.265 encoding capability:

3840 x 2160@30 fps+1080p@30 fps + 3840 x 2160@2fps

snapshot

Maximum JPEG snapshot performance of 3840 x

2160@30 fps

CBR, VBR, FIXQP, AVBR, and QPMAP modes

Maximum100 Mbit/s output bit rate

Encoding of eight ROIs

智能分析:

Integrated IVE, supporting various intelligent analysis

applications such as motion detection, perimeter defense,

and video diagnosis

Video and Graphics Processing

3D denoising, image enhancement, and dynamic contrast

improvement

Anti-flicker for output videos and graphics

1/30x to 16x video scaling

Seamless splicing of 2-channel videos

1/2x to 2x graphics scaling

OSD overlaying of eight regions before encoding

Video graphics overlaying of two layers (video layer and

graphics layer)

ISP

2-channel independent ISP processing

Adjustable 3A functions (AE, AWB, and AF)

FPN removal

Highlight compensation, backlight compensation, gamma

correction, and color enhancement

Defect pixel correction, denoising, and digital image

stabilization

Anti-fog

Lens distortion correction and fisheye correction

Picture rotation by 90° or 270°

Picture mirroring and flipping

Sensor built-in WDR, 4F/3F/2F frame-based/line-based

WDR, and local tone mapping. The second channel of ISP

其它参照官方SDK

我来回答

回答6个

时间排序

认可量排序

认可0

认可0

认可0

认可0

认可0

认可0

或将文件直接拖到这里

悬赏:

E币

网盘

* 网盘链接:

* 提取码:

悬赏:

E币

Markdown 语法

- 加粗**内容**

- 斜体*内容*

- 删除线~~内容~~

- 引用> 引用内容

- 代码`代码`

- 代码块```编程语言↵代码```

- 链接[链接标题](url)

- 无序列表- 内容

- 有序列表1. 内容

- 缩进内容

- 图片

相关问答

-

2018-05-07 11:20:17

-

2018-09-14 17:40:48

-

2019-06-13 20:17:32

-

2019-04-13 17:16:08

-

2019-04-11 16:27:32

-

2018-08-20 17:10:00

-

2018-08-21 16:29:27

-

2019-09-19 10:44:02

-

2019-04-23 18:32:16

-

2017-11-02 09:36:11

-

2016-11-22 10:27:57

-

2018-04-28 10:12:32

-

2017-12-06 10:26:46

-

2019-10-10 20:13:30

-

2019-08-22 11:25:07

-

2019-03-27 16:45:01

-

2018-12-19 11:24:06

-

2018-12-19 11:24:29

-

2019-12-02 12:00:20

无更多相似问答 去提问

点击登录

-- 积分

-- E币

提问

—

收益

—

被采纳

—

我要提问

切换马甲

上一页

下一页

悬赏问答

-

5hi3516dv500改了sensor驱动后使用pqtools出图出现彩色的竖条纹

-

10海思3559的VGS模块在VI上画线问题

-

53519dv500接lvds的sensor mn34120,图像出现很多竖线,sensor板接以前的3519v101没问题

-

103403外接hdmi口1024*600显示屏报错

-

5SS928点DC camera的6946,全屏紫色

-

5hi3519 的 网络传输的MTU值可以修改到比1500大嘛?

-

10WS73V100星闪扫描不到设备sle

-

5SS928/SD3403 录像失败 venc stream time out, exit thread; venc 2 stream buffer is full

-

10Hi3516DV500无法运行PQTool软件

-

10君正T23+1084带TF卡插卡(给该主板适配TF卡驱动,电机驱动,适配GPIO)

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

提醒

你的问题还没有最佳答案,是否结题,结题后将扣除20%的悬赏金

取消

确认

提醒

你的问题还没有最佳答案,是否结题,结题后将根据回答情况扣除相应悬赏金(1回答=1E币)

取消

确认

微信扫码分享

微信扫码分享 QQ好友

QQ好友