2149

- 收藏

- 点赞

- 分享

- 举报

[已解决]3531A VI接入8bit BT656信号,标清信号576I收不到中断。

本帖最后由 colorjun 于 2017-12-22 12:02 编辑

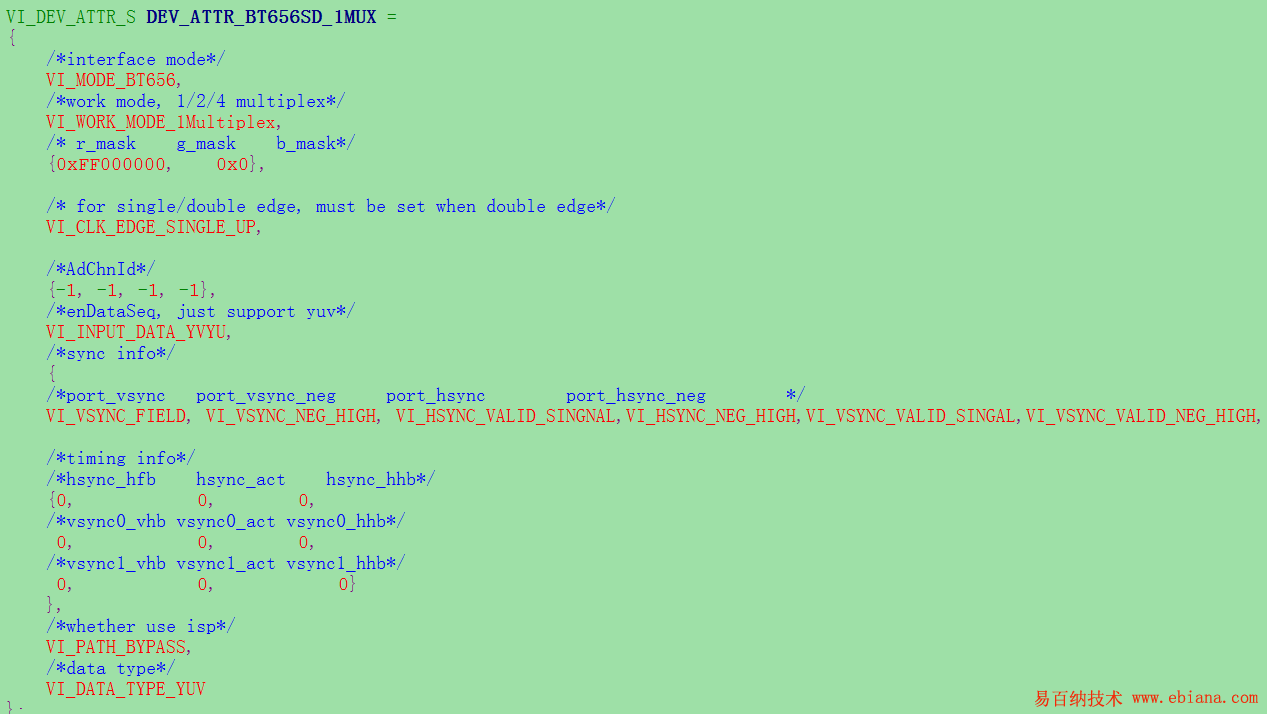

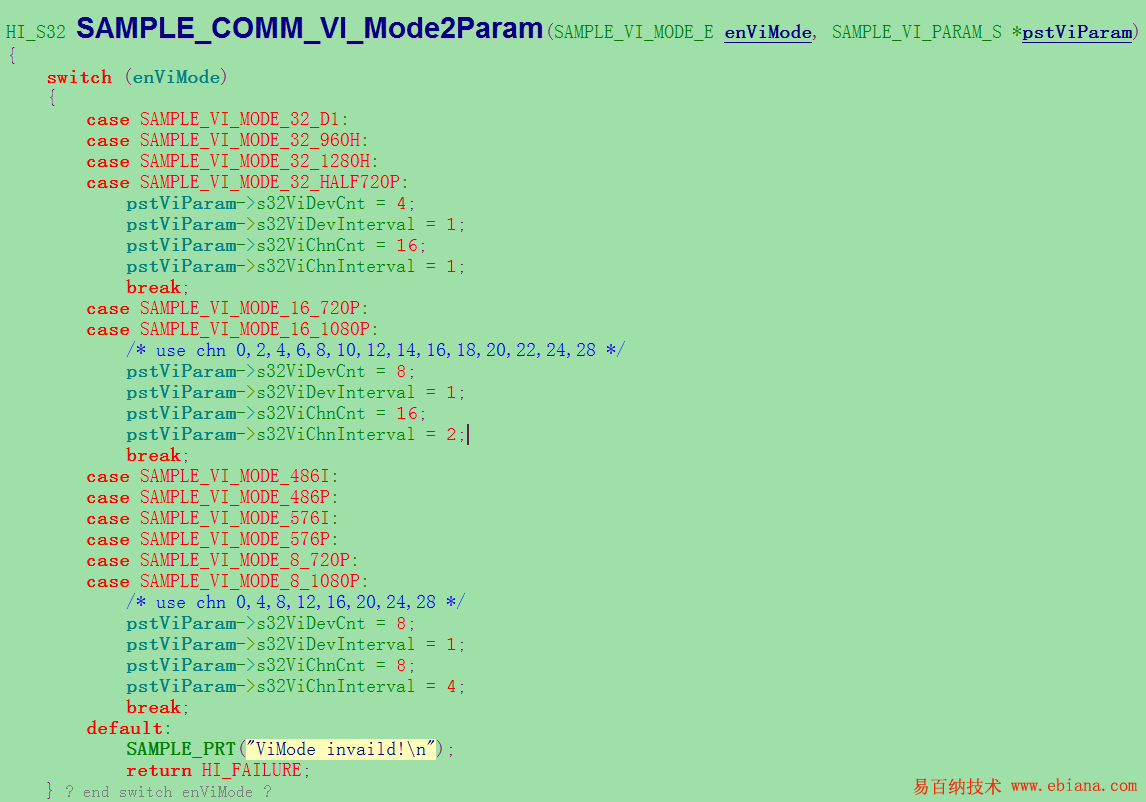

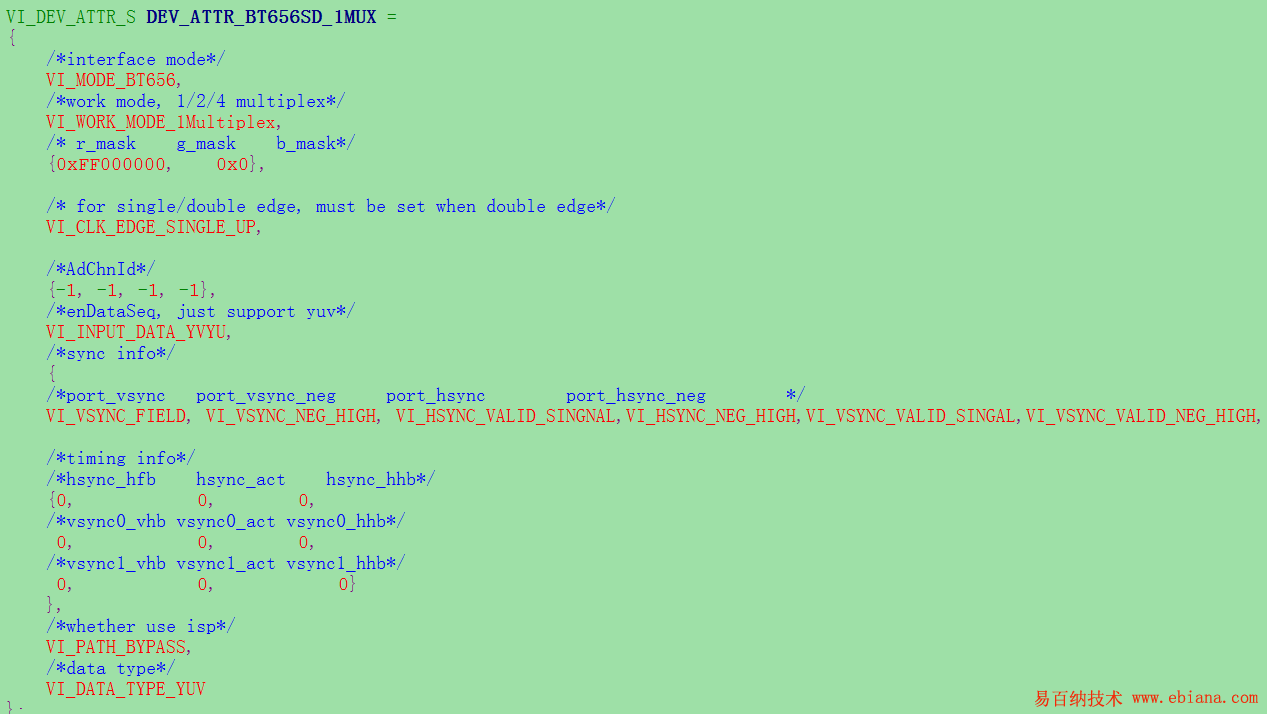

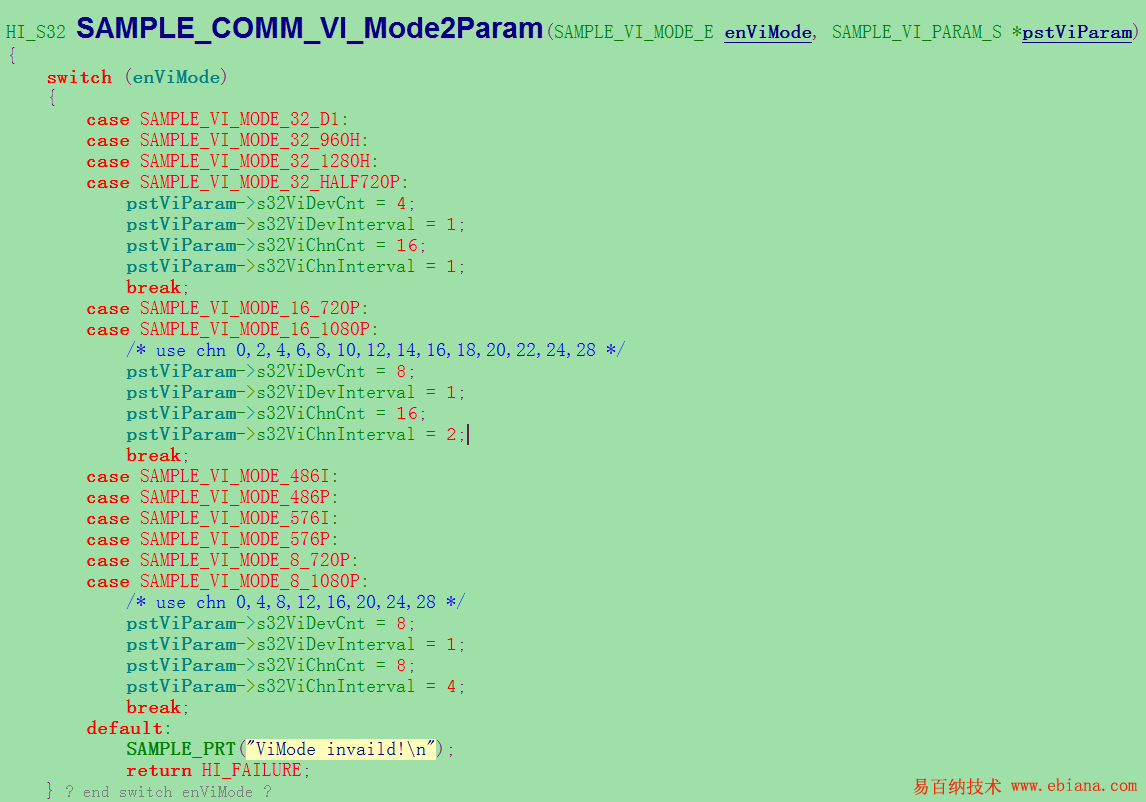

3531A的VI与FPGA之间使用8路8bit数据加一路时钟,在使用BT1120时序接收高清都720,1080,I和P都没问题。在接收标清信号时,FPGA的SDI IP 输出10bit的BT656时序,将高8bit送入3531A。在修改sample_vio后,cat vi看进不了中断。

麻烦问一下,在修改sample_vio接收标清需要修改哪些?我主要做了如下修改

3531A的VI与FPGA之间使用8路8bit数据加一路时钟,在使用BT1120时序接收高清都720,1080,I和P都没问题。在接收标清信号时,FPGA的SDI IP 输出10bit的BT656时序,将高8bit送入3531A。在修改sample_vio后,cat vi看进不了中断。

麻烦问一下,在修改sample_vio接收标清需要修改哪些?我主要做了如下修改

我来回答

回答2个

时间排序

认可量排序

认可0

认可0

或将文件直接拖到这里

悬赏:

E币

网盘

* 网盘链接:

* 提取码:

悬赏:

E币

Markdown 语法

- 加粗**内容**

- 斜体*内容*

- 删除线~~内容~~

- 引用> 引用内容

- 代码`代码`

- 代码块```编程语言↵代码```

- 链接[链接标题](url)

- 无序列表- 内容

- 有序列表1. 内容

- 缩进内容

- 图片

相关问答

-

2016-01-12 15:44:45

-

2017-12-20 18:26:12

-

2019-01-25 17:49:04

-

2016-12-27 12:04:33

-

2016-11-03 09:52:27

-

2017-08-14 11:49:42

-

2019-09-24 15:38:57

-

2019-06-05 16:16:50

-

2022-11-29 17:21:33

-

2024-03-05 18:08:33

-

2018-04-13 10:18:14

-

2020-03-14 17:43:56

-

2019-12-23 20:27:52

-

2018-08-06 18:53:48

-

2022-02-21 09:41:20

-

2017-01-14 14:49:24

-

2019-03-03 02:04:08

-

2023-06-20 15:02:27

-

2015-07-29 16:43:18

无更多相似问答 去提问

点击登录

-- 积分

-- E币

提问

—

收益

—

被采纳

—

我要提问

切换马甲

上一页

下一页

悬赏问答

-

5SS928的emmc有32GB,bootargs设置使用16GB,但是为啥能用的只有rootfs的大小

-

33SS928怎样烧写ubuntu系统

-

10ToolPlatform下载rootfs提示网络失败

-

10谁有GK7205V500的SDK

-

5Hi3516CV610 烧录不进去

-

10Hi3559AV100 芯片硬解码h265编码格式的视频时出现视频播放错误,解码错误信息 s32PackErr:码流有错

-

5海思SS928 / SD3403的sample_venc.c摄像头编码Demo中,采集到的摄像头的YUV数据在哪个相关的函数中?

-

5海鸥派openEuler无法启动网卡,连接WIFI存在问题

-

66有没有ISP相关的巨佬帮忙看看SS928对接IMX347的图像问题

-

50求助hi3559与FPGA通过SLVS-EC接口对接问题

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

提醒

你的问题还没有最佳答案,是否结题,结题后将扣除20%的悬赏金

取消

确认

提醒

你的问题还没有最佳答案,是否结题,结题后将根据回答情况扣除相应悬赏金(1回答=1E币)

取消

确认

微信扫码分享

微信扫码分享 QQ好友

QQ好友