4625

- 收藏

- 点赞

- 分享

- 举报

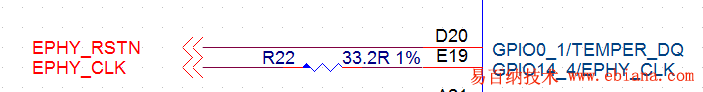

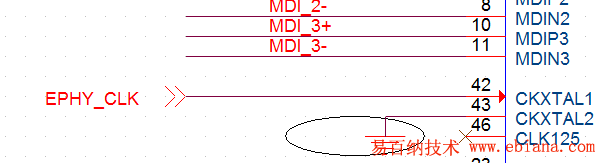

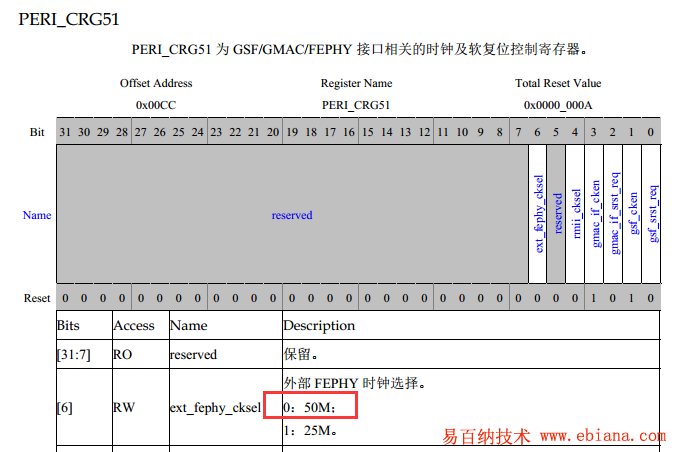

EPHY_CLK输出作为PHY时钟

本帖最后由 tgwfcc 于 2017-4-8 10:20 编辑

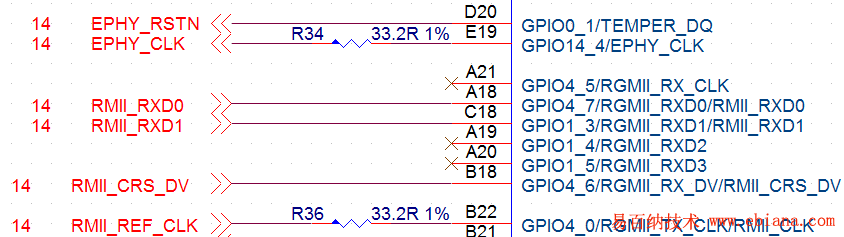

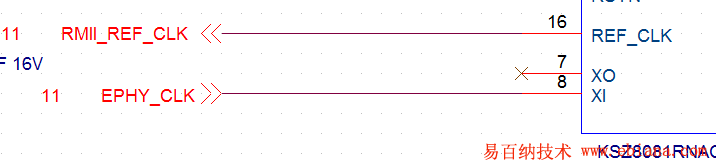

如题:做了两块板子,一块DEMO板,千兆PHY;一块百兆PHY,PHY是KSZ8081RNACA。

第一种情况:DEMO板,千兆PHY

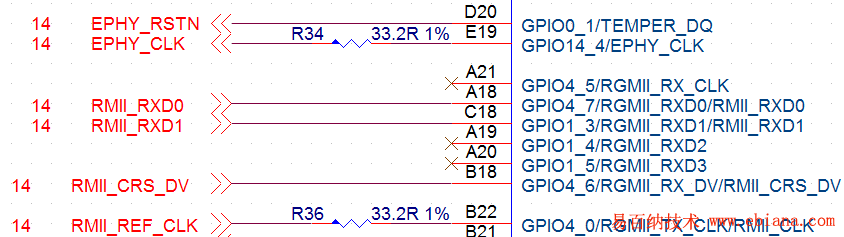

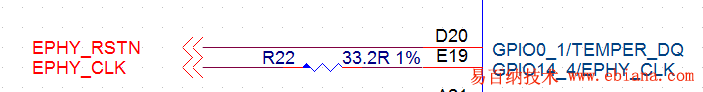

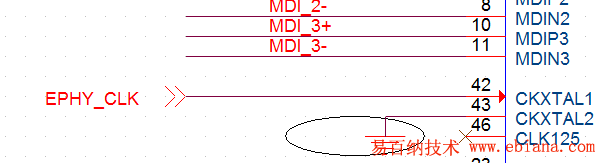

DEMO板的EPHY_CLK接PHY的时钟输入,

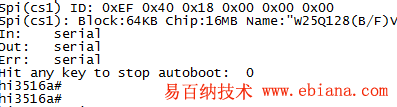

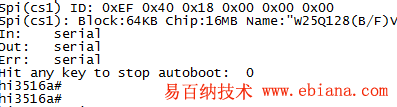

1)在SecureCRT中,启动Uboot,不启动应用程序的情况下

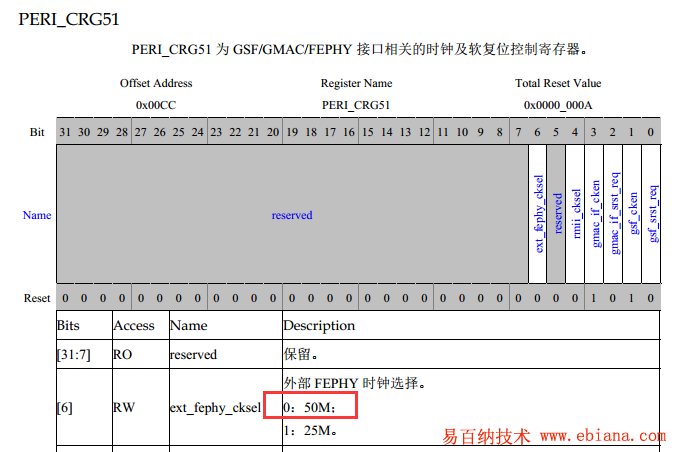

用示波器量EPHY_CLK时钟为50MHz;

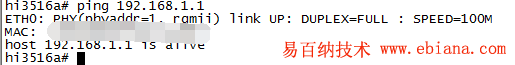

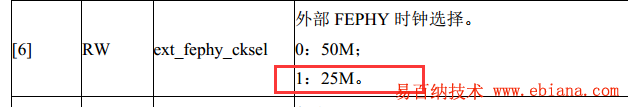

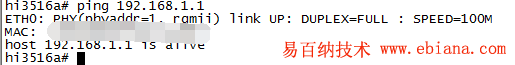

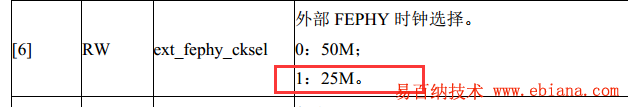

2)ping下网关192.168.1.1,可以ping通,在量EPHY_CLK时钟变为25MHz了,程序启动后可以正常获取IP地址。

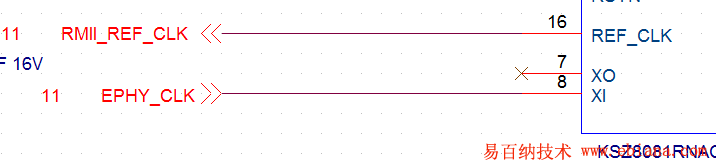

第二种情况:单内存,百兆PHY

这样接的话,软件上改下PHY地址和RMII模式,默认也是100M,

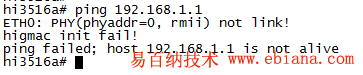

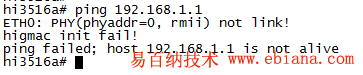

1)和第一种情况下描述的1)、2)情况一样,不同的是ping网关192.168.1.1是ping不通的。

2)在Uboot中把EPHY_CLK时钟输出改为50M后,重新烧录Uboot,启动Uboot后,不管ping不ping网关,都是50M,而且网关是可以ping通的,但是启动Kernel和filesys后,是获取不到IP的。

内核可能要改下,等软件改完在试下。。

换种接法,把CPU的RMII_CLK接到PHY的时钟输入管脚就可以了。

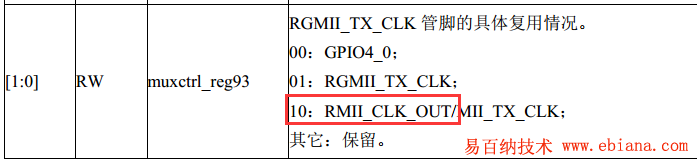

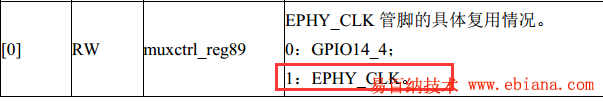

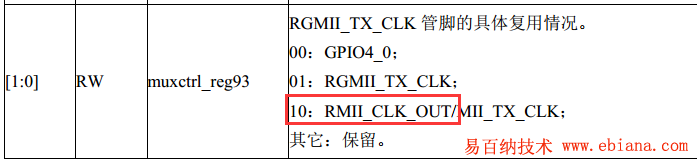

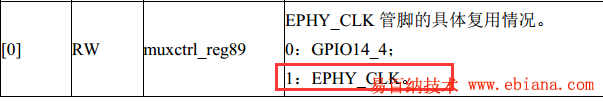

另外EPHY_CLK和RMII_CLK管脚都是复用的。

请问这是怎么回事呢?

有没有能解释的大神啊?

如题:做了两块板子,一块DEMO板,千兆PHY;一块百兆PHY,PHY是KSZ8081RNACA。

第一种情况:DEMO板,千兆PHY

DEMO板的EPHY_CLK接PHY的时钟输入,

1)在SecureCRT中,启动Uboot,不启动应用程序的情况下

用示波器量EPHY_CLK时钟为50MHz;

2)ping下网关192.168.1.1,可以ping通,在量EPHY_CLK时钟变为25MHz了,程序启动后可以正常获取IP地址。

第二种情况:单内存,百兆PHY

这样接的话,软件上改下PHY地址和RMII模式,默认也是100M,

1)和第一种情况下描述的1)、2)情况一样,不同的是ping网关192.168.1.1是ping不通的。

2)在Uboot中把EPHY_CLK时钟输出改为50M后,重新烧录Uboot,启动Uboot后,不管ping不ping网关,都是50M,而且网关是可以ping通的,但是启动Kernel和filesys后,是获取不到IP的。

内核可能要改下,等软件改完在试下。。

换种接法,把CPU的RMII_CLK接到PHY的时钟输入管脚就可以了。

另外EPHY_CLK和RMII_CLK管脚都是复用的。

请问这是怎么回事呢?

有没有能解释的大神啊?

我来回答

回答3个

时间排序

认可量排序

认可0

认可0

认可0

或将文件直接拖到这里

悬赏:

E币

网盘

* 网盘链接:

* 提取码:

悬赏:

E币

Markdown 语法

- 加粗**内容**

- 斜体*内容*

- 删除线~~内容~~

- 引用> 引用内容

- 代码`代码`

- 代码块```编程语言↵代码```

- 链接[链接标题](url)

- 无序列表- 内容

- 有序列表1. 内容

- 缩进内容

- 图片

相关问答

-

2017-04-23 12:04:22

-

2016-11-04 16:01:34

-

2017-05-06 00:34:21

-

2020-10-28 09:37:23

-

2020-02-23 15:31:58

-

2019-10-17 16:58:11

-

2022-12-15 15:14:24

-

2020-09-03 17:21:57

-

2018-06-21 11:42:33

-

2008-10-02 20:17:49

-

2018-11-30 17:18:47

-

2017-04-21 12:08:27

-

2023-01-29 09:00:24

-

2019-01-23 13:34:19

-

2016-11-03 10:55:49

-

2019-03-28 14:24:26

-

2018-04-24 08:55:22

-

2020-01-14 16:24:45

-

2019-01-12 11:04:36

无更多相似问答 去提问

点击登录

-- 积分

-- E币

提问

—

收益

—

被采纳

—

我要提问

切换马甲

上一页

下一页

悬赏问答

-

10海思3559的VGS模块在VI上画线问题

-

53519dv500接lvds的sensor mn34120,图像出现很多竖线,sensor板接以前的3519v101没问题

-

103403外接hdmi口1024*600显示屏报错

-

5SS928点DC camera的6946,全屏紫色

-

5hi3519 的 网络传输的MTU值可以修改到比1500大嘛?

-

10WS73V100星闪扫描不到设备sle

-

5SS928/SD3403 录像失败 venc stream time out, exit thread; venc 2 stream buffer is full

-

10Hi3516DV500无法运行PQTool软件

-

10君正T23+1084带TF卡插卡(给该主板适配TF卡驱动,电机驱动,适配GPIO)

-

5Hi3536A从vpss获取1080分辨率的yuv数据异常

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

提醒

你的问题还没有最佳答案,是否结题,结题后将扣除20%的悬赏金

取消

确认

提醒

你的问题还没有最佳答案,是否结题,结题后将根据回答情况扣除相应悬赏金(1回答=1E币)

取消

确认

微信扫码分享

微信扫码分享 QQ好友

QQ好友