技术专栏

降低DDR带宽的帧缓存设计

上篇文章在FPGA上关于DDR的帧缓存介绍简单讲了帧缓存的应用,这里接着讲怎么降低DDR带宽的帧缓存设计。

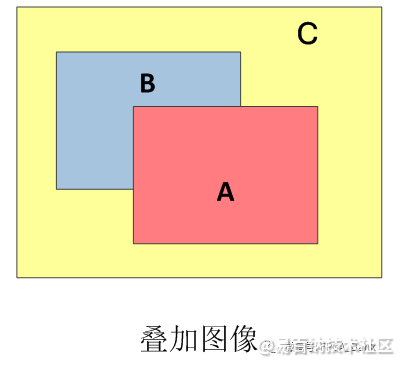

采集多个视频输入的时候,分别通过不同的frame buffer存储在不同的DDR地址里面;

在两个图层相互叠加的区域,位于下方的图层部分不写入DDR中,这样即使两个图层的帧率不同,也不会相互影响;

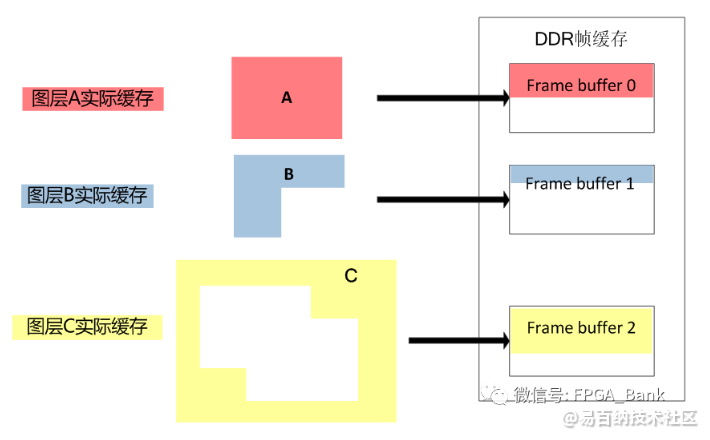

与常用的帧缓存设计接近,同样每一路均写入一个单独的frame buffer,但并不将图像整个缓存,而是只缓存实际显示的有效部分,即当存在多图层叠加的情况时,被其他图层的遮挡的重叠部分将不会被缓存到DDR中;

帧缓存结构简单,跟常规frame buffer设计一样;

读写分离,可支持各个图层输入不同帧率;

占用的DDR带宽更少,只与输出分辨率有关,与每个图层各自的分辨率及图层数量无关;

读写有效像素

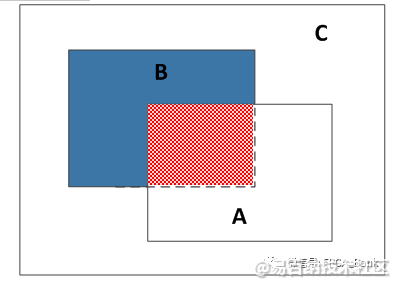

根据各个图层的层叠位置关系,提取出每个图层各自的有效像素;

实现思路:

首先计算出当前图层与其上方图层的重叠部分,将重叠部分去除后,得到当前图层的有效部分;

以下图为例,图层A为顶层,B为中间层,C为底图(底图尺寸与输出分辨率相同),对于图层B来说,蓝色部分为有效像素,红色格子部分为与A的重叠部分,需要丢弃;

降低占用的DDR带宽带来的好处

- 硬件设计阶段:节约硬件上的DDR开销,包括DDR芯片数量,引脚占用数量;

- FPGA设计阶段:降低实际使用的DDR带宽后,降低帧缓存设计消耗的RAM资源;

- 产品完善阶段:利用节约下来的DDR带宽,扩展新功能;

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:2231次2023-10-09 18:13:57

-

浏览量:7703次2021-01-30 23:18:56

-

浏览量:7195次2021-09-27 15:29:05

-

浏览量:4484次2021-11-20 15:05:18

-

浏览量:6869次2021-01-30 01:09:16

-

浏览量:6469次2020-07-17 17:27:59

-

浏览量:2909次2024-02-22 15:52:02

-

浏览量:4084次2021-08-11 17:04:30

-

浏览量:2505次2022-03-03 09:00:13

-

浏览量:3393次2020-08-10 09:24:28

-

浏览量:5388次2021-09-22 16:21:48

-

2024-01-11 15:44:19

-

浏览量:5335次2021-11-20 15:17:49

-

浏览量:3591次2021-11-20 15:15:21

-

浏览量:2978次2019-11-27 17:25:21

-

浏览量:1306次2023-12-08 17:13:21

-

浏览量:4638次2020-10-14 10:02:56

-

浏览量:3089次2018-09-05 19:19:31

-

浏览量:3257次2024-01-25 16:21:59

切换马甲

上一页

下一页

TA最新文章

打赏用户

共 0 位

我要创作

分享技术经验,可获取创作收益

分类专栏

-

24篇

热门专栏

- FPGA逻辑设计回顾(11)FPGA以及PC中的RAM与ROM

- FPGA逻辑设计回顾(3)多比特信号上升沿检测的设计方式与陷阱?

- FPGA逻辑设计回顾(8)单比特信号的CDC处理方式之Toggle同步器

- FPGA的设计艺术(21)Verilog中如何对组合逻辑进行建模?

- FPGA的设计艺术(12)使用parameter构建可重用的逻辑设计

- 在FPGA上关于DDR的帧缓存介绍

- FPGA逻辑设计回顾(13)RAM以及ROM的IP核定制以及关键参数

- FPGA逻辑设计回顾(5)多比特信号的CDC处理方式之MUX同步器

- FPGA应用于哪些行业?FPGA有什么优点?

- 高速串行总线设计基础(十二)MGT设计中物理仿真与测试测量

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

张显显

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友