技术专栏

在FPGA上关于DDR的帧缓存介绍

什么是帧缓存(frmbuf)

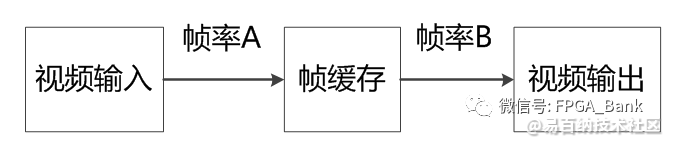

在视频处理系统中,将输入的图像以帧为单位储存到存储器(DDR)中,再根据输出时序需求,读取图像并输出,达到帧率变换、暂停显示的目的。

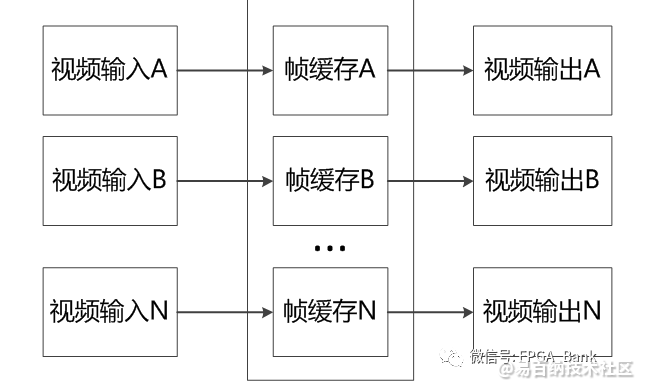

在大部分应用中,视频输入输出的数量通常都不止一组,也就是需要多个帧缓存进行视频的存储;

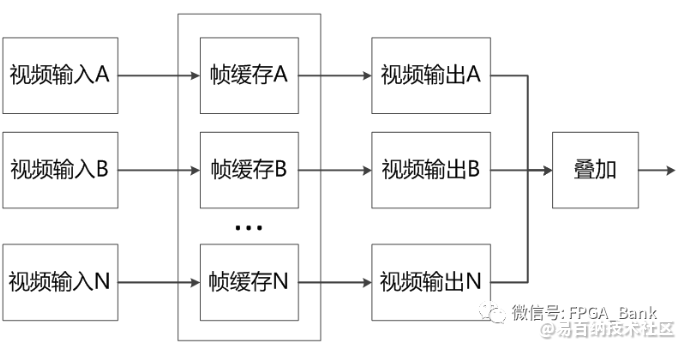

如果一个系统中存在多路视频输入,而只有一路视频输出,那么通常在帧缓存后还要将多路视频叠加在一起才可以进行输出;

常用的帧缓存设计

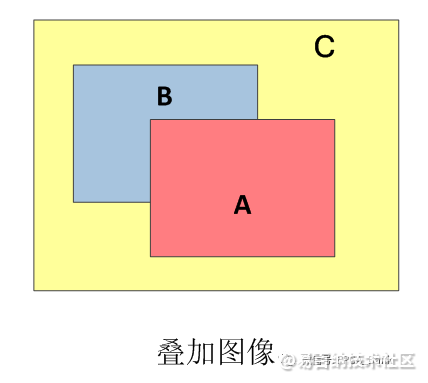

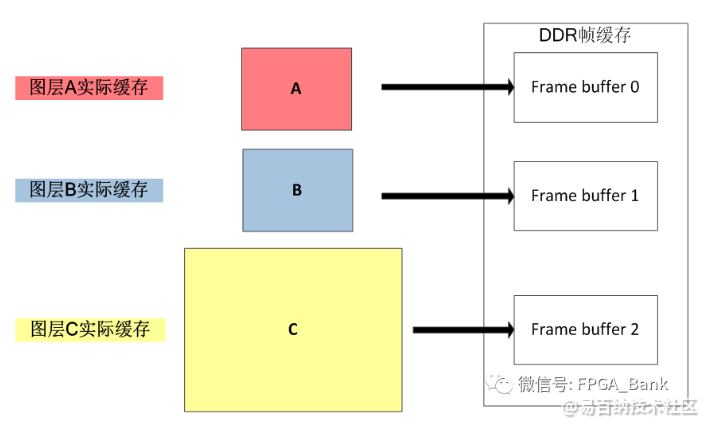

在常规的视频处理平台中,为了实现多路视频的任意叠加,会将输入到系统中的所有视频都缓存到DDR中,进行叠加时,将所有图层的完整视频从DDR读出,再根据层叠关系进行叠加;

优点:

- 操作简单

- 更改叠加位置时可以立刻响应

- 可拓展透明叠加功能

缺点:

每一个图层都缓存完整的视频,占用的DDR带宽较大,尤其 是在多图层系统中。

以FPGA实现存储4K@60输入,4K@60输出的视频为例:RGB444 24BIT像素

写有效带宽:3840*2160*24*60大约为12Gbit

读有效带宽:3840*2160*24*60大约为12Gbit

总的需要占用DDR带宽为24Gbit。

下一篇文章讲一讲关于降低DDR带宽的帧缓存设计。

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:848次2023-10-09 18:20:20

-

浏览量:7152次2021-01-30 23:18:56

-

浏览量:6568次2021-09-27 15:29:05

-

浏览量:693次2023-09-01 11:37:24

-

浏览量:8371次2020-12-14 16:47:50

-

浏览量:1037次2023-06-03 16:08:03

-

浏览量:6384次2021-01-30 01:09:16

-

浏览量:8270次2020-12-14 16:23:48

-

浏览量:1284次2023-04-21 11:15:40

-

浏览量:3950次2023-07-12 10:54:09

-

浏览量:832次2023-06-12 14:34:57

-

浏览量:3453次2022-08-16 19:12:41

-

浏览量:6105次2020-07-17 17:27:59

-

浏览量:1443次2024-01-04 17:47:00

-

浏览量:1490次2023-07-12 14:00:38

-

浏览量:6087次2022-09-19 14:17:36

-

浏览量:2100次2019-11-12 17:19:52

-

浏览量:4942次2021-09-22 16:21:48

-

浏览量:6654次2022-09-16 15:39:40

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

张显显

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友