资讯文章

新型架构可减少数字技术中噪声引起的抖动

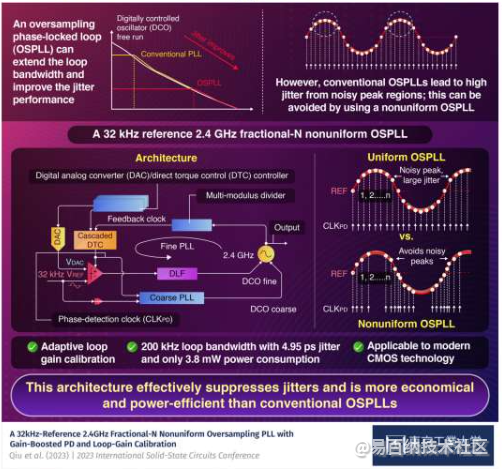

现代电子设备的效能和效率通常取决于其信号噪声和抖动。抖动是高频数字信号中信号波形的波动或偏差。有许多常规方法来减轻抖动并提高设备的性能特性。一种常见的方法是使用过采样锁相环(OSPPL)。OSPLL可以扩展环路带宽并提高抖动性能。

现在,虽然传统OSPLL具有许多优点,但由于峰值区域具有较小的梯度,因此使用传统OSPLL会导致来自噪声峰值区域的高抖动。传统32kHz信号的慢参考斜率引入了大的抖动,并导致更大的归因时间误差。

到目前为止,这一缺点阻碍了OSPLL的广泛使用。现在,东京理工学院(Tokyo Tech)的一个科学家团队已经证明了如何通过使用非均匀的OSPLL来避免这种情况。

领导研究团队的冈田健一教授,进一步解释了发展:“我们新颖的过采样架构提供了一个使用32 kHz基准的低抖动、2.4 GHz分数N PLL。根据加德纳稳定性理论,传统PLL的环路带宽理论上限制在基准频率的1/10。这种窄环路带宽会导致抖动降级。我们的非均匀过采样PLL可以将环路带宽增加60倍抑制紧张情绪。"

新构想的设备架构允许自适应环路增益校准。通过对每个采样点自动执行环路增益校准,可以最小化抖动。

“我们的设备的性能突出表现在其200 kHz环路带宽和4.95 ps的抖动。在这些参数下,该设备仅消耗3.8 mW的功率。此外,它可以与CMOS技术集成,使其成为日益增长的电子行业的一个特别有吸引力的前景,”东京理工大学的邱俊俊补充道,他是这项研究的主要作者。

由于减少了抖动和更高更干净的信号,这种范式转换架构也比传统的OSPLL更经济和更省电。

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:14764次2020-12-08 21:00:10

-

浏览量:13477次2020-12-08 20:25:24

-

2021-07-22 11:08:56

-

2020-10-14 09:40:27

-

浏览量:2596次2018-04-03 15:27:52

-

浏览量:3675次2019-11-18 11:15:10

-

浏览量:2470次2022-05-17 16:36:32

-

浏览量:2488次2018-01-20 17:01:05

-

浏览量:2282次2020-06-24 15:44:51

-

浏览量:1147次2023-08-11 15:16:04

-

浏览量:1348次2023-02-15 17:26:26

-

浏览量:5490次2021-04-12 15:49:26

-

浏览量:979次2023-12-14 15:48:49

-

浏览量:3591次2021-11-20 15:15:21

-

浏览量:2258次2020-08-03 09:56:41

-

浏览量:1696次2024-01-22 16:42:18

-

浏览量:2640次2020-06-12 09:30:51

-

浏览量:5913次2022-01-14 14:23:00

-

浏览量:1825次2020-06-05 11:53:54

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

艾

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友