FPGA零基础学习:数字通信中的电压标准

大侠好,欢迎来到FPGA技术江湖。本系列将带来FPGA的系统性学习,从最基本的数字电路基础开始,最详细操作步骤,最直白的言语描述,手把手的“傻瓜式”讲解,让电子、信息、通信类专业学生、初入职场小白及打算进阶提升的职业开发者都可以有系统性学习的机会。

系统性的掌握技术开发以及相关要求,对个人就业以及职业发展都有着潜在的帮助,希望对大家有所帮助。后续会陆续更新 Xilinx 的 Vivado、ISE 及相关操作软件的开发的相关内容,学习FPGA设计方法及设计思想的同时,实操结合各类操作软件,会让你在技术学习道路上无比的顺畅,告别技术学习小BUG卡破脑壳,告别目前忽悠性的培训诱导,真正的去学习去实战应用,这种快乐试试你就会懂的。话不多说,上货。

数字通信中的电压标准

信号存在的意义是为了能够进行信息的沟通,所以要求接收方必须能够正确的接收到信号,否则信号将没有任何存在的意义。

为了信息能够正确进行传输,发送和接收要有对信息认定的标准(发送方发送高电平,接收方要认为是高电平;发送方发送低电平,接收方要认为是低电平)。

在数字电路中,经常输入或者输出“高”、“低”电平,那么多高的电压标准算作是“高电平”呢?难道只有“0V”才算低电平?这些问题相信是任何一个初学者心中的疑虑。

我们平时所说的电压其实是电压差。例如:家用电压220V(火线)是相对于“零线”来说。

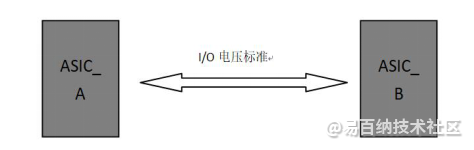

ASIC(Application Specific Integrated Circuit,专用集成电路)之间的相互通信是通过I/O发出高低电平进行通信的,这些电平都要符合相应的电平标准。

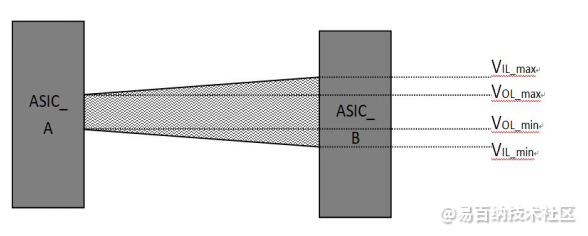

图1 :传输模型

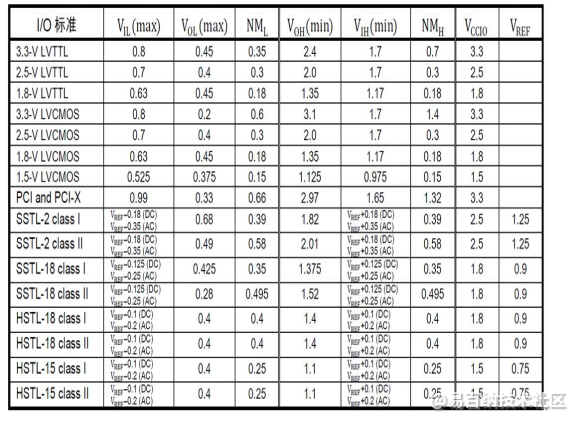

现在数字通信系统中,I/O电压标准包括早期的TTL标准,CMOS标准,LVTTL标准,LVCMOS标准,RS232,RS485标准以及HSTL(High Speed Transceiver Logic)标准和较新的LVDS(Low-Voltage Differential Signal)等标准。不同的标准支持的器件不同,支持的传输速度不同,支持的噪声容限也不同。从另一个方面来看,I/O标准的进步反映了数字系统的进步。

在实际中,各处的零电位实际上是不太相同的,将地线接在一起是为了统一零电位,以保证各处的电压,即电势差有统一的关系。

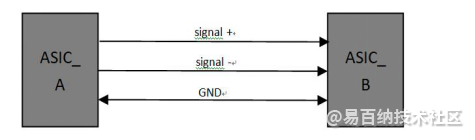

I/O端口标准按照信号的传输方式,分为单端信号(图1-8),差分信号(图1-9)和伪差分信号(图1-10、图1-11)。

图2 :单端信号传输模型

单端信号传输时,在单独的导线上传输信号,其逻辑电平相对于GND(地)。ASIC_A以相对于GND的逻辑进行驱动,接收端也用相对于地的逻辑进行捕获。LVTTL标准和LVCMOS标准都是单端信号标准。

单端信号传输一般都是短距离的传输,并且一般都是统一电源供电。中间的干扰相对较少。

LVDS,即LowVoltageDifferentialSignaling,是一种低压差分信号技术接口。它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

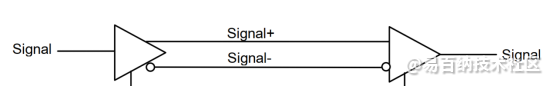

图3 :差分信号传输模型

图4 :差分信号传输连接关系

差分信号进行传输时,使用两条传输线传输信号,ASIC_A按照信号的差值进行逻辑驱动,ASIC_B也按照信号的差值进行逻辑捕获。差分信号具有很强的抗共模干扰能力,因此它的速度性能和噪声性能较好,多用于高速数据传输。LVDS标准为I/O差分标准。

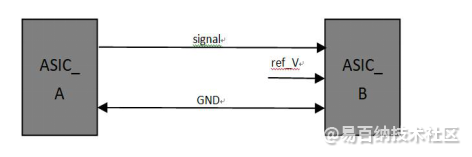

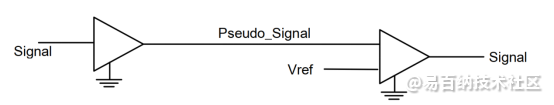

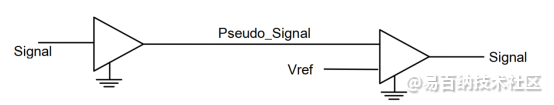

图5 :单端伪差分传输模型

图6 : 单端伪差分传输连接关系

单端伪差分信号进行传输时,使用一条传输线传输信号,ASIC_A正常发送逻辑值,ASIC_B接收是相对于ref_V(参考电压)进行接收。ref_V一般为传输电压的一半。接收端的信号电压低于ref_V当作逻辑“低”,高于ref_V当作逻辑“高”。

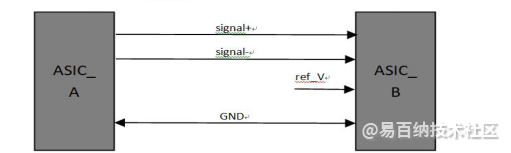

图7 :双端伪差分传输模型

图8 :双端伪差分传输连接关系

双端伪差分信号传输时,使用两条传输线分别传输信号的“正”、“反”逻辑。ASIC_A发送信号的电平与“反”电平,接收端按照单端伪差分接收标准接收,然后取出其中一路作为输出。

伪差分标准的信号输出幅度较小,电源逻辑比真差分电路简单,噪声容限大而且与JEDEC支持的SDRAM的L-Bank结构相对应,所以被应用于DDR/DDR2/DDR3接口,数据速率可以达到600Mbit/s。

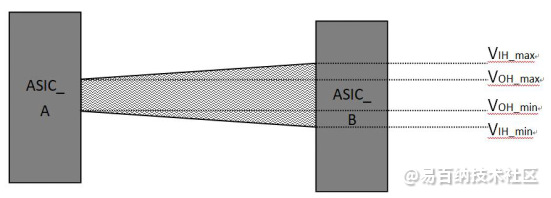

从发送端发出信号,经过线路的干扰影响,其电平可能升高或者降低,因而接收端必须在一个电平范围内判断它的逻辑值。这个电平范围称为噪声容限(Noise Margin, NM)。不同的信号传输方式和I/O标准有不同的噪声容限和逻辑值判断方式。

图9 :高电平噪声容限示意图

图10 :低电平噪声容限示意图

在单端信号传输高电平中,ASIC_A输出高电平的电压值要在VOH_max和VOH_min之间,ASIC_B为了能够正确接收到逻辑,所以要求VIH_max大于VOH_max,VIH_min小于VOH_min。而VIH_max和VOH_max都是受到电源电压的影响,并且越高肯定会判断成为逻辑高,因此VIH_min和VOH_min才是影响传输的关键。所以高电平的噪声容限(NMH)为VOH_min — VIH_min。

对于低电平而言,ASIC_A输出高电平的电压值要在VOL_max和VOL_min之间,ASIC_B为了能够正确接收到逻辑,所以要求VIL_max大于VOL_max,VIL_min小于VOL_min。而VIL_min和VOL_min都是受到GND的影响,并且越低肯定会判断成为逻辑低,因此VIL_max和VOH_max才是影响传输的关键。所以低电平的噪声容限(NML)为VIL_max — VOL_max。如果发送端和接收端不能满足以上条件,那么通信就会受到影响。

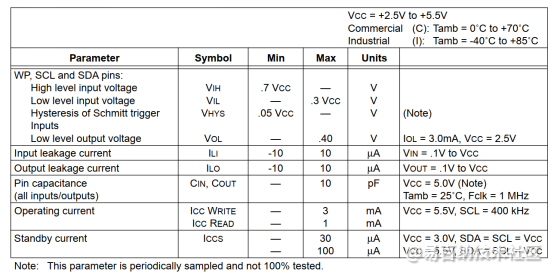

图11 :某芯片的电气标准

图12 :各类电压标准详细信息

思考:3.3V供电的单片机如何和5V供电的单片机进行通信?

1. 电平转换芯片

2. 通过上拉电阻或者三极管等

- End -

- 分享

- 举报

暂无数据

暂无数据-

浏览量:1348次2023-02-15 17:26:26

-

浏览量:1283次2023-02-13 19:34:05

-

浏览量:1180次2023-03-08 10:07:50

-

浏览量:6201次2020-11-30 10:01:37

-

浏览量:2201次2020-09-09 19:02:25

-

2020-12-14 18:16:24

-

浏览量:5582次2020-12-29 19:37:20

-

浏览量:1044次2023-09-18 15:02:26

-

浏览量:7625次2020-12-21 20:12:30

-

浏览量:6022次2020-12-21 16:50:21

-

浏览量:7287次2021-01-05 18:32:12

-

2021-01-12 21:31:51

-

浏览量:5266次2021-01-11 15:33:50

-

浏览量:4759次2021-01-08 01:04:31

-

浏览量:5617次2021-01-12 23:46:34

-

浏览量:5751次2021-01-05 22:14:42

-

浏览量:6029次2021-01-02 22:50:35

-

浏览量:6545次2020-12-29 14:13:00

-

浏览量:5224次2021-01-19 16:45:32

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

FPGA技术江湖

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友