DFT设计实战(四)

DFT设计实战(一)

DFT设计实战(二)

DFT设计实战(三)

用tmax输出scan的testbench,stil2verilog始终没有启动,怎么办?

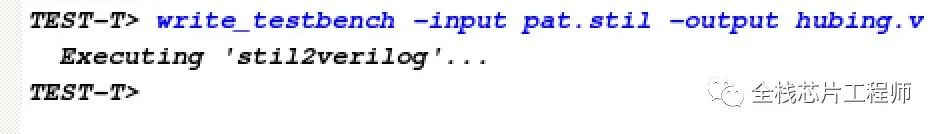

幸好对mentor的工具也熟悉,于是采用tessent软件里面的STILVerify将pa tterns转成Verilog格式的testbench:

命令:

stilverify pat.stil -VErilog tb.v

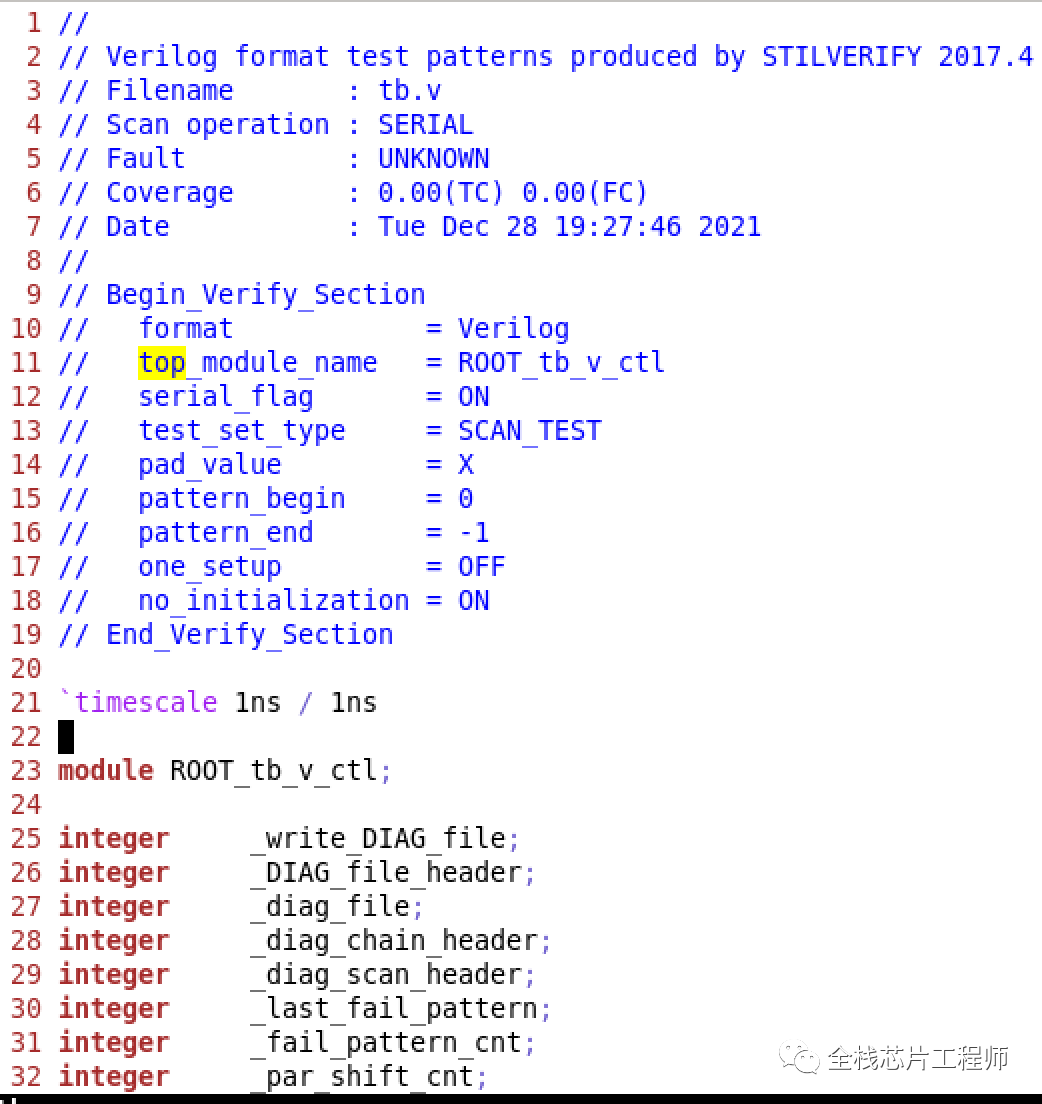

生成的testbench如下:

顶层名需要修改为设计名:

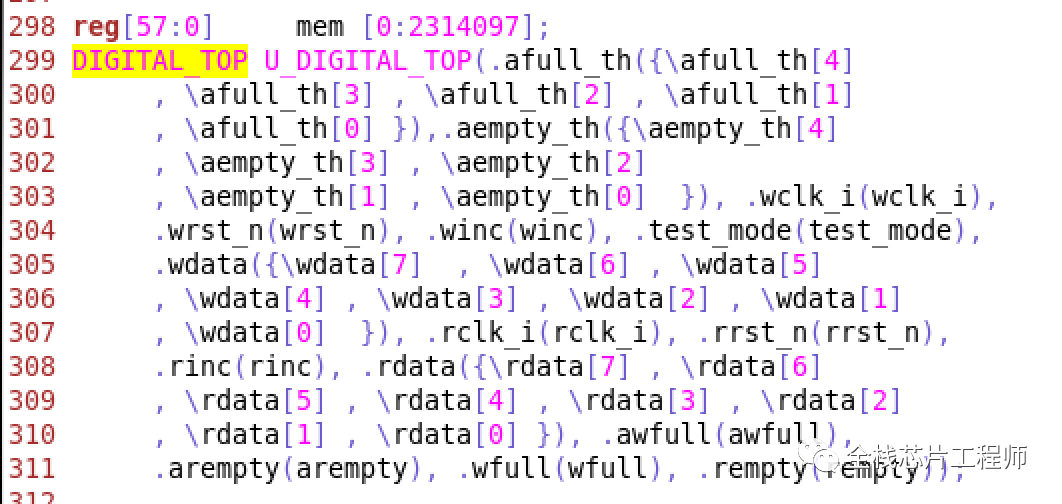

修改后如下:

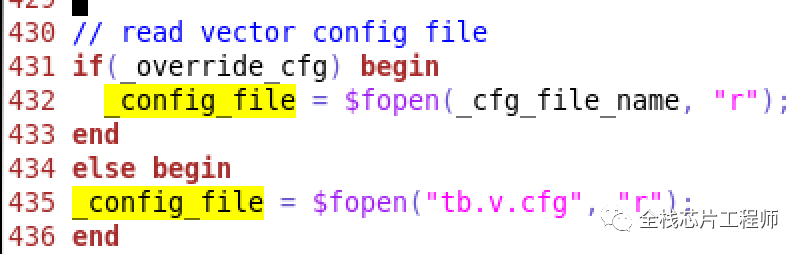

注意到顶层tb.v的激励:

顶层tb.v的配置:

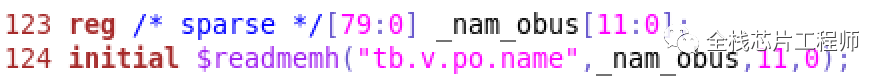

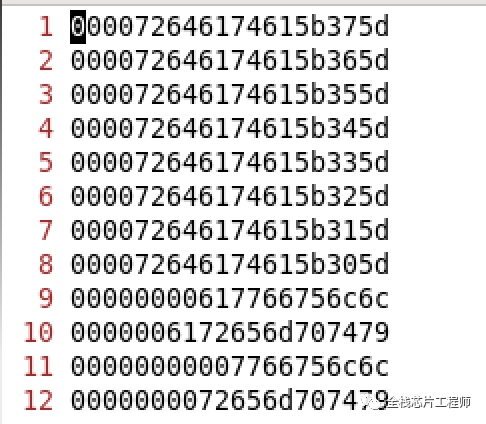

打开tb.v.po.name看看:

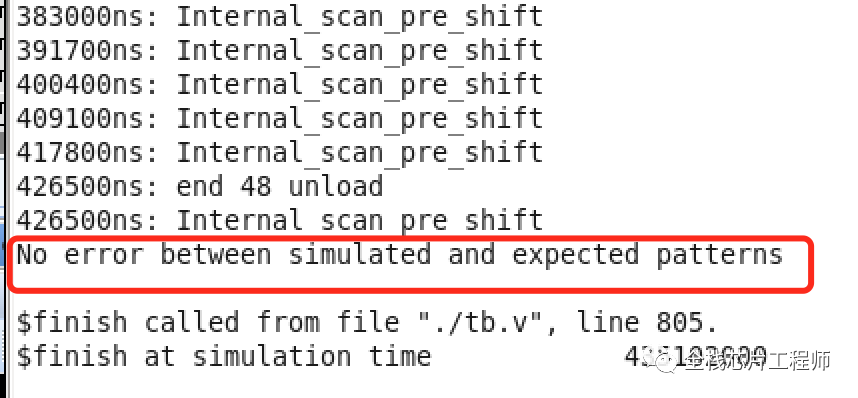

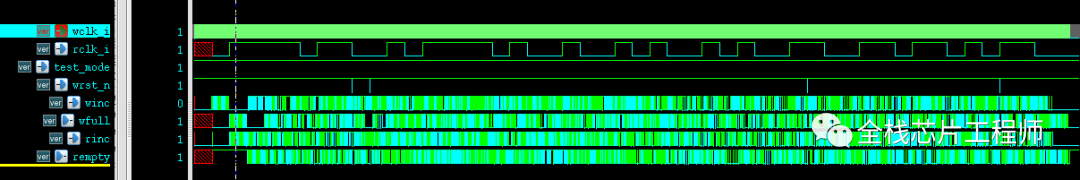

开始simulation:

欢迎加入技术交流群,先加我微信,我拉你进群!

感谢阅读,别走!点赞、关注、转发后再走吧

部分文章索引:

如何对ICG过约束:set_clock_gating_check

芯片ECO(一)

详解GDSII文件

详解SPEF文件

详解SPI协议

详解I2C协议

详解GearBox设计原理

详解set_clock_gating_style命令

【MCU】Cortex-M3 SoC的主栈指针

低功耗设计之Multi-Bit Cell

剖析数字后端site、track、pitch的概念

Verilog中,2'b1x和2’b0x造成的仿真器、综合器的mismatch!

【剖析】傅里叶变换、拉普拉斯变换、Z变换

【剖析】傅里叶变换、拉普拉斯变换、Z变换(二)

芯片设计之CDC异步电路(五)

芯片设计之CDC异步电路(四)

芯片设计之CDC异步电路(三)

芯片设计之CDC异步电路(二)

芯片设计之CDC异步电路(一)

OCV分析计算

低功耗设计之Power Switch Cell

深度剖析“异步复位、同步撤离”

芯片后仿(二)

时钟切换clk_switch

8B/10B、64B/66B编解码(一)

8B/10B、64B/66B编解码(二)

剖析FPGA怎么实现“超前进位加法器”(一)

剖析FPGA怎么实现“超前进位加法器”(二)

FPGA原型验证-时钟门控的替换

行波进位/超前进位加法器详解

AES加密算法(一)

Cadence Voltus-功耗分析&IR-drop(一)

Cadence Voltus-功耗分析&IR-Drop(二)

Cadence Voltus-功耗分析&IR-drop(三)

Cadence Voltus-功耗分析&IR-drop(四)

本文转载自公众号全栈芯片工程师,版权归原作者所有,不代表本站观点,如有侵权请与本站联系,本站将第一时间删除

- 分享

- 举报

暂无数据

暂无数据-

浏览量:7032次2022-03-26 09:00:12

-

浏览量:6570次2022-05-10 09:00:38

-

浏览量:2371次2023-04-19 09:15:27

-

浏览量:1615次2023-04-19 09:13:50

-

浏览量:3151次2023-04-19 09:15:44

-

浏览量:3853次2022-03-01 09:00:10

-

浏览量:4619次2022-02-22 09:00:14

-

浏览量:24058次2021-01-29 16:50:41

-

浏览量:3074次2023-04-19 09:16:00

-

浏览量:19827次2020-12-07 00:56:53

-

浏览量:9762次2020-12-18 22:21:10

-

浏览量:6399次2021-02-21 21:08:27

-

浏览量:6715次2021-02-21 16:01:28

-

浏览量:7522次2020-08-15 17:22:26

-

浏览量:3348次2020-11-28 22:33:06

-

浏览量:10522次2021-02-20 22:37:06

-

浏览量:3267次2019-11-19 14:40:18

-

浏览量:6582次2021-04-06 20:09:36

-

浏览量:7608次2021-02-21 01:20:21

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

转国产芯的酱油

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友