HI3518EV300电源设计参考

HI3518EV300电源设计参考

1.CORE电源设参考

(1)Hi3518EV300 的 CORE 电源 VDD,典型电压 0.9V,具体输出电压由 SVB 电路控制。

(2)电源芯片选型要求其供电能力不小于 1A,要求使用非轻载高效器件。电感感值不低于1uH,饱和电流建议不低于1.5A。

(3)纹波噪声要求约束在 Vpp 70mv 以内。

2.DDR电源设计参考

(1)Hi3518EV300 内置 DDR2,典型 IO 电压 1.8V。

(2)DDR PLL 电源(管脚名 AVDD33_DDR_PLL):连接 3.3V 电源。必须使用磁珠(1kΩ@100MHz)和主芯片的数字 3.3V 电源进行隔离,纹波噪声要求约束在Vpp 80mv 以内,要求不能有固定频点噪声。

(3)电源器件选型,要求使用非轻载高效器件。

3.IO电源设计参考

(1)IO 电源连接数字 3.3V/1.8V 电源。

(2)Sensor 时钟、复位和配置管脚 IO 电源支持3.3V/1.8V 电源,实际连接的电源要与对接芯片的接口电平保持一致。

(3)MIPI/LVDS 接口电源支持 3.3V/1.8V 电源。

Hi3518EV300 的 MIPI/LVDS 管脚可以复用成 Parallel Data 功能,电平支持3.3V/1.8V,实际连接的电源要与对接芯片的接口电平保持一致。

(4)LCD 接口电源(管脚名 DVDD3318_VIVO):支持 3.3V/1.8V 电源。

(5)纹波噪声要求约束在 Vpp 80mv 以内,建议使用非轻载高效器件。

4.PLL电源设计参考

Hi3518EV300 的 PLL 电源有 2 个,分别是:AVDD_PLL和AVDD33_PLL,设计要求有:

(1)AVDD_PLL:设计上必须用磁珠(1kΩ@100MHz)对 DVDD 电源进行隔离。

(2)AVDD33_PLL:设计上必须用磁珠(1kΩ@100MHz)对数字 3.3V 电源进行隔离。

(3)AVDD_PLL 纹波噪声要求约束在 Vpp 70mv 以内。

(4)AVDD33_PLL 纹波噪声要求约束在 Vpp 70mv 以内。

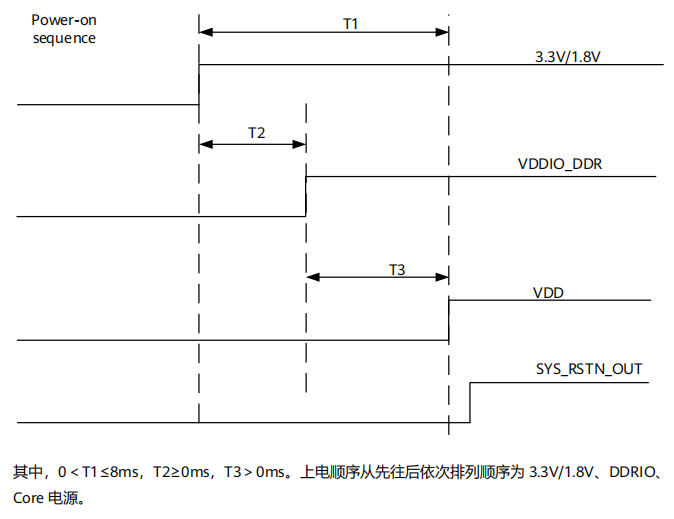

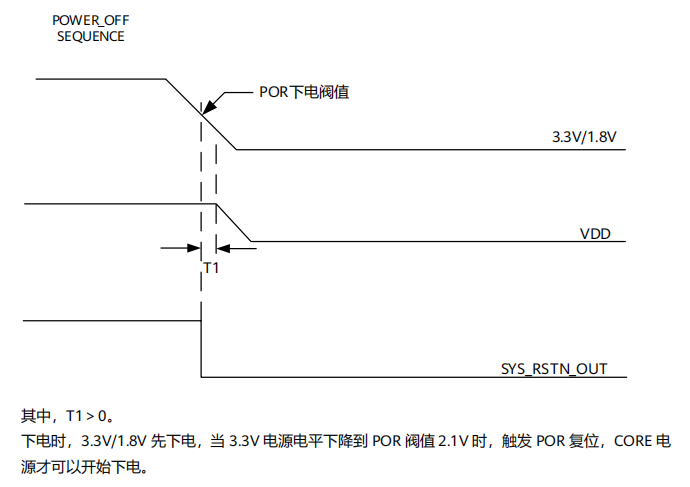

5.上下电时序要求

Core 电源、DDR 电源和 IO 电源有上下电时序的要求,如图所示:

(1)上电时序

(2)下电时序

- 分享

- 举报

暂无数据

暂无数据-

浏览量:11939次2022-06-10 21:26:04

-

浏览量:12487次2022-06-10 21:31:53

-

浏览量:1533次2023-11-08 18:12:13

-

2020-08-03 19:07:53

-

浏览量:10770次2020-09-06 23:18:26

-

浏览量:2882次2019-11-05 20:18:39

-

浏览量:3759次2022-01-31 09:00:24

-

2018-06-18 22:47:22

-

浏览量:3521次2022-05-20 10:31:05

-

2021-07-13 14:13:08

-

浏览量:3948次2020-12-03 13:59:05

-

浏览量:2438次2020-06-23 18:07:57

-

浏览量:6591次2022-06-08 21:18:55

-

浏览量:1286次2023-06-12 14:35:25

-

浏览量:5968次2021-09-24 13:45:50

-

2019-04-10 21:45:38

-

浏览量:1829次2023-06-12 14:35:30

-

浏览量:3422次2019-02-14 17:57:04

-

浏览量:725次2023-12-11 11:42:02

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

杨大大

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友