【转载】Display Port概述以及应用

1、Display Port 概述

DisplayPort是由美国视频电子协会(VESA:Video Electronics Standards Association)在2006年5月提出的一种新型的数字显示接口规范,主要用于在源端Source和设备端Sink(如电脑显示器)之间传输视频、音频、USB以及其它格式的数据信息。DisplayPort规范采用免费授权方式,旨在取代VGA、DVI和LVDS,提供高性能的视频传输通道。用户可以通过使用适配器兼容目前的VGA/DVI显示设备。

DisplayPort包括三个独立相关的标准:外围DisplayPort(external DisplayPort interface)标准和两个内部(internal interfaces)DisplayPort标准:embedded DisplayPort (eDP)。2010年起,在移动PC和PC显示器市场,external DisplayPort interface取得了一些进展。eDP主要用于移动和嵌入式设备。

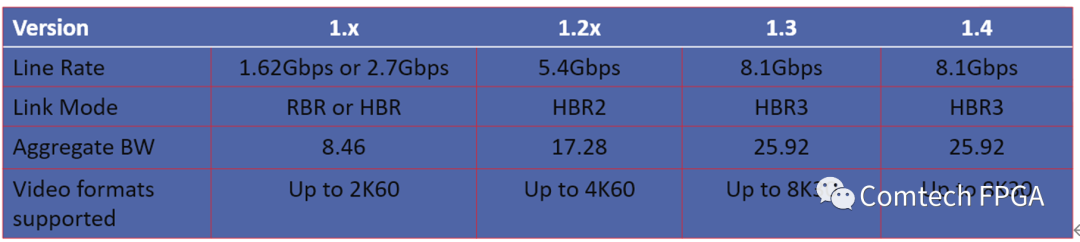

DisplayPort是首个采用微封包数据传输(Micro-Packet Architecture,Ethernet/USB/PCI Express均采用该数据传输)的显示接口标准,支持内部和外部显示连接,不同于其它基于差分对标准有单独的时钟信号,DisplayPort采用的微封包将时钟信号嵌入在数据包中。DisplayPort可以用较少的Pin传输更大的数据量,支持高分辨率显示输出。同时,微封包的数据传输可以在不改变接口的情况下,提供更好的可扩展性能。DisplayPort可同时传输音频和视频,也可以单独传输音频或者视频。视频信号路径中每个颜色通道支持6位,8位, 12位,16位,音频路径可以有多达8通道24位48 kHz的非压缩的PCM音频,或可以在音频流中封装压缩的音频格式。一个双向的、半双工的辅助通道携带了主链接用的设备管理和设备控制数据,如VESAEDID、MCCS和DPMS标准。DisplayPort信号不兼容DVI或HDMI。然而,双模式DisplayPort被设计用来通过该通信端口传输单链接DVI或HDMI1.2/1.4的协议,需要通过使用一个外部无源连接器来实现,选择所需的信号,并将电气信号从LVDS转换为TMDS。DisplayPort连接器在主链路可以有1、2、或4路差分数据对(通道),每通道可以在自定时器运行于162、270、或540MHz的基础上其原始码率为1.62、2.7或者5.4 Gbit/s。数据为8b/10b编码,即每8位的消息被编入10比特符号中。因此,解码后每通道的有效数据传输速率是1.296、2.16、4.32 Gbit/s(有效带宽80%)。

Display Port图像显示接口,不仅支持全高清 (1920×1080) 分辨率,还能支持4k分辨率(3840×2160),以及最新的8k分辨率(7680×4320)。

Display Port图像显示接口不仅传输率高,而且可靠稳定,其接口传输的信号由传输图像的数据通道信号以及传输图像相关的状态、控制信息的辅助通道信号组成,具体包含DisplayPort数据传输主要通道(Main Link)、辅助通道(AUX Channel)与连接(Link Training)。

2、Display Port接口信号

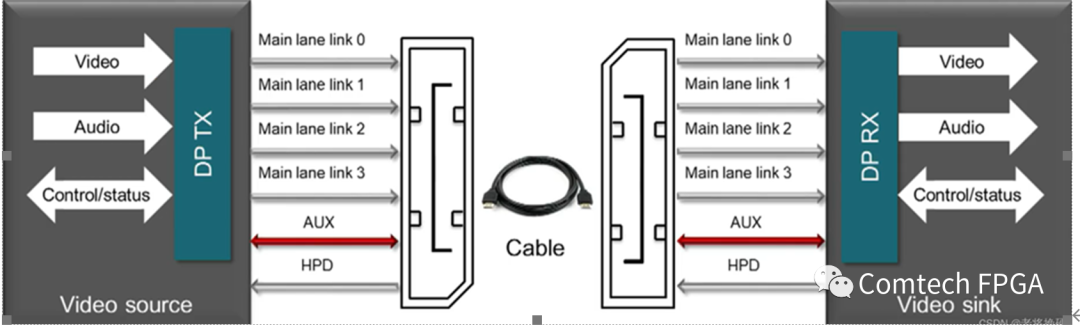

DisplayPort由三部分组成,分别为主链路、辅助信道和热插拔信号检测(HPD)。

主链路(Main Lane):主链路是单向、高带宽、低延迟信道,用于传输同步串行数据流,如未压缩的视频和音频。主链路由4条线路(Lane)组成,每一条线路都是一对差分线。根据实际需要,DisplayPort可以分别使用1、2或4条线路。每一条线路都支持多种传输速率:1.62Gbps、2.7Gbps、5.4Gbps或8.1Gbps,4条线路则可以实现最高32.4Gbps的传输速率。在这种高带宽的支持下,DisplayPort可以满足各种多媒体、特别是视频应用的需求。任何色深、分辨率和画面刷新频率都可以自由转换。每一条线路都是数据线,这意味着DisplayPort没有单独的时钟通道。实际上,DisplayPort在主链路上采用的是ANXI 8B/10B编码,时钟信号是从数据串流中提取出来。这个有别于DVI和HDMI的特点,大幅降低了DisplayPort产品EMI设计难度。同时,由于DisplayPort传输线路采用交流耦合,发送端和接收端有不同的共模电压,这使芯片可以拥有更小的特征尺寸,也方便DisplayPort与其它新兴高速数字接口(如TYPE-C)连接、耦合,兼容。

辅助通道(AUX CH):辅助通道是由一对交流耦合差分线组成的双向、半双工通道,用于传输小带宽需求的数据,链路管理和设备控制。其中,源端设备为主、终端设备为从。所有通讯都必须由源端设备发起,终端设备也可以透过热插入信号来提出通讯请求。辅助通道是1Mbit/s半双工,双向通道,用于链路管理(状态信息)和设备控制。同时对传输延迟做了严格要求:通讯必须在500us内完成。辅助通道AUX(Auxiliary)的用途包括读取扩展显示识别数据(EDID),以确保DP信号的正确传输;读取显示器所支持的DP接口的信息,如主要通道的数量和DP信号的传输速率;进行各种显示组态寄存器的设定;读取显示器状态寄存器。接收(sink)设备可以切换HPD信号来提示源设备启动一个AUX请求事务来读取DPCD链接/接收状态寄存器位,包括IRQ_HPD向量寄存器位。只有先保证AUX的信号正确才能使DP接口信号正确传输,而不同DP协议的液晶模组对AUX输出信号的幅值有不同的要求。目前,在液晶模组检测设备对液晶模组进行检测时,针对不同DP协议的液晶模组,需要设计各种AUX输出幅值相匹配的液晶模组测试装置,明显提高了液晶模组的测试成本。

热插拔信号检测(HPD):HPD信号是一条sink to source单向通道,用于检测上层设备和下层设备是否连接,进而实现线路的连接和中断。一、用作sink检测,接3.3V或拉高说明sink存在,拉低超过2ms说明sink不存在;二、作为sink设备的中断请求,当拉低0.5ms~1ms时,说明sink设备发出中断,此时source通过AUX读取sink的DPCD寄存器获知中断类型。

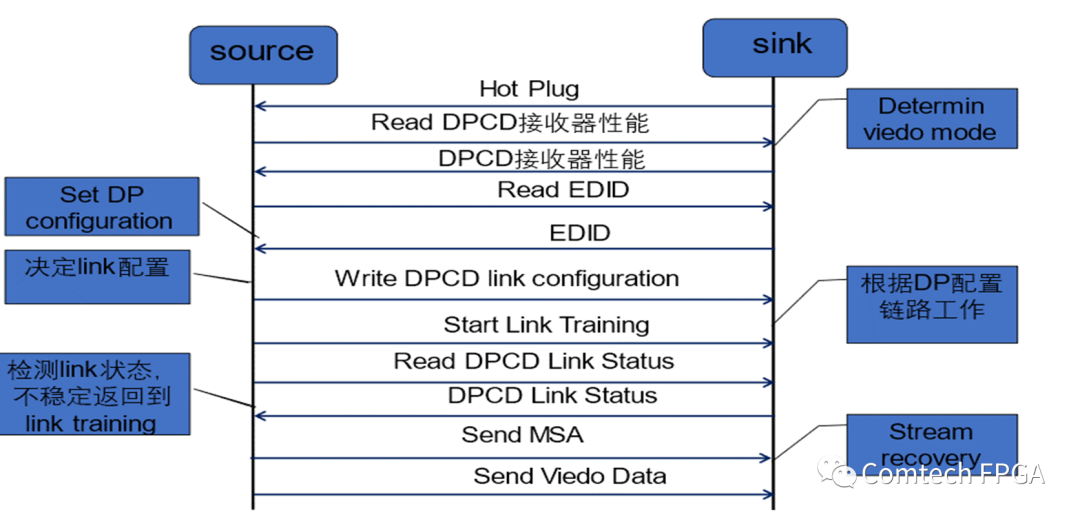

3、Display Port 数据传输前流程

DP source和sink之间的信息传送通过对sink上的DisplayPort配置数据(DPCD)寄存器进行读写来实现。通过读取DPCD中的特定寄存器,source将知晓sink的性能。在建立数据link,即link训练期间,source对DPCD进行写操作,以指明目标link的配置,另外sink也将各个link训练阶段的结果写到此处。在数十个DPCD寄存器中调用每个位的详细含义非常具有挑战性。因此,对于DP调试程序的生产率来说重要的是,所用工具能够轻松地根据VESA DP技术规范等标准的常用术语解析AUX读写操作中的DPCD内容。

扩展显示标识数据(EDID)是一个结构化数据块,定义了DP接收装置的性能。它定义了构造、型号名称、屏幕尺寸和颜色格式。在连接到sink之后,source首先要执行的操作之一就是读取sink的EDID数据。对DP source和sink之间的通信起到重要作用的是EDID定义了sink以及sink支持的视频模式的原始分辨率。在选择将要发送给sink的内容的格式时,该数据是source的基础。分辨率、所用视频模式、颜色格式、音频格式等。通过改变测试sink的EDID,工程师可以轻松验证sink的灵活性。易于使用的EDID编辑器可向用户说明各个比特位,是另外一种非常重要且节省时间的工具。

根据source需要发送给sink的内容以及从EDID和DPCD读取来的sink性能,source可确定发送内容的格式以及用于传输的数据link配置。一个良好设计的source将尝试优化link的使用,以达到将功耗降至最低等目的。因此其目标是使用尽可能少的信道和尽可能低的电压摆动。在link训练期间,source使用其首选配置启动实际训练过程,在link建立之前通过迭代法对其进行改变。一旦link建立,source便可开始发送内容本身。用户可以在AUX Channel Monitor的帮助下评估通信记录,进而验证link培训过程是如何执行的。此外,工具的易用性将有助于工程师保持注意力集中。因为一对具有多流功能的source和sink之间的link训练过程可包含上百个读写操作,诸如突出显示数据以便于阅读、过滤数据以专注于基础数据等功能至关重要。通过改变sink或source的性能因素,工程师可以验证其DUT sink或DUT source是否按预期工作。VESA定义的Link Compliance Test中的各种测试事实上可验证sink或source是否按实现良好互操作性所需的方式进行工作。一个良好的工具允许编辑和保存性能数据,供以后使用。

4、AMD Xilinx Display Port 接口方案

使用Xilinx DisplayPort 解决方案有两种方式:

1、在FPGA或者SOC的PL端调用DisplayPort TX 和RX 子系统的IP core,它们是完全符合VESA DisplayPort V1.2和V1.4的规范要求;

2、MPSOC的PS端集成符合VESA DisplayPort V1.2a标准的硬核DP接口,可以达到4K@30的显示能力,使用它可以减小FPGA资源的消耗。

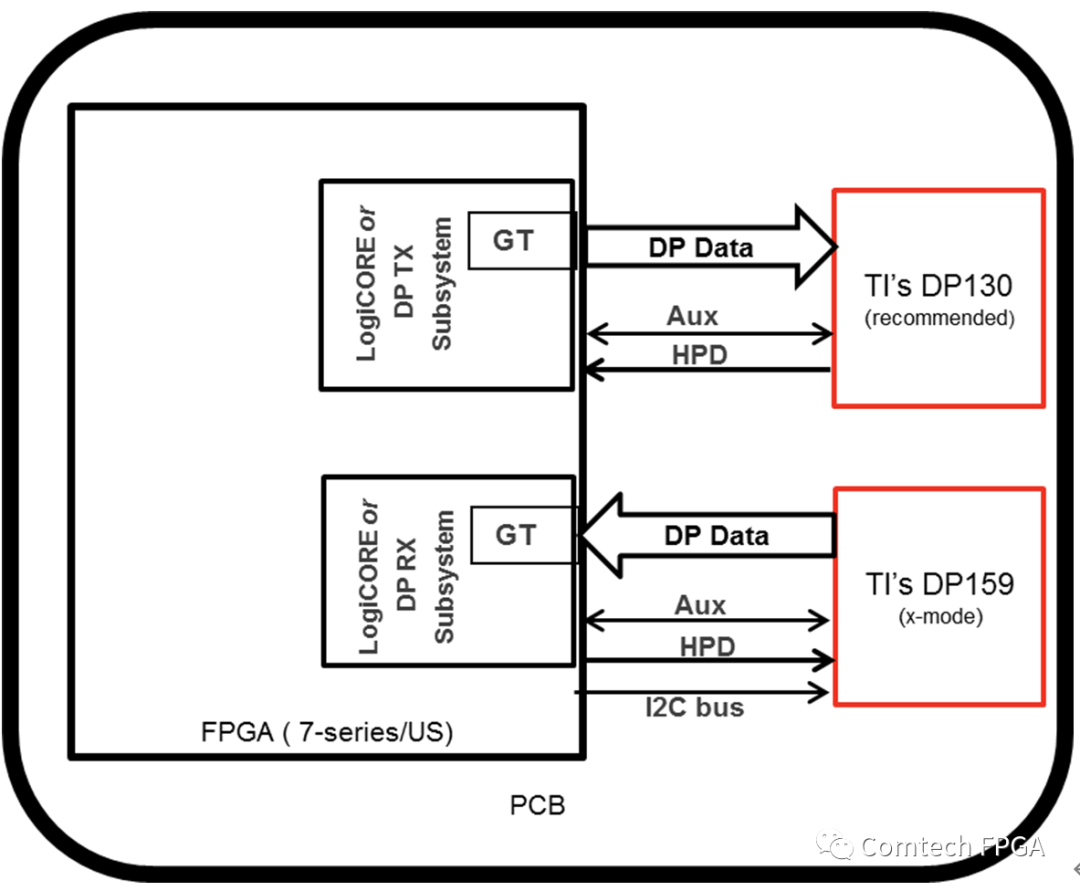

5、AMD Xilinx Display Port硬件设计

下面以Display Port 1.2为例子简介硬件设计要求。DP信号是一个交流耦合、100欧姆的差分信号接口。交流耦合电容必须添加,推荐封装0402;共模电感的选择要注意其是否支持足够高的数据速率;ESD尽量选择寄生电容小的器件。

Xilinx Display Port1.2 TX IP需要外加SN75DP130,SN75DP130器件是一款单通道 DisplayPort™ (DP) 转接驱动器,可重新生成 DP 高速数字链路。该器件符合 VESA DisplayPort 标准版本 1.2,支持 4 通道主链路接口,允许每个通道以 5.4Gbps 的 HBR2 速率发送信号。器件会补偿 PCB 相关频率损耗和开关相关损耗,以在源设备和接收设备之间提供最佳 DP 电气性能。主链路信号输入具有可配置均衡器和可选升压设置。主链路输出提供四种初级差分输出电压摆幅 (VOD) 和四种初级预加强设置。

Xilinx Display Port1.2 RX IP需要外加SN65DP159 (RGZ package),该器件为确保信号完整性, SNx5DP159 器件实现了多个特性。 SNx5DP159 接收器支持自适应和固定均衡,以便消除电路板走线或电缆因带宽受限而引起的码间串扰(ISI) 抖动或损耗。用作重定时器时,内置的时钟数据恢复 (CDR) 功能可清除输入端高频和视频源的随机抖动。发送器提供多种功能不仅有利于达到合规要求,还能够减少系统设计问题,例如去加重功能可补偿驱动长电缆或高损耗电路板走线时的衰减。 SNx5DP159 器件还包含使用 Vsadj 引脚上的外部电阻器实现的TMDS输出幅值调节功能,以及源端选择功能和输出转换速率控制功能。器件的运行和配置可通过引脚设置或 I2C编程。

附:相关参考文档

1、Display port RX\TX手册:PG299和PG300;

2、MPSOC PS Display Port接口手册:UG1085

3、Display Port的linux驱动代码:

如果有任何技术问题,欢迎您联系科通各地的AMD赛灵思支持团队,或发邮件至:

simonyang@comtech.com.cn

charlesxu@comtech.com.cn

- 分享

- 举报

暂无数据

暂无数据-

浏览量:3366次2020-02-17 19:21:02

-

浏览量:2069次2019-12-13 18:21:20

-

浏览量:3852次2022-06-08 14:16:22

-

2020-10-17 18:27:28

-

浏览量:3355次2020-11-10 14:23:32

-

浏览量:2594次2022-01-08 09:00:12

-

浏览量:3411次2020-08-04 20:10:32

-

浏览量:3993次2021-04-23 10:35:16

-

浏览量:4599次2020-10-21 15:44:26

-

2025-04-11 11:48:23

-

浏览量:3687次2020-08-17 18:05:11

-

浏览量:838次2023-06-03 15:58:33

-

浏览量:6356次2021-03-02 02:30:33

-

浏览量:2146次2018-01-05 15:15:02

-

浏览量:8734次2021-02-06 22:29:19

-

浏览量:2889次2020-08-05 20:49:45

-

浏览量:1934次2023-09-01 13:29:58

-

浏览量:6448次2021-07-26 17:43:04

-

浏览量:3053次2022-04-29 16:36:53

- 再度亮相进博会,Xilinx 高度关注中国开发者

- 收官!您想要的演讲回放都在这里

- 高光时刻: Xilinx 自适应计算平台 和 Vitis 登上世界互联网领奖台

- 高速串行总线设计基础(十二)MGT设计中物理仿真与测试测量

- XDF(亚洲站)6 折门票,限时抢购

- FPGA的设计艺术(8)最佳的FPGA开发实践之过程

- FPGA的设计艺术(15)逻辑设计及仿真利器之各式各样的循环

- Xilinx、Spline.AI、AWS 推出 X 射线分型深度学习模型和参考设计

- FPGA逻辑设计回顾(4)亚稳态与单比特脉冲信号的CDC处理问题

- FPGA的设计艺术(18)如何使用Verilog中的数组对存储器进行建模?

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

四叶草~

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友