为香山处理器“雁栖湖”设计一个DFT方案

“ 何志恒老师是鹏城实验室开源芯片院士工作室的DFT负责人,本篇文章转发自他的知乎账号“恒芯荣耀”。这是香山后端团队的工作之一,后续团队将开设物理实现的专栏,以支撑与完善香山的开源社区。欢迎关注!”

前言

“香山”是一款开源高性能RISC-V处理器,其微结构设计第一版代号为“雁栖湖”,具有11级流水线,性能评估SPEC CPU2006分数达到7分/GHz;香山的第二版代号为南湖,主要改动包括①新的前端取值与分支预测设计;②优化的后端执行流水线;③新的non-inclusive L2/L3 Cache;④使用双核完成流片。初步性能评估结果显示,南湖能够在2GHz主频下达到SPECint 2006 18分,SPECfp 2006 20分的成绩。香山处理器第一版(雁栖湖)已于2021年7月在28nm工艺节点下完成流片,在2022年1月回片,经过了一系列、跨春节的调试攻关,目前的调试目标已达成!香山性能优化后,在CPU 1GHz+DDR4-1600配置下:SPECint 2006 7.02分,SPECfp 2006 6.94分,与预期性能评估高度一致! 图1 雁栖湖的RTL-sim、FPGA、AISC实测及南湖RTL-sim的性能评估对比香山处理器第二版(南湖)将在14nm工艺节点下完成流片;基于南湖微结构的香山处理器在整体SOC加入了DFT规格。我们必须在芯片的开发阶段就考虑可测试性的问题,这就是DFT(Design for Test)问题。测试是通过控制和观察电路中的信号,确定电路是否正常工作的过程。可测试性设计技术的目的就是试图增加电路节点的可控制性和可观测性,从而有效地、经济地完成芯片的生产测试。可测性设计(DFT)给整个测试领域开拓了一条切实可行的途径,目前国际上大中型IC设计公司基本上都采用了可测性设计的设计流程,DFT已经成为芯片设计的关键环节。在先进工艺下,芯片良率问题愈发突出;DFT除了服务于生产测试外,其灵活强大的诊断能力为芯片功能调试、芯片良率提升提供强有力的支撑!香山处理器横空出世之后,在学界、业界、国内外备受关注,许多开发者希望集成雁栖湖/南湖做出自己的soc,或者对微结构进行二次开发;并且不少开发者设计出来的芯片定位量产。香山处理器旨在打通从芯片设计到芯片生产测试过程中每一个环节的设计流程,让开源芯片生态中的芯片都具备切实可行的生产测试能力。本文整理出“雁栖湖”的DFT设计范例,包括了生产测试规格、DFT设计规格、DFT设计数据及测试时间评估,给各大开发者作一个参考。雁栖湖DFT设计范例

图1 雁栖湖的RTL-sim、FPGA、AISC实测及南湖RTL-sim的性能评估对比香山处理器第二版(南湖)将在14nm工艺节点下完成流片;基于南湖微结构的香山处理器在整体SOC加入了DFT规格。我们必须在芯片的开发阶段就考虑可测试性的问题,这就是DFT(Design for Test)问题。测试是通过控制和观察电路中的信号,确定电路是否正常工作的过程。可测试性设计技术的目的就是试图增加电路节点的可控制性和可观测性,从而有效地、经济地完成芯片的生产测试。可测性设计(DFT)给整个测试领域开拓了一条切实可行的途径,目前国际上大中型IC设计公司基本上都采用了可测性设计的设计流程,DFT已经成为芯片设计的关键环节。在先进工艺下,芯片良率问题愈发突出;DFT除了服务于生产测试外,其灵活强大的诊断能力为芯片功能调试、芯片良率提升提供强有力的支撑!香山处理器横空出世之后,在学界、业界、国内外备受关注,许多开发者希望集成雁栖湖/南湖做出自己的soc,或者对微结构进行二次开发;并且不少开发者设计出来的芯片定位量产。香山处理器旨在打通从芯片设计到芯片生产测试过程中每一个环节的设计流程,让开源芯片生态中的芯片都具备切实可行的生产测试能力。本文整理出“雁栖湖”的DFT设计范例,包括了生产测试规格、DFT设计规格、DFT设计数据及测试时间评估,给各大开发者作一个参考。雁栖湖DFT设计范例

“雁栖湖”是一个开源的soft IP,综合策略、DFT设计、物理实现均可以根据开发者的需求及实际情况进行,利用EDA工具链(开源或者商业)完成相关设计。给出“雁栖湖”DFT设计范例旨在给开发者一个参考,另外DFT设计质量受功能设计影响,因此DFT设计范例当中给出的DFT设计数据也是各位开发者所关心的。以下所提到的DFT设计规格均是范例中的设计规格,并不是“雁栖湖”代码release的既有规格;以下文中提到的设计范例代指“雁栖湖”DFT设计范例。### 生产测试规格(建议)

“雁栖湖”是纯数字电路,由时序逻辑、组合逻辑、Memory组成;设计范例考虑常规soc芯片所需要的生产测试规格,若芯片有更高的测试要求(如车规芯片),可自行增加测试规格及对应的电路开发。Test item/FeatureSpecificationMemory

MBIST Go/No-GoYES(coverage 100%)MBIST算法soft programYESMemory诊断YESMemory RetentionTestYESMemory RepairNO板级Mbist测试YESLogic

Scan Chain TestYES(coverage 100%)Stuck-At TestYES(coverage >99.5%)Transition TestYES(coverage >90%)IDDQ TestYES(coverage >80%)Bridge TestSupport When NeededPath Delay TestSupport When NeededSmall Delay TestSupport When NeededN-Detect TestSupport When NeededLPCT(Low Pin Count Test)NOLBISTNO### DFT设计规格(建议)

在现代化的DFT设计当中,DFT电路已经形成结构化,可以通过EDA工具快速对design插入DFT电路;结合生产测试规格,设计范例中包含的结构化DFT电路如表所示:Structured DFTSpecificationMBISTMemory的内建自测试,一种高效的Memory测试电路OCC时钟控制电路,用于测试时钟的生成SCAN采用全扫描电路,另外使能了Wrapper ChainEDT“雁栖湖”有一定的寄存器规模,采用了EDT对scan chain进行压缩解压IJTAG对MBIST、EDT、OCC以及其他DFT的静态信号进行控制。- DFT设计流程

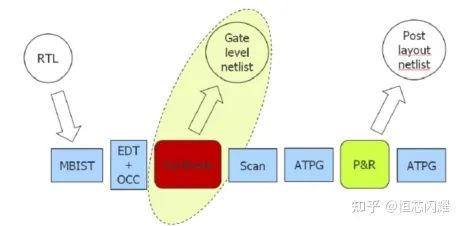

“雁栖湖”微结构设计是基于chisel语言开发,通过chisel编译器编译成可综合的RTL,然后进行综合,DFT设计从可综合RTL开始介入。设计范例中MBIST、OCC、EDT、IJTAG的插入在RTL当中完成,而SCAN则在综合阶段完成;输出的DFT网表交给物理实现,最终基于Post layout netlist进行ATPG向量开发及验证,release到测试机台调试。下图为大致的DFT设计流程示意图。由于chisel编译器编译出来的可综合RTL都是基本的verilog语法,基本上不会因为语法问题而导致DFT EDA工具的不支持;MBIST等逻辑在rtl flow进行,大部分情况下可获得更好的PPA指标。而SCAN可以选择在综合阶段完成或者在综合之后进行,设计范例中选取了与综合工具配套的SCAN工具,可以在综合环境当中完成Scan Insert,以应对带物理信息的综合流程。 图2 DFT设计流程- “雁栖湖”的功能时钟及测试时钟

图2 DFT设计流程- “雁栖湖”的功能时钟及测试时钟

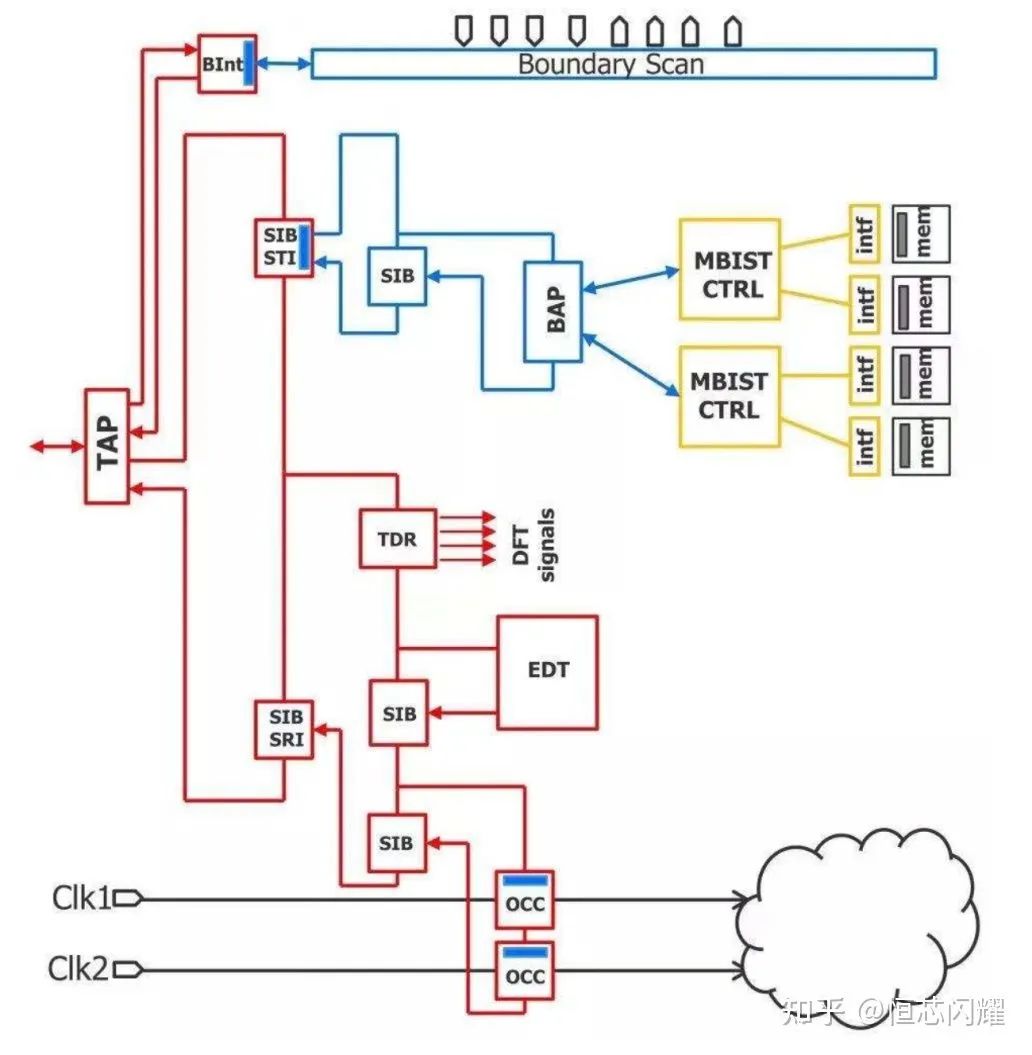

OCC(on-chip-clock)是时钟控制电路,输入时钟源为功能快时钟和测试慢时钟,输出为OCC时钟,可输出特定的时钟脉冲。在功能时钟路径上添加OCC,才能代表时钟是dft可控的。通过配置OCC,可以构造出测试时所需要的时钟脉冲;其中Slow capture mode用于stuck-at/iddq测试,Fast capture mode用于transition测试。“雁栖湖”为单一时钟设计,主时钟是io_clock;设计范例中对io_clock添加occ,测试时钟复用到GPIO,频率设定为48M。 图3 OCC时钟“雁栖湖”的功能复位“雁栖湖”的功能复位采用的同步复位结构,综合出来的时序逻辑均是不带复位端的寄存器,在DFT的设计当中不需要关心复位信号,也不需要定义复位。IJTAG网络(Internal JTAG)设计范例通过IJTAG网络对MBIST、EDT、OCC以及其他DFT的静态信号进行控制。IJTAG电路是基于IEEE1687协议进行设计的控制电路,最终挂载在JTAG TAP下,由SIB、TDR两部分电路构成,如下图所示:

图3 OCC时钟“雁栖湖”的功能复位“雁栖湖”的功能复位采用的同步复位结构,综合出来的时序逻辑均是不带复位端的寄存器,在DFT的设计当中不需要关心复位信号,也不需要定义复位。IJTAG网络(Internal JTAG)设计范例通过IJTAG网络对MBIST、EDT、OCC以及其他DFT的静态信号进行控制。IJTAG电路是基于IEEE1687协议进行设计的控制电路,最终挂载在JTAG TAP下,由SIB、TDR两部分电路构成,如下图所示: 图4 整芯片IJTAG网络DFT的新增端口设计范例规定了DFT新增端口的类型,以方便与外部模块通信,新增端口如下表所示:PortDirectionSpecificationijtag_tckInputIJTAG协议信号ijtag_resetInput

图4 整芯片IJTAG网络DFT的新增端口设计范例规定了DFT新增端口的类型,以方便与外部模块通信,新增端口如下表所示:PortDirectionSpecificationijtag_tckInputIJTAG协议信号ijtag_resetInput

ijtag_ceInput

ijtag_selInput

ijtag_siInput

ijtag_soOutput

dft_atpg_clkInputDft Test Clockdft_seInputScan Enableedt_updateInputEdt Updatedft_edt_int_chn_si_default[n:0]InputEdt Channel Scan Indft_edt_int_chn_so_default[n:0]OutputEdt Channel Scan Outdft_edt_wrp_chn_si_default[n:0]InputEdt Channel Scan Indft_edt_wrp_chn_so_default[n:0]OutputEdt Channel Scan Out### DFT的设计数据

本章节侧重于介绍SCAN、EDT、MBIST以及向量的设计数据。

SCAN设计数据

- 采用全扫描电路,模块包括MBIST逻辑在内有50.8w寄存器,均按单bit寄存器计算。

- 不同scan chain长度尽量保持Balance(短链链长控制在250左右)

- 为了方便timing收敛,一条scan chain上只对应同一个功能时钟域,链尾统一加上LOCKUP(解决func_clk到edt_clk之间的hold time)

- 模块使能wrapper chain,加入wrapper cell原则为share first,reuse_threshold阈值设置为20

模块wrapper cell统计,物理实现需关注被加入Dedicate Wrapper Cell的功能接口时序:

模块Scan regAllWrapper cellAllInputWrapper cellOutputWrapper cellSharingWrapper cellDedicateWrapper cellXSTop50.8w315999521642292867- 时钟、dft相关端口不加入wrapper cell

- 在transition测试时,避免模块在intest模式下wrapper chain高频shift

EDT设计数据

- 模块设计两个edt

普通scan chain、reserved chain压缩到int edt当中

occ chain、gt_se_chain、sti chain、wrp chain压缩到wrp edt当中

模块edt chain/channel设置:

模块Int edt

Wrp edt

Chain CountChannel CountChain CountChannel CountXSTop200010:10201:1- 对EDT的Compactor进行打拍,避免组合逻辑深度过深

- edt channel根据物理距离进行打拍

- EDT使能lowpowershift,min_switching_threshold_percentage设置为15(翻转率)

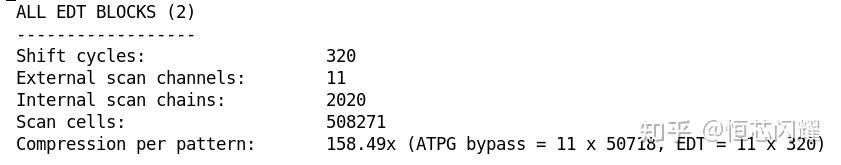

- 在lowpowershift模式下,模块整体的shift cycle为320,整体压缩比为158x

图5 EDT设计数据ATPG向量数据

图5 EDT设计数据ATPG向量数据

- 采用PatternRetarget向量生成技术

技术优点在于可模块级生成向量,为了达成这个规格,需模块内OCC及wrapper chain配合

“雁栖湖”在例化多核的情况下,模块级向量也可被多次复用,向量生成效率优势会更明显

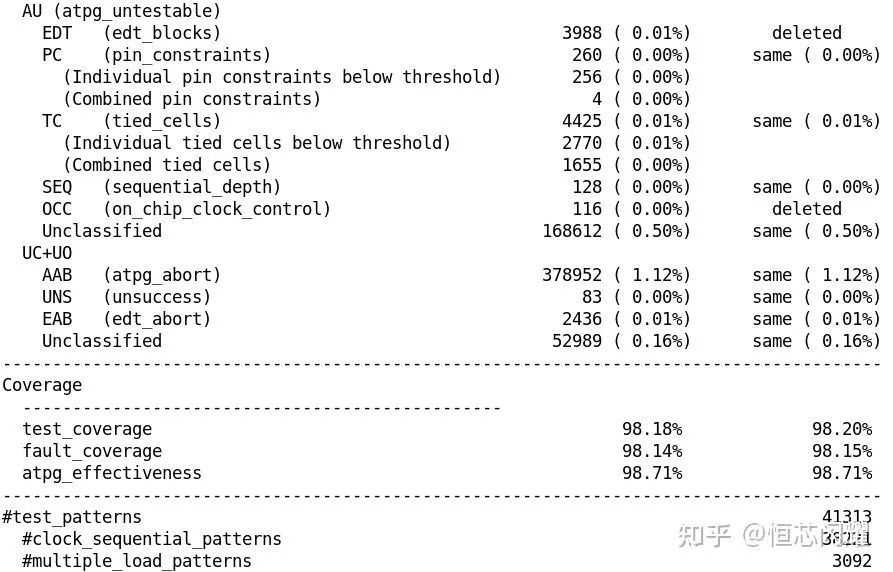

- 模块覆盖率及向量数

Stuck-at

Transition

Intest模式Normal模式Intest模式覆盖率99.86%99.92%98.20%向量数219572266041313- 覆盖率具体情况:

图6 Intest模式下的Stuck-at向量(接口逻辑未被覆盖)

图6 Intest模式下的Stuck-at向量(接口逻辑未被覆盖) 图7 Normal模式下的Stuck-at向量(包括了对接口逻辑的覆盖)

图7 Normal模式下的Stuck-at向量(包括了对接口逻辑的覆盖) 图8 Intest模式的Transition向量MBIST设计数据

图8 Intest模式的Transition向量MBIST设计数据

- “雁栖湖”的Cache规格为:

16KB L1 Cache,128KB L1plus Cache for instruction

32KB L1 Data Cache

1MB inclusive L2 Cache

- MBIST默认算法由Memory Model决定

- 支持MBIST测试算法Soft Program

- 支持Memory物理位置诊断

- 支持Memory bypass,提高Memory Shadow Logic覆盖率;

设计范例中为了追求最高覆盖率采用了sync_mux结构的membypass,当然这会导致memory周边的绕线紧张,光是membypass reg count占了3.5w;而完全不加memory bypass逻辑的模块stuck-at覆盖率为99.09%,且大部分au fault分布在Mbist Ctrl到Memory的路径上;在“南湖”上会采用新型的mbist架构规避此问题。开发者在面对Design面积紧张的情况下,对此规格可做精细化调整。

- “雁栖湖”功能逻辑的reg count为36w,设计范例所加mbist逻辑的reg count为14.7w

- 支持dftramhold,用于IDDQ测试场景

- Memory的调速信号DFT可控

- Memory分组情况:

Mbist Controller所属时钟域Memory片数备注C1io_clock15core/ctrlBlock/ftqC2io_clock25core/frontend/ifu/bpuC3io_clock25core/frontend/ifu/bpuC4io_clock20core/frontend/ifu/icacheC5io_clock24core/l1pluscacheC6io_clock24core/l1pluscacheC7io_clock24core/memBlock/dcacheC8io_clock24core/memBlock/dcacheC9io_clock24core/memBlock/dcacheC10io_clock16core/memBlock/dcacheC11io_clock20core/ptwC12io_clock20core/ptwC13io_clock16l2cacheC14io_clock16l2cacheC15io_clock16l2cacheC16io_clock16l2cachec17io_clock17l2cache- Memory支持并行测试,但会因翻转率过高导致功耗过大;实际测试过程中考虑功能功耗模拟,建议对以上Mbist Controller串行测试。

测试时间评估

最终上测试机台的向量如下列表所示,JTAG_TCK以24M供给,测试时钟以48M供给:Pattern NameTest Time向量深度CHAIN_XSTop1.38ms0.06MIDDQ_XSTop6.95ms0.32MSTUCK_XSTop153.87ms7.04MTRANS_XSTop280.54ms12.84MMBIST_XSTop4.37ms0.1MTotal447.11ms20.36M

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:14945次2020-12-03 22:52:27

-

浏览量:2343次2022-03-22 09:00:12

-

浏览量:2473次2020-01-14 10:34:58

-

浏览量:6381次2022-03-26 09:00:12

-

浏览量:4725次2022-08-17 09:01:18

-

浏览量:9072次2021-08-09 15:05:08

-

浏览量:2112次2018-11-10 13:36:50

-

浏览量:3282次2020-11-03 09:31:20

-

浏览量:2479次2022-03-25 09:00:33

-

浏览量:1634次2023-03-29 17:52:20

-

浏览量:4382次2018-09-15 17:23:42

-

浏览量:1632次2021-12-01 17:26:38

-

浏览量:2073次2019-11-21 14:06:15

-

浏览量:6759次2022-05-30 15:26:15

-

浏览量:787次2023-10-23 17:56:00

-

浏览量:2230次2017-12-27 14:17:48

-

浏览量:2179次2022-01-31 09:00:15

-

浏览量:2180次2020-08-14 18:15:32

-

浏览量:123次2025-03-08 11:24:40

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

如果只是如果

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友