芯片片上SRAM存储概略及生成使用实践 (上)

芯片是一个庞杂的系统,体量分布非常宽泛,从百十个gate的数模混合芯片(譬如:PMU,sensor等等)一路到上百亿门的复杂高端数字芯片(譬如:苹果Axx, 麒麟:9xx,联发科:天玑系列抑或各个巨大无比的NP网络芯片等等)

同样的芯片,也可以从不同维度进行区分,譬如:逻辑功能分类(core,peripheral,interface 等等),门级功能分类(寄存器,组合逻辑,存储器,phy等等)。

这里,就一起来从芯片的门级功能展开说起,一起来看看片上存储的细节和生成实践,本系列分为上,中,下三部分,这一篇是开篇,一起走就片上存储的世界。

芯片片上存储分类

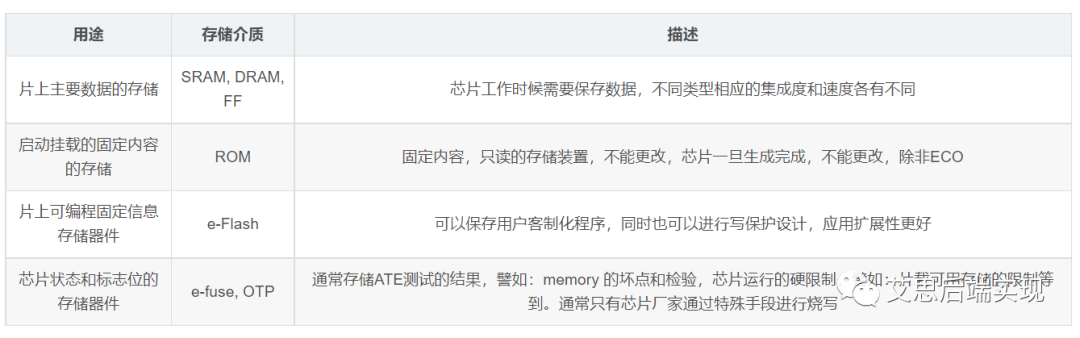

为了配合芯片的功能和应用,对于数据存储会有非常多的使用场景,通常可以用下列表格进行描述

对于大型芯片而言,以上种种可能都会用到,但是最普遍,占比最大的还是第一类,这里使用下表对三种存储方式各自的特点进行一个拆解

可以看到,通过上表比较,对于大型的存储需求,以及从简单易用角度而言,SRAM是此类场景的不二之选

SRAM的存储结构

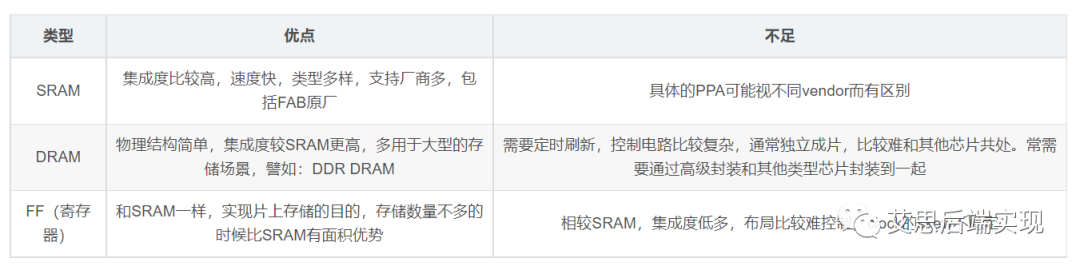

SRAM的核心存储器件,通常被称为bit cell。具体如下图所示

可以看到,外部逻辑通过控制信号:BL(BitLine)和WL(WordLine)对bit cell进行写入和读取,这也就是通常所说的六管结构,由四个NMOS和两个PMOS组成

写操作

- 先把需要写入的数据加载到BL上,如果是准备写入逻辑‘1’,那么就先在BL上就置成逻辑‘1’,~BL置成逻辑‘0’

- 在WL上置成逻辑‘1’,这样通过选通M5/M6,对应的逻辑写到了Q和~Q上,这样就完成了逻辑‘1’的写入

对于逻辑‘0’的写入方式类似

读操作1. 预充电到BL/~BL端到高电平

- 然后把WL置高,从而打开M5/M6,

- 如果Q=“1”,则晶体管M1导通,~BL会被拉低到低电平

- 对于另一侧,因~Q=“0”,晶体管M4和M6导通,通过VDD将BL拉到高电平

这样就完成了将逻辑1读取到了BL上

对于逻辑‘0’的读取方式类似

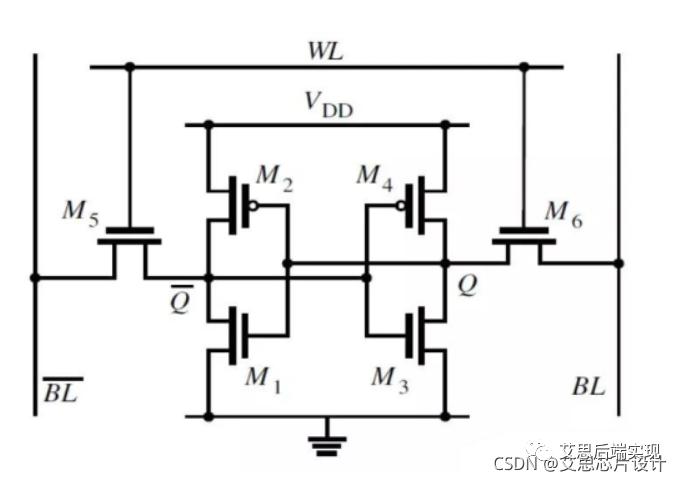

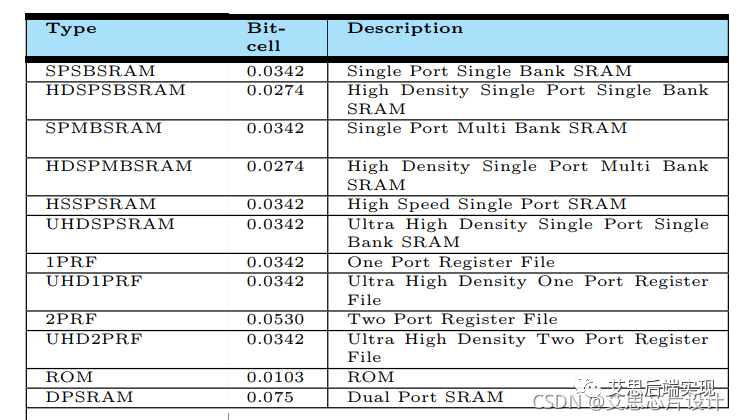

对于bit cell而言,在在同一种工艺下,不同功能的bit cell大小或有不同,这里以TSMC 7nm的memory bit cell为例 可以看到,对于HD,RF,DP会呈现不同的bit cell的大小,这里的每一个bit-cell就是一个完整的存储1bit的器件大小。基于此,和同样储存1bit的DFF进行面积比对的优势明显,详见下图:

可以看到,对于HD,RF,DP会呈现不同的bit cell的大小,这里的每一个bit-cell就是一个完整的存储1bit的器件大小。基于此,和同样储存1bit的DFF进行面积比对的优势明显,详见下图: 片载SRAM的结构拆解

片载SRAM的结构拆解

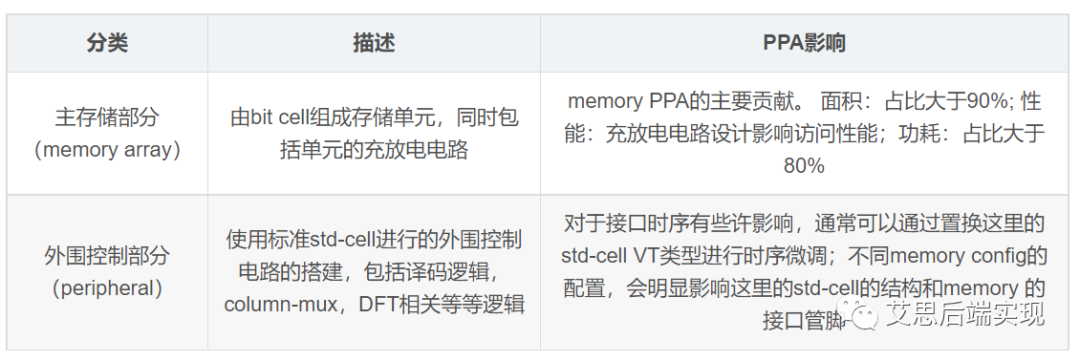

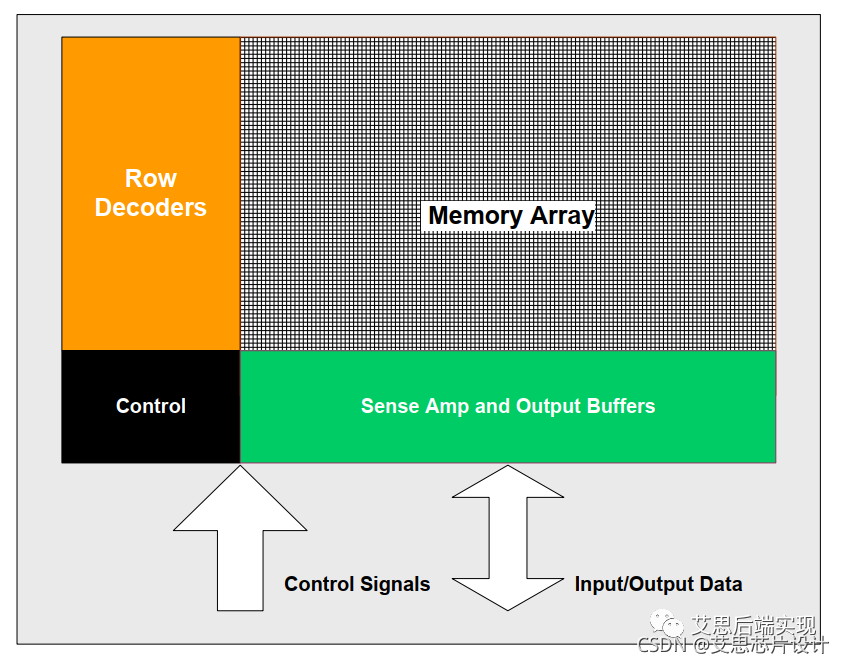

对于芯片上的SRAM,是由一个个bit cell拼接成一个矩阵,矩阵的横竖分布被BL和WL来控制,这个由bit cell组成的矩阵通常就会被称为memory array通常的SRAM都是由以下两个部分组成的

SRAM的大致示意图如下

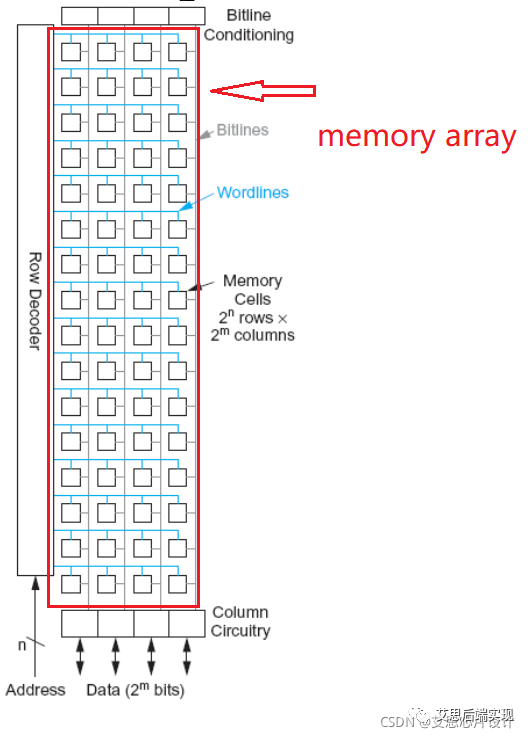

这里很明显可以看到控制逻辑的身影,从外部访问方便而言,它们对memory array成包围模式。更为真实的SRAM结构如下图所示,

这里很明显可以看到控制逻辑的身影,从外部访问方便而言,它们对memory array成包围模式。更为真实的SRAM结构如下图所示, 一个SRAM的简单访问步骤如下:1. 首先确定读抑或写操作,对BL进行对应的与操作,详见上述bitcell的读写操作释义

一个SRAM的简单访问步骤如下:1. 首先确定读抑或写操作,对BL进行对应的与操作,详见上述bitcell的读写操作释义

- 配置地址线,选通对应的WL

- 如果是读操作:下方的Data就会出现一整行WL的bitcell的数据;如果是写操作:下方的Data就会写入到选定WL的bitcell中

上述访问呈现以下几个要点:- 读写操作通常都是对一个WL进行的操作

-

如果,WL的bitcell 位数不变,地址的深度直接决断了SRAM的物理高度。

-

SRAM的容量通常由NW*NB来决断

-

NW:Number of Word,SRAM深度

-

NB:Number of Bit, SRAM宽度

-

Bitcell Count:NW * NB SRAM的容量

-

地址译码和数据通路通常由std-cell直接构成,是影响接口时序的一个因素

-

支持bitwise的SRAM,在写入的时候,可以通过对某一个bitcell对应的BL进行管控,从而控制单bit的写操作。

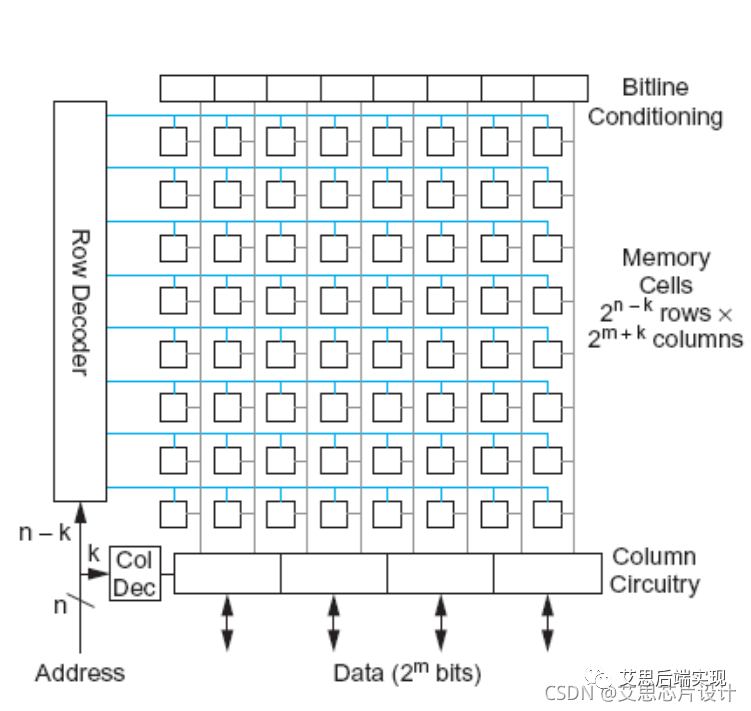

结合bitcell的读取方式,小伙伴们可以想一想,为什么SRAM的读取没有按bit选通的功能呢?对于通常的用户,一般都会常见一个深度很大的SRAM,譬如:256K * 8之类的。但是对于上述SRAM’结构,可以感知,这样单纯的累加bit cell高度的会有以下一些问题- SRAM过于细长,对布局不友好, PG的接触点也不太均衡

- 由于SRAM的地址和数据出口通常都是居中分布式规划,过高的SRAM,必定会在一定的高度的时候引发驱动能力的问题

所以,这里提出了一个ColumnMux (CM)的解决方式:当NW >> NB的时候,在不改变SRAM 大小的时候,可以使用增加CM的方式来解决这类问题 可以看到,竖长的SRAM拦腰被折成两半,并排分布,有效的降低了SRAM的高度。

可以看到,竖长的SRAM拦腰被折成两半,并排分布,有效的降低了SRAM的高度。

用户通过使用CM=2,相应的也增加CM decoder部分组合逻辑。一个简单的换算公式如下:Depth * Width = (Depth/2) * width + (Depth/2) * width地址线的部分(高位)会直接参与CM的译码,从而可以2的幂次方的折叠方式有效降低SRAM的高度。同样也会由于bitcell更为聚集,接口时序也会有相应的提升,对应的面积增长(CM decoder)在大规模SRAM下的影响,可以忽略不计。本章词汇

【敲黑板划重点】

从基础理论学习SRAM,了解SRAM的读写原理,给后面的使用打下基础参考资料

Neil H.E. Weste • David Money Harris CMOS VLSI Design - A Circuits and Systems Perspective

TSMC TSMC N7 SRAM Compiler Databook喜欢文章的小伙伴,点赞加关注吧!

欢迎一起加入号主的知识星球,近期热门话题:- CTS

欢迎一起加入号主的知识星球,近期热门话题:- CTS

- PAD ring planning

- eBook share: tech_file and design rule

- PT tips

- LVS naming conversion and physical cell handling

- Calibre GDS operation

- ......

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:3642次2018-04-26 15:06:40

-

浏览量:3152次2020-07-29 15:38:57

-

浏览量:773次2023-12-18 18:31:22

-

浏览量:11993次2022-03-18 09:00:47

-

浏览量:3468次2020-07-30 14:53:44

-

浏览量:3485次2020-04-10 11:14:21

-

浏览量:1776次2020-04-03 09:38:23

-

浏览量:2944次2021-12-11 15:15:30

-

浏览量:3570次2020-07-28 18:03:59

-

浏览量:1532次2023-07-27 10:19:06

-

浏览量:1832次2020-02-28 18:49:51

-

浏览量:2294次2019-12-28 10:40:42

-

2020-06-23 17:04:09

-

浏览量:2311次2020-02-26 19:51:32

-

浏览量:1058次2024-01-08 18:13:05

-

浏览量:2327次2019-08-30 14:48:05

-

浏览量:1307次2023-12-16 22:32:09

-

2023-12-24 00:06:09

-

浏览量:2638次2018-01-17 12:13:20

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友