Cadence Voltus-功耗分析&IR-drop(三)

Cadence Voltus-功耗分析&IR-drop(一)Cadence Voltus-功耗分析&IR-Drop(二)上文讲了IR-Drop的原理及Static Rail Analysis,本文补讲IR-Drop有哪些危害及现象。

IR-Drop的危害及现象

- “石头”一块

芯片回片后无法bring up,像块石头一样不工作,设计者可能怀疑芯片前端设计有重大问题,比如时钟、复位有问题,但前仿、后仿逻辑功能都正确。

全局性的IR-Drop问题,可试着增大电压,看芯片能否正常工作。

- 概率性错误

芯片大体工作正常,但是在某些场景下、某些激励下(比如:bus总线所有bit全部翻转)会出现芯片局部IR-Drop或ground bounce严重到一定程度,无法驱动逻辑门翻转。可以理解为某些场景下芯片局部为“石头”,device器件的阈值电压无法满足,device器件根本不翻转,降频也无济于事。设计者可能怀疑RTL设计有功能bug,但前仿、后仿无法复现问题,逻辑仿真都正确,设计者可能又会怀疑Foundry的良率问题,实际上很可能是芯片局部IR-Drop问题。可试着增大电压,看芯片能否正常工作。

- Timing Failures

芯片大体工作正常,但是在某些场景下、某些激励下逻辑门drive/transition time不满足,导致timing violation功能错误。可试着降频使芯片正常工作,但是这影响了芯片产品Performance,竞争力大打折扣。再来一版,时间成本、金钱成本等代价极高。

- 时钟buffer

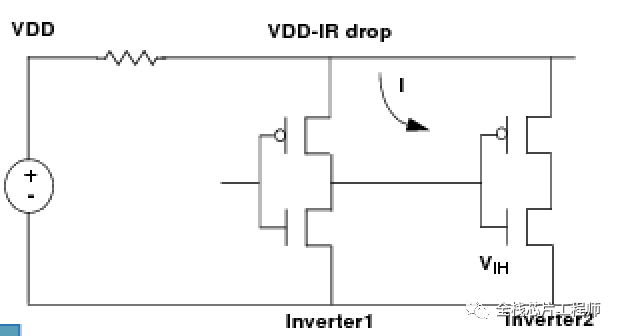

时钟buffer上5%的电压降,可降低其15%的速度,如下图clock buffer:

Inverter1的输出电压仅能达到VDD - IR-Drop,所以Inverter2的栅极驱动电压不足VDD,导致Inverter2的器件速度下降。

通常的,timing library会为一定范围内的IR-Drop预留margin,这部分margin叠加上SDC的timing margin约束在芯片设计实现上,若实际IR-Drop超过了一定范围,芯片则会fail。相反,若电源网络过设计,则占用了routing 资源,芯片面积也会变大。此外,为了预防IR-Drop,电源网络往往过设计,并且无法评估到底过设计了多少。

感谢阅读,别走!点赞、关注、转发后再走吧

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:6863次2021-12-11 15:12:34

-

浏览量:11819次2022-03-12 09:00:12

-

浏览量:17097次2022-03-11 09:00:13

-

浏览量:11117次2021-12-11 15:12:29

-

浏览量:10325次2021-12-11 15:15:27

-

浏览量:6436次2021-12-01 10:32:46

-

浏览量:5295次2022-08-17 09:01:18

-

浏览量:8085次2022-04-01 09:00:15

-

浏览量:8042次2021-12-11 15:15:40

-

浏览量:9046次2022-01-01 09:00:13

-

浏览量:3636次2021-12-21 09:00:33

-

浏览量:3076次2023-04-19 09:16:00

-

浏览量:6130次2021-12-27 09:00:22

-

浏览量:3985次2019-11-21 09:05:53

-

浏览量:2692次2022-03-08 09:00:11

-

浏览量:2646次2017-12-24 23:58:37

-

浏览量:4135次2022-03-15 09:00:13

-

浏览量:4639次2021-07-16 10:09:05

-

浏览量:3138次2018-01-11 15:31:57

-

浏览量:2266次2020-07-28 17:27:40

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友