Cadence Voltus-功耗分析&IR-Drop(二)

- IR Drop & Ground Bounce

-

IR Drop

理想状态下,下图v1、v2、v3、v4节点的电压应该相同,而实际上电流从VDD pad流到v4经历了R11-R12-R13-R14等电阻网络,产生了压降,导致G4 cell的power pin的电压不足VDD,一般电压降需要控制在2%-5%以内,具体根据实际项目、实际工艺等决定;

-

Ground Bounce

同样,G4 cell的ground pin的电流要经过R24-R23-R22-R21回流到VSS pad,因此G4 cell的ground pin电压也不是0,产生了Ground Bounce;

-

Average and Peak current当G1、G2、G3、G4同时翻转,瞬时IR Drop将会很大,计算如下:

如果每4拍发生一次全翻转,那么G4的IR Drop平均下来就只有其1/4。实际上,芯片规模越大,cell全部同时翻转的概率就越小,因此Average IR Drop和Peak IR Drop的值就相近。

如果每4拍发生一次全翻转,那么G4的IR Drop平均下来就只有其1/4。实际上,芯片规模越大,cell全部同时翻转的概率就越小,因此Average IR Drop和Peak IR Drop的值就相近。 -

Static IR-Drop目前对于130nm及以上的设计,Static IR-Drop仍然广泛使用,其能有效分析出由于power rail开路、via丢失、power straps不足、电源线宽度不足等等问题造成的IR Drop & EM问题,尤其是EM分析,由于Static IR-Drop可以仿真芯片长时间使用的平均损耗,所以对分析EM而言更加接近真实情况。后端设计可利用Static IR-Drop先将IR Drop优化到2%-5%以内(具体根据实际项目决定),然后利用Dynamic analysis分析transient IR Drop。

-

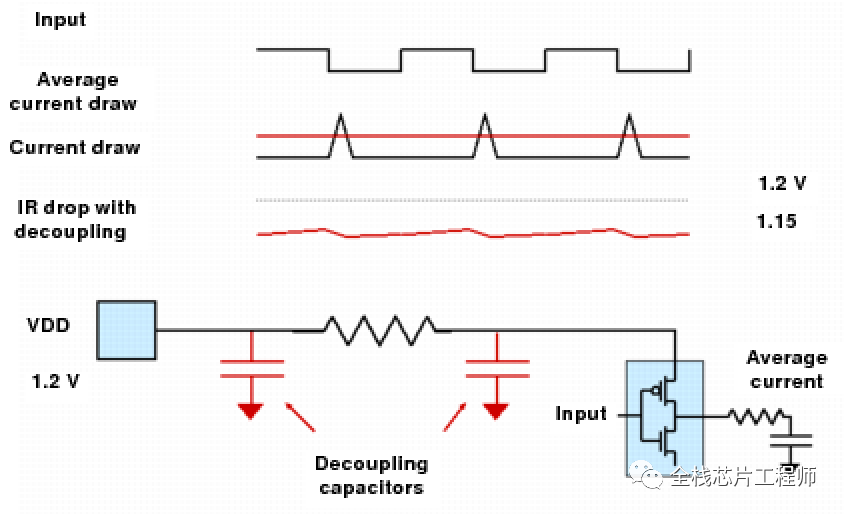

Decoupling capacitors(to mitigate voltage drops)

添加足够的Decoupling capacitors可有效缓和transient电压降,这时,Dynamic IR Drop和Static IR-Drop的分析结果则相近。

-

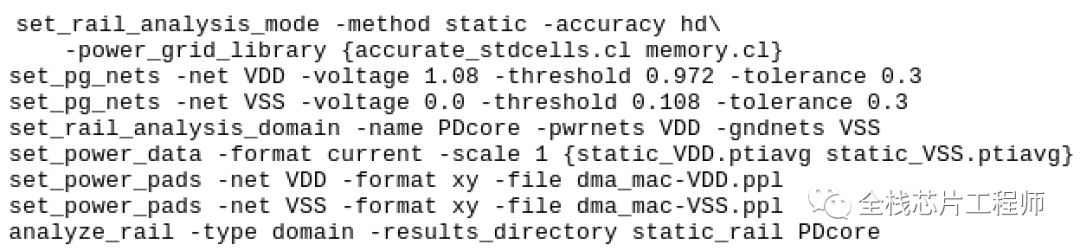

IR-Drop -> Setup & Run

上一篇文章Cadence Voltus-功耗分析&IR-drop(一)已经写了如何生成power grid library,其中technology library是rail analysis必须的配置,且应写在各个power grid library最前面,为了提高IR分析的精度,std cell & macro也被要求利用spice model/spice corner/spice subckts生成power grid library。

-

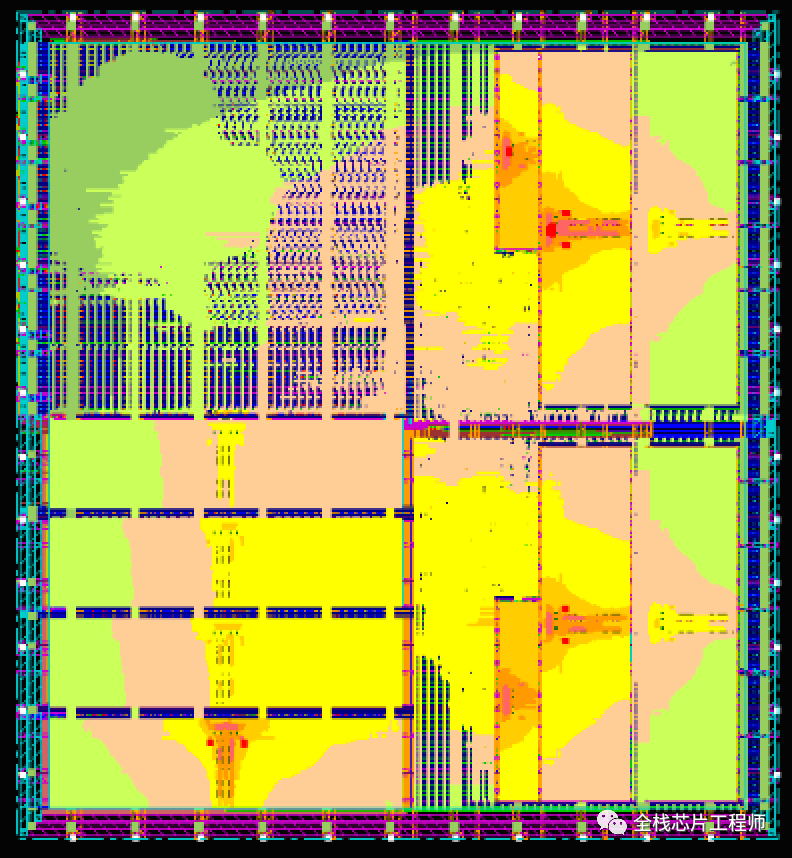

IR drop plot

感谢阅读,别走!点赞、关注、转发后再走吧

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:6433次2021-12-01 10:32:46

-

浏览量:6861次2021-12-11 15:12:34

-

浏览量:11812次2022-03-12 09:00:12

-

浏览量:10321次2021-12-11 15:15:27

-

浏览量:11116次2021-12-11 15:12:29

-

浏览量:5293次2022-08-17 09:01:18

-

浏览量:8083次2022-04-01 09:00:15

-

浏览量:8040次2021-12-11 15:15:40

-

浏览量:9044次2022-01-01 09:00:13

-

浏览量:3633次2021-12-21 09:00:33

-

浏览量:7482次2021-12-23 09:00:16

-

浏览量:6125次2021-12-27 09:00:22

-

浏览量:3074次2023-04-19 09:16:00

-

浏览量:2690次2022-03-08 09:00:11

-

浏览量:3983次2019-11-21 09:05:53

-

浏览量:4132次2022-03-15 09:00:13

-

浏览量:4637次2021-07-16 10:09:05

-

浏览量:2207次2019-07-31 14:23:46

-

浏览量:4705次2021-07-03 14:35:11

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友