资讯文章

Verilog二维数组作为输入输出端口可以吗

先说答案:不行。

通常,reg [7:0] mem [1:0]这种写法是作为内部二维寄存器使用的,比如定义一个1KB的存储器,可以用reg [7:0] memory [0:1023],或者reg [7:0] memory [1023:0]。那二维数组作为输入输出端口可以综合不?

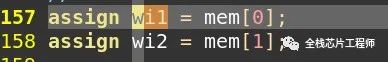

做个小实验,简单造个小代码:

用input [7:0] mem [1:0]这种二维数组作为input端口,

Verdi检查

首先用Verdi编译看看报错不:

上图很明显,Verdi默认就直接支持这种SV类型语法。

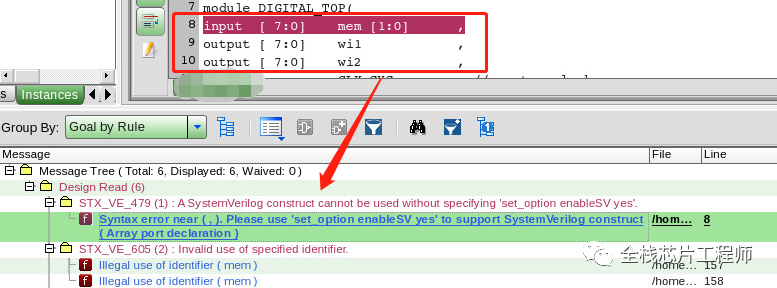

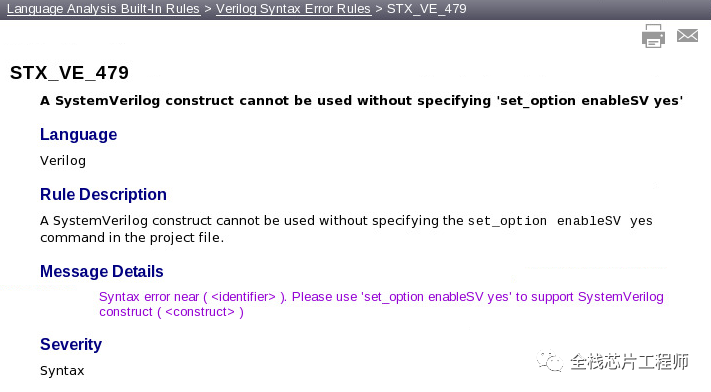

Spyglass检查

Spyglass就能严格报出来,除非set_option enableSV yes,否则不支持这种sv语法特性,

DC工具

那么Design Compiler是否支持这种语法综合呢?

综合一下,查看LOG:

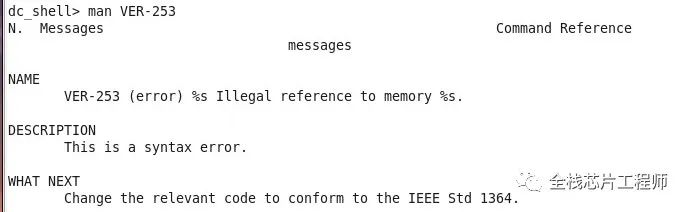

也很明显,直接报Error,综合进程终止,DC是不支持的。

man查询一下报的错:VER-253:

感兴趣的朋友可以用C家的genius试试。

结论

结论:Verilog语法不支持二维数组作为输入输出端口。

可能有同学吐槽Verilog语法太僵硬了,不如sv便捷强大,况且很多国外团队已经用sv进行开发了,但是DC工具更希望RTL开发者明确指定每一根输入输出信号线的具体连接关系,虽然工作量繁杂一点,但可以避免工具与人的理解不一致而造成的芯片错误, 也迫使开发者想清楚每根线怎么连接。

感谢阅读,别走!点赞、关注、转发后再走吧

转载:全栈芯片工程师

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:5329次2020-08-19 22:25:39

-

浏览量:1385次2022-12-09 14:00:21

-

浏览量:1990次2023-04-18 09:05:54

-

浏览量:11609次2021-03-20 13:22:58

-

浏览量:1104次2023-08-17 10:17:40

-

浏览量:1296次2023-04-14 11:29:55

-

浏览量:6923次2021-03-22 00:49:53

-

浏览量:17640次2020-11-12 21:47:17

-

浏览量:7263次2021-03-14 02:34:44

-

浏览量:7604次2021-03-15 23:18:36

-

2021-03-21 22:03:30

-

浏览量:746次2023-09-16 10:51:37

-

浏览量:2170次2021-01-27 16:48:37

-

浏览量:6675次2021-01-08 02:27:20

-

浏览量:7207次2021-04-19 14:56:57

-

浏览量:10916次2020-12-13 19:59:59

-

浏览量:11549次2021-06-25 16:41:43

-

浏览量:24792次2021-06-21 20:56:40

-

浏览量:4529次2024-02-20 17:35:09

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友