标准单元库设计(三)

Special cells

Tap cells● Tap cells are used to provide substrate connection.● They are used to avoid latch-up.● They connect n-well to VDD and p-sub to VSS.● They are inserted in layout at regular intervals based on tap rules (tap to gate distance) defined in the technology DRC file.Filler cells● Filler cells are used to provide rail continuity, thereby reducing the DRC violations created by the base.● Filler cells are designed in such a way that they contain n-well and p substrate.Metal eco-able cells● The filler cells which are converted to attain any functionality are called metal eco-able cells.● The base layers of both filler cells and metal eco-able cells are same. Some extra metal connections will be added in metal eco-able cells to attain the functionality.● Sizes of these cells are more when compared to normal cells of same functionality.● For example, consider a design having hold violation after the fabrication. One way to overcome the violation is to delay the data-path. In this case we can convert metal eco-able cells to buffer for the delay. (generally done during re-spin of chip).Antenna diode● During fabrication stray charges get accumulated in metal layers. The gate gets ruptured when the amount of these charges are more than threshold. This effect is called antenna effect. The threshold is decided by metal layer area to gate area ratio.● To overcome the antenna effect we use antenna diodes.● Zener diodes will be connected to the metal layers to remove the excess charges.

Fig4: Antenna diode● Another way to overcome antenna effect is to add jumpers. Use higher metal layers for connection.

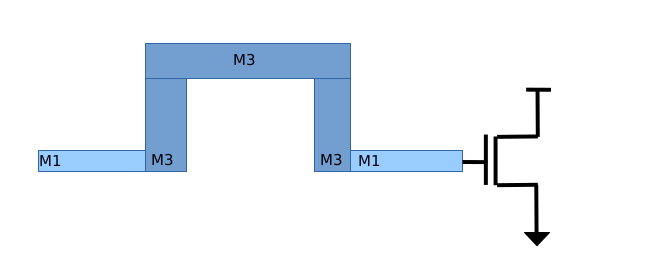

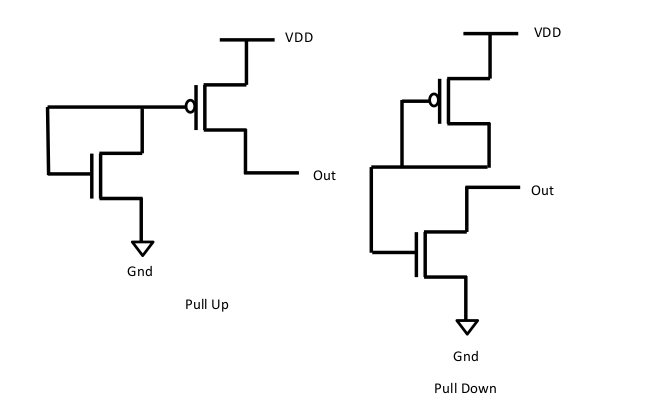

Fig5: JumperDe cap cells (Decoupling capacitor cells)● De cap cells are capacitors added in design between power and ground rails.● When there is drop in power rail, these cells act like a battery and maintain the voltage across rails.● These cells aids IR drop issue and removes glitches in power.● In a design most of the power consumption is done by clock circuits. Assume that all the clock blocks are clustered in an area, then they will consume more power, i.e. they drew more current which will increase IR drop. In this case de cap cells can be used.End cap cell● End cap cells are added near the end of rows to terminate the rows properly.● The n-wells of end cap cells are properly terminated within the cell.Tie cell● Tie cells are used to avoid direct gate connection to the power or ground network thereby protecting the cell from damage.● In your design, some cell inputs may require a logic 0 or logic 1 value. Instead of connecting these to the VDD/VSS rails/rings, you connect them to special cells available in your library called TIE cells.● In tie high cell, nmos acts as diode connected and gives logic 0 to the gate of pmos, so we will get logic 1 as output whereas in tie low cell, pmos act as diode connected and gives logic 1 to the gate of nmos, so we will get logic 0 as output.

Fig6: Tie cellSpare cell● Spare cells are normal standard cells but they act as redundant cells as they are evenly distributed on the chip in anticipation of future ECO i.e, after the tape out.● After the tape out, sometimes we may have to make some changes to the design to resolve a bug. In these cases we use the pre existing spare cells in the design.● If we carry out the design changes with minimal layer changes, it will save a lot of cost from fabrication point of view as each mask layer has significant cost of its own.● Spare cell inputs are connected to VDD/GND when they are placed in the design and their outputs are left floating.● If they are required to be used, then their inputs are disconnected from VDD/GND and connected to functional logic in ECO mode.

Fig7: Spare CellCharacterization● Characterization is the generation of .lib files, done with respect to PVT corners.● Typically characterization is done for six different loads and six different transitions(slew)● Models used to generate .lib files are NLDM and CCS. CCS is more accurate when compared to NLDM.原文链接:https://mp.weixin.qq.com/s/91uIeOu6Q1MuJuJiZ5OFjg

感谢阅读,别走!点赞、关注、转发后再走吧

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:3188次2022-03-06 09:00:09

-

浏览量:2261次2022-03-07 09:00:09

-

浏览量:9043次2022-01-01 09:00:13

-

浏览量:14573次2022-01-09 09:00:11

-

浏览量:3217次2020-07-20 20:14:23

-

浏览量:2158次2019-11-14 09:08:28

-

浏览量:7032次2022-03-26 09:00:12

-

浏览量:14831次2022-03-25 09:00:11

-

浏览量:2792次2020-07-30 18:41:41

-

浏览量:2341次2020-01-10 11:21:54

-

浏览量:3983次2019-11-21 09:05:53

-

浏览量:1991次2023-04-19 09:06:13

-

浏览量:8326次2021-09-29 13:43:29

-

浏览量:6341次2020-08-23 21:17:12

-

浏览量:3132次2022-01-13 09:00:13

-

浏览量:7344次2021-01-08 02:45:30

-

浏览量:12551次2021-01-29 12:25:06

-

浏览量:1502次2023-11-10 15:59:27

-

浏览量:1277次2023-08-15 14:40:41

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友