技术专栏

芯片设计之CDC异步电路(五)

芯片设计之CDC异步电路(四)

芯片设计之CDC异步电路(三)

芯片设计之CDC异步电路(二)

芯片设计之CDC异步电路(一)

1 CDC常见错误

===

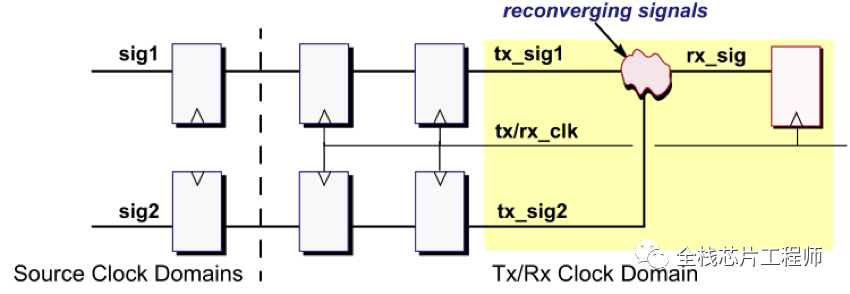

1.1 Reconvergence

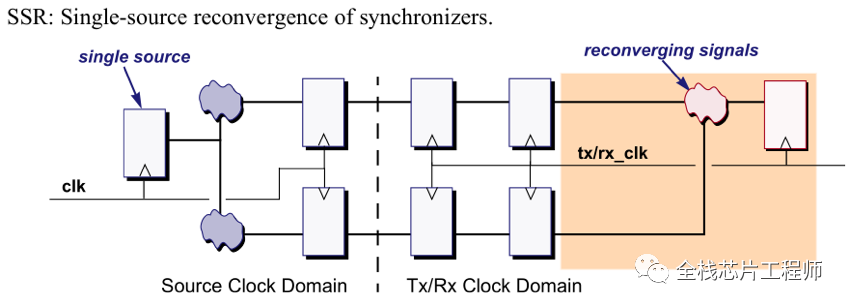

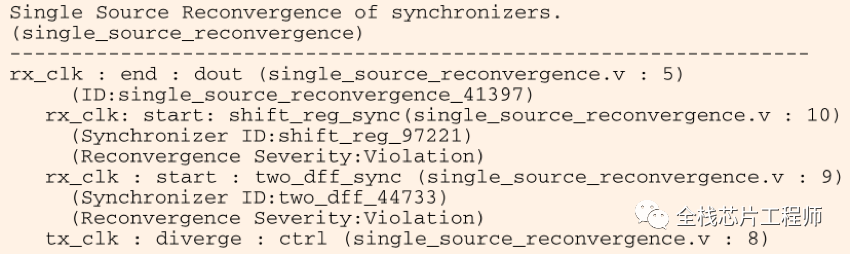

1.1.1 single_source_reconvergence

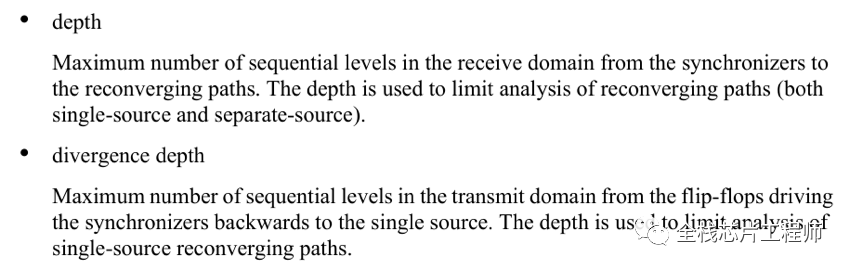

结构:同一个信号源头,两个同步处理器。这里提一下,有两个CDC分析工具的参数配置:

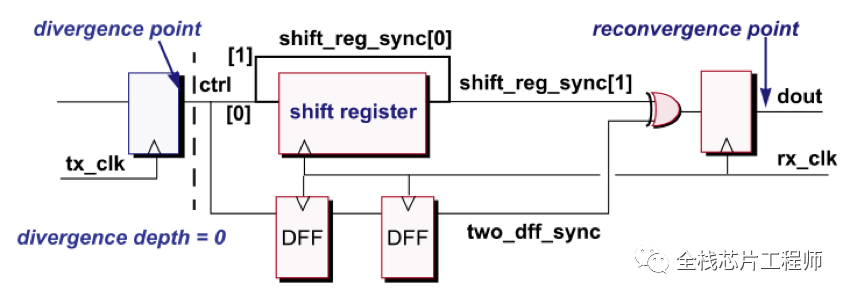

1.1.2 案列1:divergence_depths为0

<pre class="code-snippet__js" data-lang="properties">```

<span class="code-snippet_outer"><span class="code-snippet__meta">//</span> <span class="code-snippet__string">divergence point</span></span>always @ (posedge tx_clk)

<span class="code-snippet_outer"> <span class="code-snippet__attr">ctrl</span> <span class="code-snippet__string"></span></span>

<span class="code-snippet_outer"><span class="code-snippet__meta">//</span> <span class="code-snippet__string">two_dff synchronizer</span></span>always @ (posedge rx_clk) begin: two_dff

<span class="code-snippet_outer"> <span class="code-snippet__attr">reg</span> <span class="code-snippet__string">temp;</span></span>temp

<span class="code-snippet_outer"> <span class="code-snippet__attr">two_dff_sync</span> <span class="code-snippet__string"></span></span>end

<span class="code-snippet_outer"> </span>shift_reg synchronizer

<span class="code-snippet_outer"><span class="code-snippet__attr">always</span> <span class="code-snippet__string">@ (posedge rx_clk) begin: shift_reg</span></span>shift_reg_sync

<span class="code-snippet_outer"><span class="code-snippet__attr">end</span></span>

<span class="code-snippet_outer"><span class="code-snippet__meta">//</span> <span class="code-snippet__string">reconvergence point</span></span>always @ (posedge rx_clk)

<span class="code-snippet_outer"> <span class="code-snippet__attr">dout</span> <span class="code-snippet__string"></span></span>

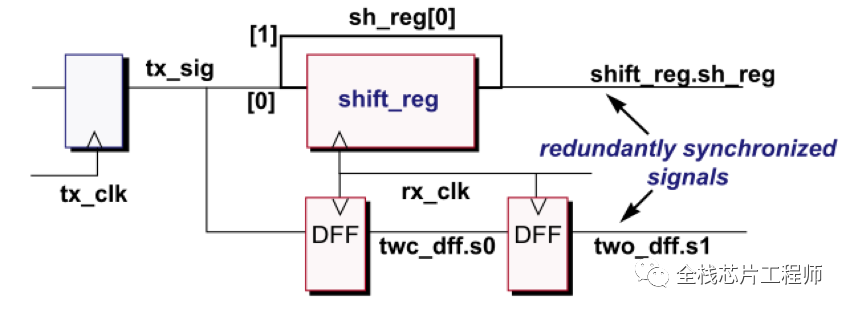

电路如下:divergence_depth为0

CDC报告如下:

1.2 Redundant

案例1:

<pre class="code-snippet__js" data-lang="properties">```

<span class="code-snippet_outer"><span class="code-snippet__meta">//</span> <span class="code-snippet__string">two_dff synchronizer of tx_sig</span></span>always @ (posedge rx_clk) begin: two_dff

<span class="code-snippet_outer"> <span class="code-snippet__attr">reg</span> <span class="code-snippet__string">s0 , s1;</span></span>s0

<span class="code-snippet_outer"> <span class="code-snippet__attr">s1</span> <span class="code-snippet__string"></span></span>end

<span class="code-snippet_outer"><br></br></span>two_dff synchronizer of tx_sig

<span class="code-snippet_outer"><span class="code-snippet__attr">always</span> <span class="code-snippet__string">@ (posedge rx_clk) begin: shift_reg</span></span>reg [1:0] sh_reg;

<span class="code-snippet_outer"> <span class="code-snippet__meta">sh_reg =<span class="code-snippet__string"> {sh_reg[0], tx_sig};</span></span></span>end

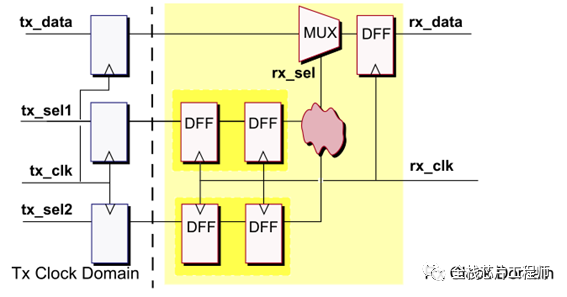

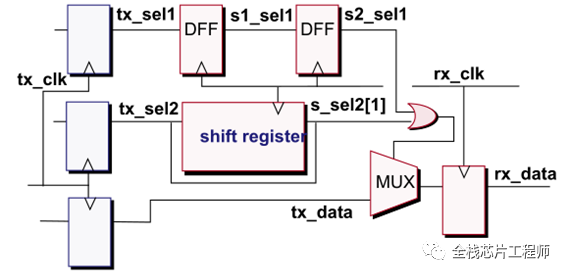

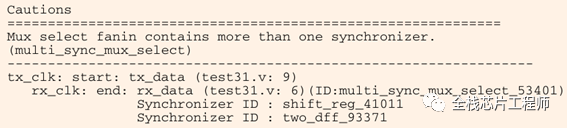

1.3 multi_sync_mux_select (DMUX)

MUX的sel端fan-in信号超过一组同步器,不推荐。通常MUX的sel端只能有一组同步器。

案例1:

<pre class="code-snippet__js" data-lang="properties">```

<span class="code-snippet_outer"><span class="code-snippet__attr">always</span> <span class="code-snippet__string">@(posedge rx_clk) begin</span></span>reg s1_sel1, s2_sel1;

<span class="code-snippet_outer"> <span class="code-snippet__attr">reg</span> <span class="code-snippet__string">[1:0] s_sel2;</span></span>

<span class="code-snippet_outer"> <span class="code-snippet__attr">s1_sel1</span> <span class="code-snippet__string"></span></span>s2_sel1

<span class="code-snippet_outer"> </span>s_sel2

<span class="code-snippet_outer"> </span>if (s_sel2[1] | s2_sel1)

<span class="code-snippet_outer"><span class="code-snippet__meta"> rx_data =<span class="code-snippet__string"> tx_data;</span></span></span>end

电路如下:

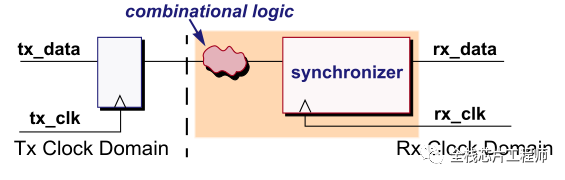

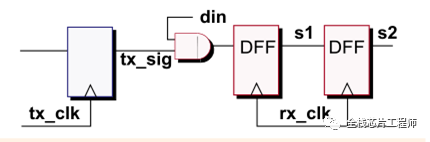

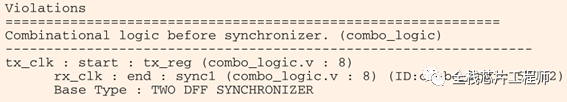

1.4 combo_logic

1.4.1 错误案列1

<pre class="code-snippet__js" data-lang="properties">```

<span class="code-snippet_outer"><span class="code-snippet__attr">always</span> <span class="code-snippet__string">@ (posedge rx_clk) begin</span></span>s1

<span class="code-snippet_outer"> <span class="code-snippet__attr">s2</span> <span class="code-snippet__string"></span></span>end

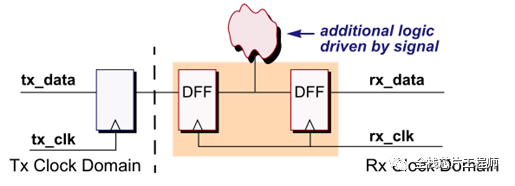

当然还有如下这种错误,除非additional logic全部是静态变量。

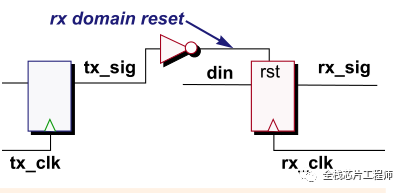

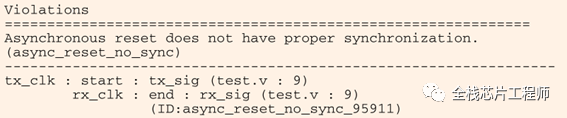

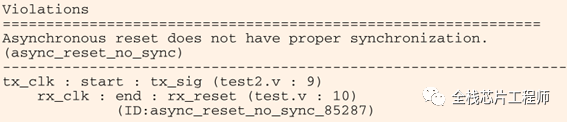

1.5 async_reset_no_sync(异步复位、同步撤离)

1.5.1 案列1

<pre class="code-snippet__js" data-lang="javascript">```

<span class="code-snippet_outer"><span class="code-snippet__comment">// Reset triggered by tx_clk</span></span>always @(posedge tx_clk)

<span class="code-snippet_outer">tx_sig </span>

<span class="code-snippet_outer"><span class="code-snippet__comment">// Unsynchronized reset used in</span></span>// Rx domain

<span class="code-snippet_outer">always @(posedge rx_clk,negedge tx_sig)</span>if (!tx_sig) rx_sig 1’b0;

<span class="code-snippet_outer"><span class="code-snippet__keyword">else</span> rx_sig </span>

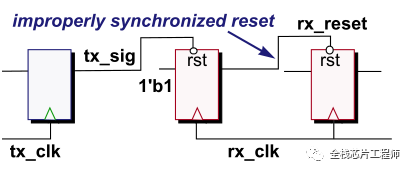

### 1.5.2 错误案列2

-

-

-

-

-

-

-

-

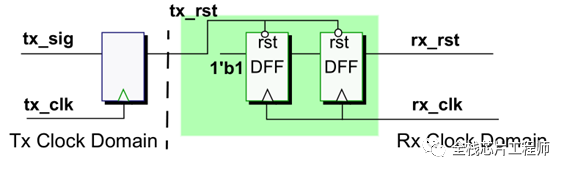

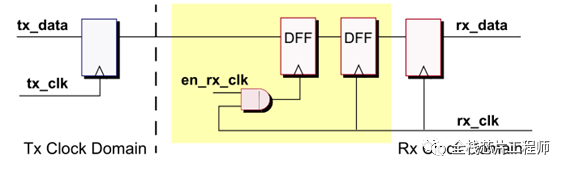

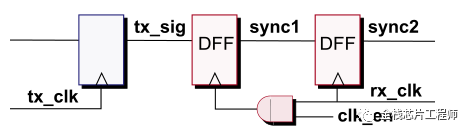

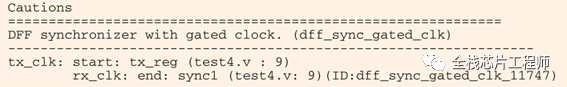

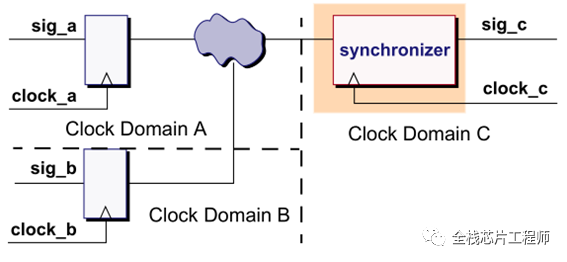

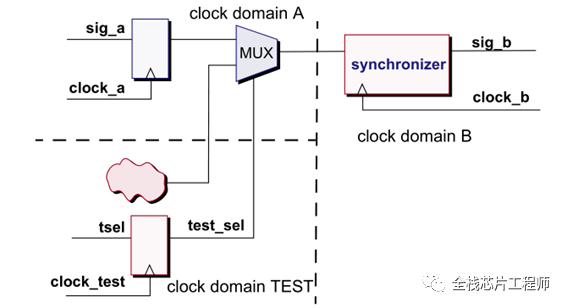

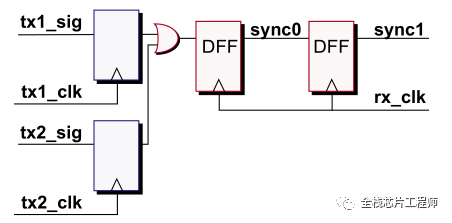

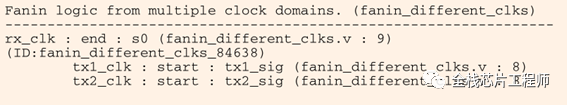

``` // Reset triggered by tx_clk `````` always @(posedge tx_clk) `````` tx_sig `````` // Improperly synchronized reset used `````` // in Rx domain `````` always @(posedge rx_clk,negedge tx_sig) `````` if (!tx_sig) rx_reset 1’b0; `````` else rx_reset 1’b1; ``` ```   正确的结构如下:  1.6 dff\_sync\_gated\_clk -------------------------  案列1,与门做时钟gating有毛刺,需要clock gating cell。 - - - - - - `````` gated clock expression `````` assign gclk = rx_clk & clk_en; `````` always @(posedge gclk) `````` sync1 `````` always @(posedge rx_clk) `````` sync2 ``` ```   1.7 fanin\_different\_clks -------------------------- 同步器的输入由两个异步时钟域的组合逻辑构成,如下图所示:(还有combo logic)  值得注意的是,如果sig\_a或者sig\_b中有一个信号是stable静态变量,那么上图结构的电路就不会被报fanin\_different\_clks或者combo\_logic错误。 假设有sig\_a、sig\_b、sig\_c三个信号及以上的fan\_in呢?抛开静态变量后, 若所有信号都是同一个时钟域,CDC错误类型就是combo\_logic; 若所有信号来自至少2个时钟域,CDC错误类型就是fanin\_different\_clks; 举个例子,如下图:  上图电路仍会报fanin\_different\_clks,但是电路确实是设计者的意图,我们只需要将TEST时钟域的test\_sel设置为常数0即可。 ### 1.7.1 案列1 - - - - - - - - `````` always @ (posedge tx1_clk) `````` tx1_sig `````` always @ (posedge tx2_clk) `````` tx2_sig `````` always @ (posedge rx_clk) begin `````` sync0 `````` sync1 `````` end ``` ```   时间不早了,暂写到这里,后续接着完善。 感谢阅读文章,如果文章有用,麻烦点个“在看”或转发分享。  转载:全栈芯片工程师

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:3419次2022-01-23 09:00:19

-

浏览量:4252次2022-02-20 09:00:18

-

浏览量:3317次2022-01-12 09:00:12

-

浏览量:3132次2022-01-13 09:00:13

-

浏览量:5292次2022-08-17 09:01:18

-

浏览量:9119次2021-01-09 02:07:52

-

浏览量:8083次2022-04-01 09:00:15

-

浏览量:11244次2021-01-17 00:16:33

-

浏览量:7353次2021-01-23 18:45:14

-

浏览量:13016次2021-01-02 00:02:19

-

浏览量:3597次2020-08-24 21:19:41

-

浏览量:14153次2020-12-07 00:58:01

-

浏览量:2975次2022-05-30 11:53:09

-

浏览量:3410次2020-11-27 10:06:38

-

浏览量:10091次2021-02-20 17:50:13

-

浏览量:45648次2020-12-12 19:46:11

-

浏览量:10132次2021-08-09 15:05:08

-

浏览量:7032次2022-03-26 09:00:12

-

浏览量:8375次2022-01-11 09:00:13

-

浏览量:2777次2020-07-03 18:27:11

更多相关专栏

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友