技术专栏

低通滤波器的FIR的设计

基于FPGA低通滤波器FIR的设计

1 滤波器的特征参数介绍

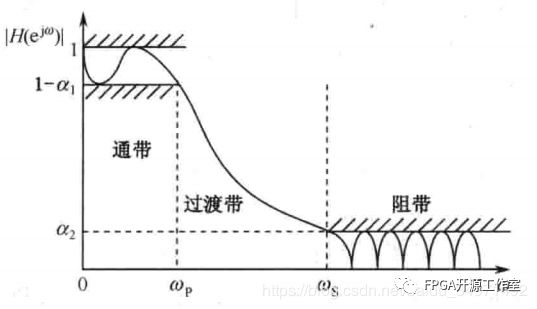

图1 低通滤波器特征参数 如图1所示,低通滤波器的通带截止频率为ωp ,通带容限为α1,阻带截止频率为ωs,阻带容限为α2。通带定义为|ω|≤ωp ,过渡带定义为ωp2 设计目标

要求:使用fir滤波器设计一个滤波器系数为15阶的低通滤波器,通带截止频率为1KHZ,采样频率为44.1khz。

3 matlab的设计验证

<pre code="" consolas="" courier="" inconsolata="" menlo="" monaco="" mono="" monospace="" pro="" rgb="" sans="" sans-serif="" sc="" source="" style="box-sizing: border-box;font-family: " yahei="">```

close all<br></br>clear all<br></br>clc<br></br> <br></br>%设计一个低通滤波器 采样频率为44.1khz, 截止频率为1khz<br></br> <br></br>FS = 44100; %HZ<br></br>fc = 1000;<br></br>N = 15;<br></br>Q = 16;<br></br> <br></br>%以采样频率的一半,对频率进行归一化处理<br></br>wn_lpf=fc*2/FS;<br></br>%采用fir1函数设计FIR滤波器<br></br>b_lpf=fir1(N-1,wn_lpf);<br></br> <br></br>%滤波系数进行量化<br></br>b_16=round(b_lpf/max(abs(b_lpf))*(2^(Q-1)-1));<br></br> <br></br>%求滤波器的幅频响应<br></br>m_lpf=20*log(abs(fft(b_lpf)))/log(10);<br></br>b16_lpf=20*log(abs(fft(b_16)))/log(10);<br></br>%设置幅频响应的横从标单位为Hz<br></br>x_f=[0:(FS/length(m_lpf)):FS/2]; <br></br> <br></br>%绘制单位脉冲响应<br></br>subplot(221);stem(b_lpf);xlabel('n');ylabel('h(n)');<br></br>title('低通滤波器的单位脉冲响应','fontsize',8);<br></br> <br></br>subplot(222);stem(b_16);xlabel('n');ylabel('h(n)');<br></br>title('低通滤波器的单位脉冲响应','fontsize',8);<br></br> <br></br>%绘制幅频响应曲线<br></br>subplot(223);plot(x_f,m_lpf(1:length(x_f)));xlabel('频率(Hz)','fontsize',8);ylabel('幅度(dB)','fontsize',8);<br></br>title('低通滤波器的幅频响应','fontsize',8);<br></br> <br></br>subplot(224);plot(x_f,b16_lpf(1:length(x_f)));xlabel('频率(Hz)','fontsize',8);ylabel('幅度(dB)','fontsize',8);<br></br>title('低通滤波器的幅频响应','fontsize',8);<br></br>

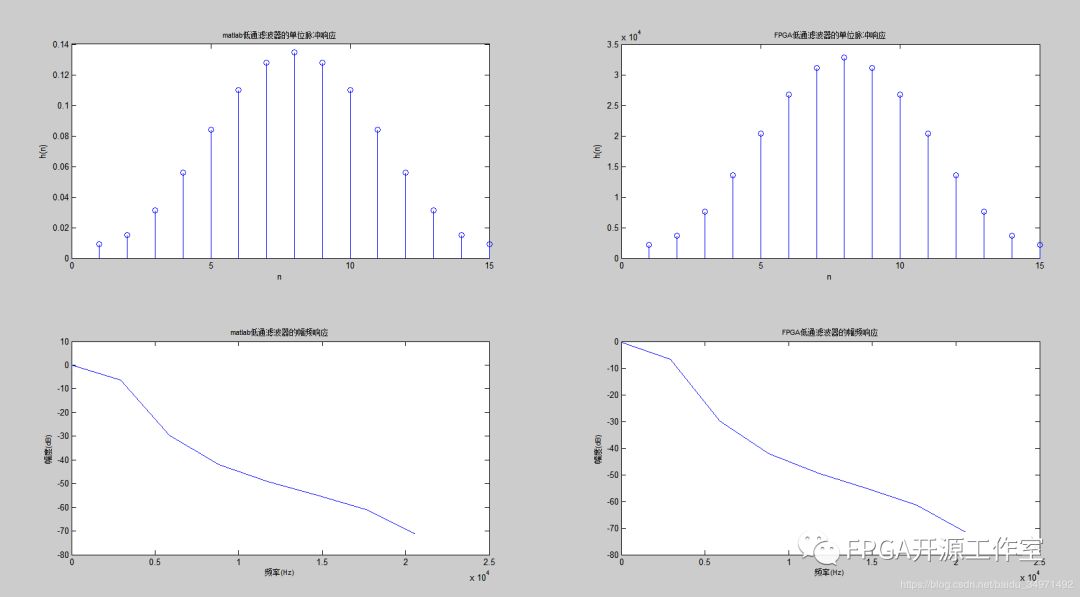

图2 低通滤波器的matlab单位脉冲响应和幅频响应4 FPGA信号发生器

-----------

为了验证低通滤波器,我们设计了测试验证的sin信号发生器。

wire \[17:0\] kfreq= (k产生1khz和5khz的sin波。

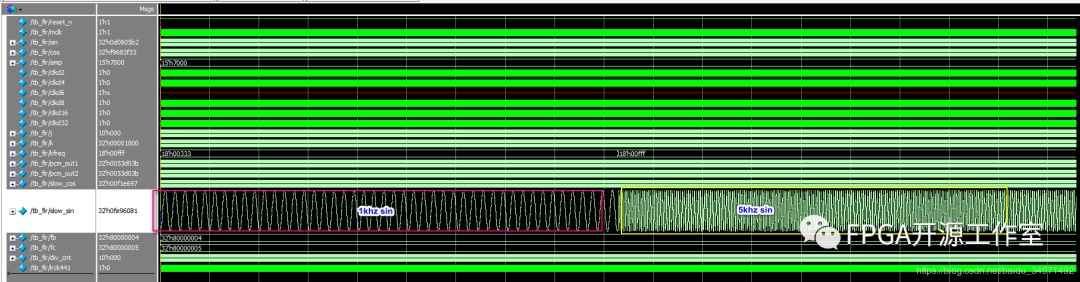

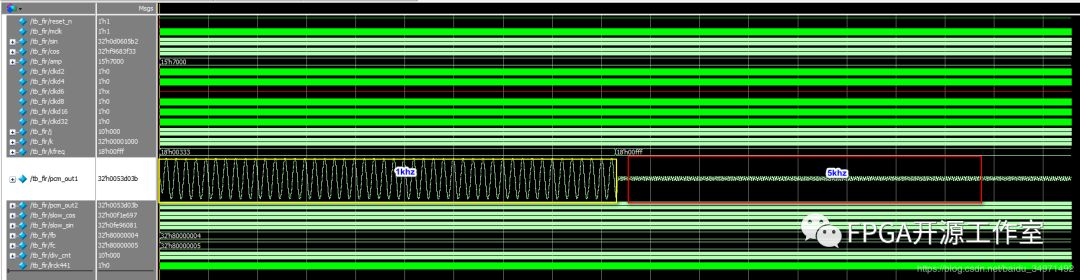

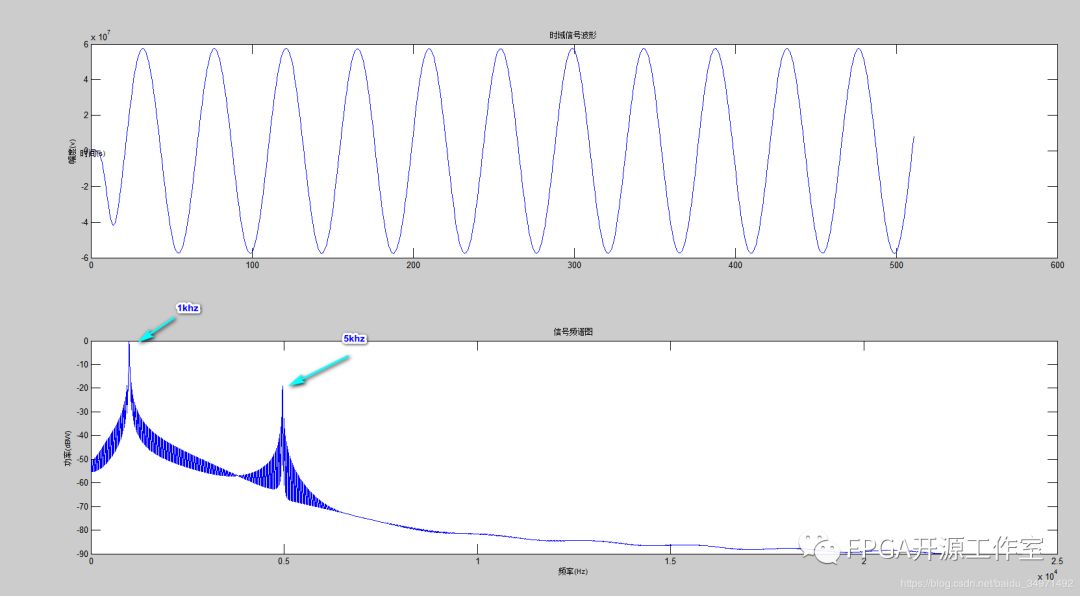

图3 信号发生器产生1khz和5khz的sin测试源测试源的FFT分析:

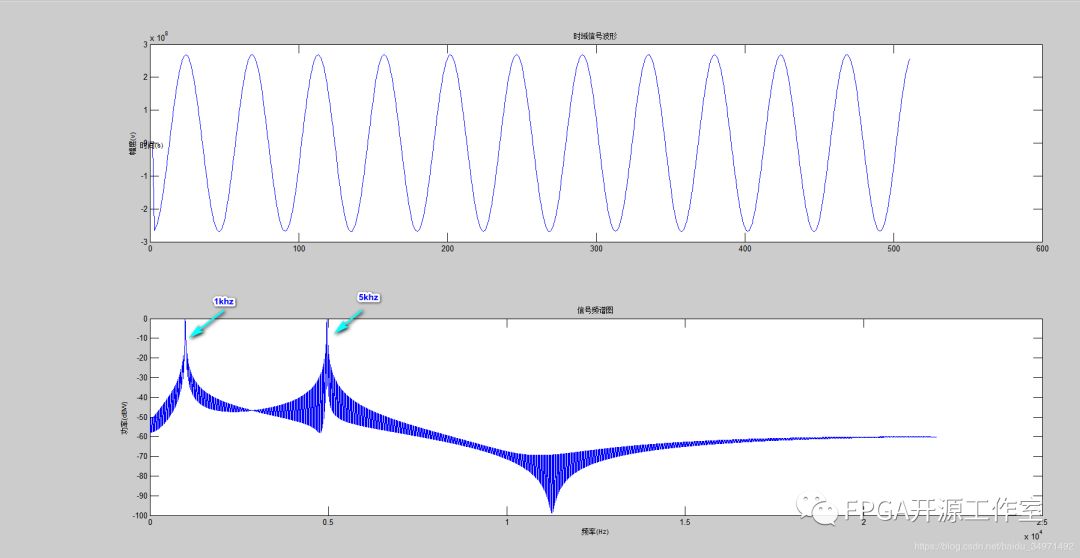

图4 测试源数据的matlab分析

由图4的频域图可知,测试源产生了1khz和5khz的sin。

5 FPGA的fir设计

------------

Fir滤波器verilog代码设计采取全并行模式。

``` `timescale 1ps/1ps

module fir1(

input mclk,//45.1584MHZ

input reset_n,

input signed[31:0] pcm_in,

output signed[31:0] pcm_out

);

localparam LAST_CYCLE = 1023;

reg [9:0] i;

reg signed [31:0] pcm1,pcm2,pcm3,pcm4,pcm5,pcm6,pcm7,pcm8,pcm9,pcm10,pcm11,pcm12,pcm13,pcm14,pcm15;

reg signed [47:0] pcm1_out,pcm2_out,pcm3_out,pcm4_out,pcm5_out,pcm6_out,pcm7_out,pcm8_out,pcm9_out,pcm10_out,pcm11_out,pcm12_out,pcm13_out,pcm14_out,pcm15_out;

reg signed [51:0] pcm_r;

wire signed [15:0] coeff1,coeff2,coeff3,coeff4,coeff5,coeff6,coeff7,coeff8,coeff9,coeff10,coeff11,coeff12,coeff13,coeff14,coeff15;

assign coeff1 = 2208;

assign coeff2 = 3631;

assign coeff3 = 7612;

assign coeff4 = 13576;

assign coeff5 = 20413;

assign coeff6 = 26727;

assign coeff7 = 31169;

assign coeff8 = 32767;

assign coeff9 = 31169;

assign coeff10 = 26727;

assign coeff11 = 20413;

assign coeff12 = 13576;

assign coeff13 = 7612;

assign coeff14 = 3631;

assign coeff15 = 2208;

assign pcm_out = pcm_r[51:20];

always @(posedge mclk or negedge reset_n) begin

if(!reset_n) begin

i 0;

pcm10;

pcm20;

pcm30;

pcm40;

pcm50;

pcm60;

pcm70;

pcm80;

pcm90;

pcm100;

pcm110;

pcm120;

pcm130;

pcm140;

pcm150;

pcm1_out0;

pcm2_out0;

pcm3_out0;

pcm4_out0;

pcm5_out0;

pcm6_out0;

pcm7_out0;

pcm8_out0;

pcm9_out0;

pcm10_out0;

pcm11_out0;

pcm12_out0;

pcm13_out0;

pcm14_out0;

pcm15_out0;

pcm_r 0;

end

else begin

i i + 1;

if(i == 0) begin

pcm1pcm_in;

pcm2pcm1;

pcm3pcm2;

pcm4pcm3;

pcm5pcm4;

pcm6pcm5;

pcm7pcm6;

pcm8pcm7;

pcm9pcm8;

pcm10pcm9;

pcm11pcm10;

pcm12pcm11;

pcm13pcm12;

pcm14pcm13;

pcm15pcm14;

end

if(i==1) begin

pcm1_out pcm1*coeff1;

pcm2_out pcm2*coeff2;

pcm3_out pcm3*coeff3;

pcm4_out pcm4*coeff4;

pcm5_out pcm5*coeff5;

pcm6_out pcm6*coeff6;

pcm7_out pcm7*coeff7;

pcm8_out pcm8*coeff8;

pcm9_out pcm9*coeff9;

pcm10_out pcm10*coeff10;

pcm11_out pcm11*coeff11;

pcm12_out pcm12*coeff12;

pcm13_out pcm13*coeff13;

pcm14_out pcm14*coeff14;

pcm15_out pcm15*coeff15;

end

if(i==2) pcm_r pcm1_out +pcm2_out+pcm3_out+pcm4_out+pcm5_out+pcm6_out+pcm7_out+pcm8_out+pcm9_out+pcm10_out+pcm11_out+pcm12_out+pcm13_out+pcm14_out+pcm15_out;

end

end

endmodule

``` ``` - - - - - - fpga实验modelsim仿真结果,从图5来看1khz几乎保持不变,而5khz波形幅度上被抑制了很多。  图5 modelsim fir实验结果时域波形 Matlab fft分析:  图6 matlab分析实验结果 由图2和图6对比,5khz经过滤波后的功率减小了20DB,图2与图5基本一致,fir的低通滤波器全并行设计成功。 感谢阅读,别走!点赞、关注、转发后再走吧  转载:全栈芯片工程师

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

点赞

收藏

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:18893次2021-01-21 11:45:55

-

浏览量:13470次2021-01-18 17:28:31

-

浏览量:18442次2021-01-18 13:46:39

-

浏览量:12551次2021-01-29 12:25:06

-

浏览量:24058次2021-01-29 16:50:41

-

浏览量:8838次2022-02-14 09:00:16

-

浏览量:4129次2021-01-18 17:57:51

-

浏览量:2239次2019-11-21 08:51:37

-

浏览量:7560次2021-01-20 08:36:19

-

浏览量:12461次2021-01-21 11:07:14

-

浏览量:2006次2019-09-18 16:32:09

-

浏览量:5822次2021-01-20 09:58:57

-

浏览量:9268次2021-01-20 09:27:42

-

浏览量:1062次2023-03-21 10:37:02

-

浏览量:2106次2019-11-27 16:00:08

-

浏览量:2928次2020-06-16 09:36:17

-

浏览量:5589次2019-11-09 09:37:38

-

浏览量:20207次2020-12-21 18:20:26

-

浏览量:4474次2021-01-07 15:03:29

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

david

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友