FPGA原型验证-时钟门控的替换

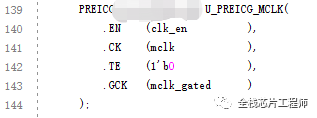

RTL设计、验证完成后,就该上菜FPGA原型验证了。将芯片RTL设计修改映射到FPGA上,没有FPGA工程师的话就得自己上啦。芯片ASIC设计中,不可避免会例化门级单元,比如CRG里:

一方面,ASIC设计里面可能存在很多个异步、同步/分频时钟,但FPGA可以将多个同步/分频时钟简单连接在一起用同一个时钟,甚至降频到10MHz进行仿真,因为我们只需要在FPGA上完成function功能验证。带Power domain(power gating cell/level shifter/isolation)的低功耗设计FPGA是无法模拟的,即低功耗设计是FPGA无法验证的,更何况ASIC芯片的时钟树和FPGA的时钟、复位是有质的不同的,因此,FPGA上完成function功能验证即可。

一方面,ASIC设计里面可能存在很多个异步、同步/分频时钟,但FPGA可以将多个同步/分频时钟简单连接在一起用同一个时钟,甚至降频到10MHz进行仿真,因为我们只需要在FPGA上完成function功能验证。带Power domain(power gating cell/level shifter/isolation)的低功耗设计FPGA是无法模拟的,即低功耗设计是FPGA无法验证的,更何况ASIC芯片的时钟树和FPGA的时钟、复位是有质的不同的,因此,FPGA上完成function功能验证即可。

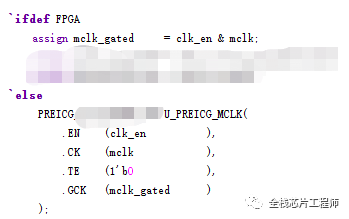

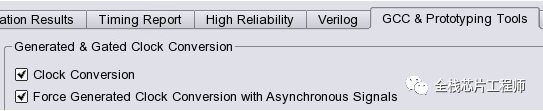

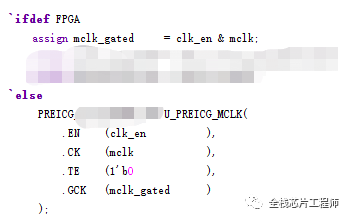

一方面,ASIC设计必然有大量门控时钟单元器件,当芯片RTL设计修改映射到FPGA上后,FPGA编译器肯定是不识别Foundry的STD Cell的,我们甚至可以直接assign clk_g = clk && en; (尽管存在毛刺风险),使用Synplify Premier综合时把下面选项勾上,类似于assign clk_g = clk && en的语句,工具会自动转为门控时钟,clk驱动信号,en变成CE这样的使能信号,功能不变。

对大部分时钟门控信号而言,FPGA验证时直接忽略掉门控,用assign clk_g = clk,时钟变成直通;当然也可以使用BUFGCE来严格实现FPGA的门控时钟,但是费时费力,不见收益。

另外,我们设计RTL时候,需要考虑到如何映射到FPGA上面,因此通常我们会用到以下的`ifdef:

所有verilog文件会用到的define定义,可以统一放在include.v里面,include.v里就一句:

所有verilog文件会用到的define定义,可以统一放在include.v里面,include.v里就一句:

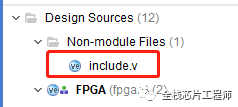

include.v添加到FPGA工程后,会发现include.v编译不进去,很多模块找不到`define FPGA的定义,造成Error报警。

解决办法:set Global include

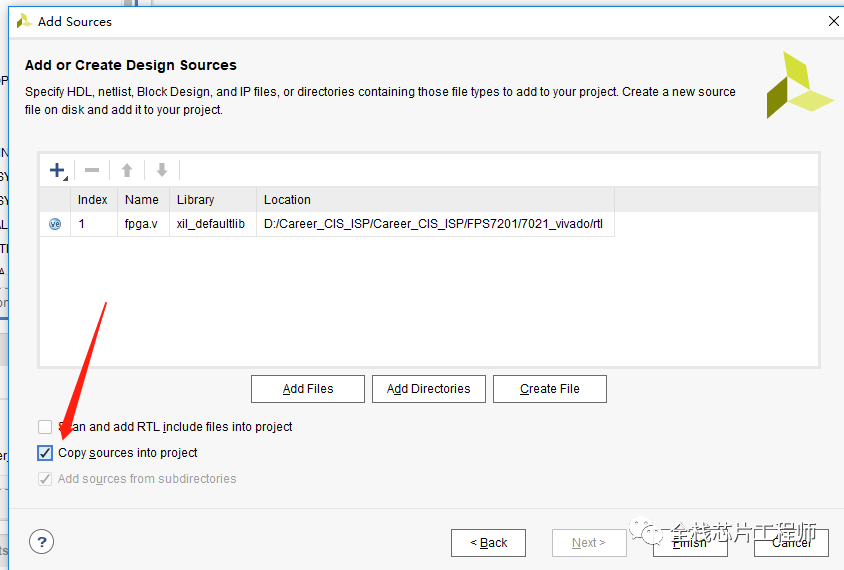

还有个容易出错的地方,改了代码老发现工具还用的老代码编译,可能是开了如下开关,造成RTL代码被编译到vivado自己的目录下了,所以当我改了新代码后,编译进去的还是它自己目录下的老代码。解决办法就是取消该选项,不要Copy sources into project。

感谢阅读文章,如果文章有用,麻烦点个“在看”或转发分享。

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:7252次2021-12-21 09:00:31

-

浏览量:4707次2022-08-17 09:01:18

-

浏览量:9311次2021-02-20 17:50:13

-

浏览量:7100次2022-04-01 09:00:15

-

浏览量:5843次2021-01-31 04:24:47

-

浏览量:5948次2021-02-21 21:08:27

-

浏览量:4180次2021-03-13 01:55:14

-

浏览量:5640次2021-02-09 14:27:57

-

浏览量:7148次2021-02-21 01:20:21

-

浏览量:1844次2019-04-26 11:42:22

-

浏览量:4442次2021-04-23 17:03:06

-

浏览量:1350次2023-04-11 15:24:20

-

浏览量:2637次2022-10-13 10:22:20

-

浏览量:6276次2020-03-18 10:41:44

-

浏览量:2589次2022-05-30 11:53:09

-

浏览量:5184次2021-03-14 01:58:15

-

浏览量:7897次2021-02-07 00:59:28

-

浏览量:1209次2022-05-28 10:31:03

-

浏览量:1046次2023-01-31 09:17:20

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友