不差钱的话,您会用激光雷达吗?

高阶自动驾驶的量产落地需要整个技术体系的进步。感知、决策、控制,每一个环节的软硬件都需要持续不断的创新。其中,后两者能否安全、准确地实现,取决于自动驾驶车辆的感知能力。

因此,智能电动汽车关于感知传感器的装载,也在不断增加和技术迭代。

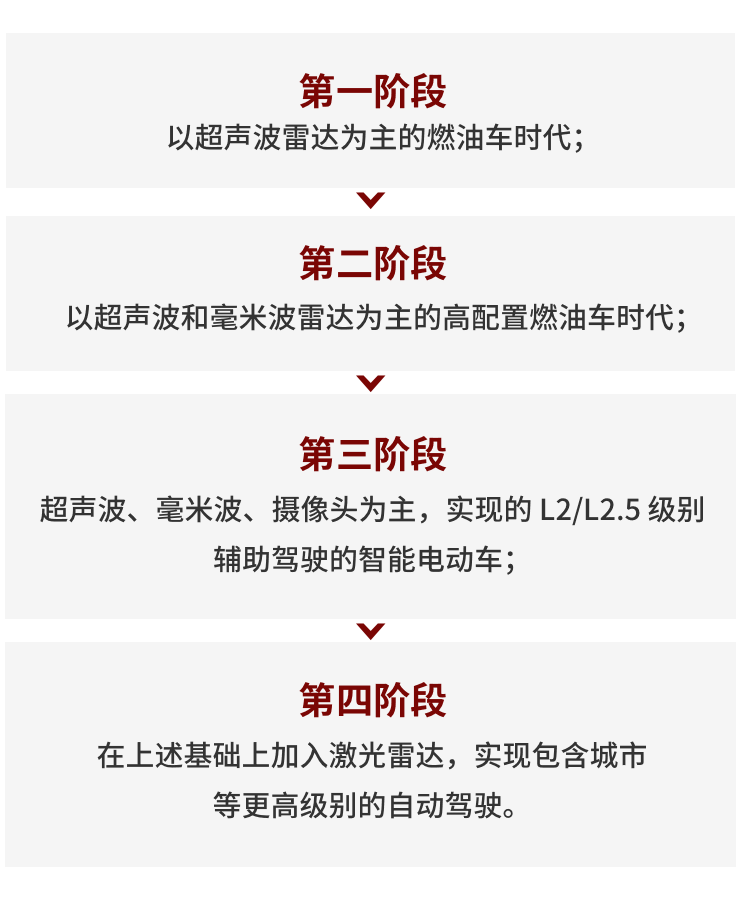

从传感器的形态和功能维度来看,可以分为几个阶段:

随着高级别自动驾驶对感知传感器需求的变高,传感器本身的技术迭代和技术创新也在加速。

随着高级别自动驾驶对感知传感器需求的变高,传感器本身的技术迭代和技术创新也在加速。

No.1

硬件竞争短期不会结束

在科技产品中,硬件是基础,为实现一些系统性的功能而存在。在自动驾驶系统中,感知传感器就像眼睛,让车辆能够丰富且更精准地感知真实环境。

如果把整个自动驾驶系统拆分来看,感知本身只是一套小系统存在,由物理硬件、软件算法、芯片组成。这三者之间的关系是:硬件识别到的数据,由感知算法解析,解析标定之后提交有用数据与其他传感器数据比对,通过整个自动驾驶计算平台计算得到答案后交给决策机构。过程中的每个步骤都会影响传感器性能。

在传感器识别模组上,想要感知更丰富的信息,就需要传感器处理芯片具备更高性能。而在现阶段,激光雷达几乎成了智能汽车感知传感器的必选项,因其具备诸多优势:

❶ 精确的距离/深度和速度测量;

❷ 空间分辨率 - 高分辨率 3D 对象特征化;

❸ 200 m+ 的检测距离;

❹ 为方位角和仰角提供宽视角( FoV )和角度分辨率。

相比大多数厂商采用的“视觉+雷达”方案,在高级别自动驾驶对传感器高精度需求的驱动下,激光雷达会迅速成为车企与自动驾驶企业的标配,推动市场迅速扩大。然而,随之而来的问题是:激光雷达的升级迭代能否满足需求?

11 月 25 日下午 13:30 ,Xilinx Adapt – 中国站迎来汽车与自动驾驶专场。

扫描下图二维码报名并观看直播👇

No.2

传感器技术迭代缓慢

很多人将激光雷达等传感器落地和迭代慢,归结于机械结构以及光学组件升级慢。但这背后还有一个核心原因——专用芯片。

高性能传感器对芯片以及整个计算平台的性能有着极高要求,通常有几个主要指标:

算力:

激光雷达需要高算力,用于 3D 点云的高数据速率图像处理,3D 点云由每秒超过 100 万个数据点构成,数据量远超摄像头和其他雷达传感器。

高可扩展性:

未来传感器的融合,需要芯片架构具有非常强的拓展性。以支持运行不同软件,而且不同技术体系的之间需要进行复杂数据的计算。

性能与低功耗:

要做到限制成本与传感器模块尺寸以满足热管理要求。

低时延和动态数据吞吐量:

处理数据的延迟越低,越能够降低执行机构的执行时间,从而降低危险。

算法匹配:

当前芯片算法既要满足大数据量的计算,也要满足 AI 边缘算法需求。

左右滑动查看更多指标

目前最大的挑战在于,市场上的激光雷达硬件、深度学习算法软件尚未形成产业规模,也就是标准的通用型产品。因此,使用专用的 ASSP/ASIC 架构芯片效率并不高。在此情况下,芯片的灵活性就显得更加重要。

也正因如此,FPGA 处理平台正在被大规模应用。从结果来看,未来基于 FPGA 架构的芯片可能会更受制造商青睐。

No.3

基于 FPGA 的方案正跻身主流

针对激光雷达,FPGA 可以在众多方面提供助力,如灵活性、自适应能力、低时延、高吞吐量、快速上市进程等。其允许工程师更改内部电路的特性,则使汽车激光雷达系统能响应不断演进的设计与性能要求。凭借这些优势,FPGA 解决方案正跻身投产汽车激光雷达处理应用的主流。

截至目前,赛灵思在汽车电子领域的累计出货量已达 2.05 亿片,其中 8000 万片用于ADAS 领域。仅去年一年,赛灵思在汽车行业的出货量就接近 2000 万片器件。

面向汽车市场,赛灵思可以提供从 28 nm 工艺的 FPGA、Zynq SoC,16 nm 的 Zynq UltraScale + MPSoC 7EV 和 11 EG,以及 7nm 工艺的 Versal ACAP。在芯片制造行业,这是一条又宽又深的护城河。

车规级固态激光雷达已量产

11 月 25 日下午 13:30 ,Xilinx Adapt – 中国站汽车与自动驾驶专场,将围绕 FPGA 如何赋能激光雷达、毫米波雷达、以及自动驾驶域控制器等话题展开。

届时,赛灵思技术专家、一径科技研发副总裁以及苏州豪米波公司总工程师,将从技术角度深度分析相关技术具体应用。

扫描下方二维码,即刻报名吧👇

转载:赛灵思

- 分享

- 举报

暂无数据

暂无数据-

浏览量:1819次2019-12-13 18:21:20

-

浏览量:2561次2018-08-21 10:46:54

-

浏览量:1811次2019-12-25 15:37:50

-

浏览量:13609次2020-10-14 09:53:18

-

浏览量:3635次2020-03-19 10:10:20

-

浏览量:1684次2018-01-29 18:18:28

-

浏览量:2504次2020-01-08 11:20:32

-

浏览量:4854次2020-02-21 12:02:55

-

浏览量:1817次2018-08-03 00:49:53

-

浏览量:2619次2018-10-30 21:28:43

-

浏览量:1745次2018-06-04 15:06:13

-

2020-12-02 12:20:51

-

浏览量:2774次2020-03-20 09:30:35

-

浏览量:1959次2019-08-21 15:24:40

-

浏览量:3517次2020-03-25 10:02:47

-

浏览量:1207次2023-02-15 16:30:07

-

浏览量:3061次2019-06-24 14:21:28

-

浏览量:2151次2020-02-27 10:54:30

-

浏览量:3078次2020-04-17 11:58:37

-

253篇

- 高速串行总线设计基础(十)常用MGT协议简介以及自定义协议示例

- Xilinx 携手三星推出业界首款灵活应变的计算存储驱动器

- XDF(美洲站)首站告捷,名企云集,自适应技术全面开花 —— 期待 12 月份亚洲站

- FPGA逻辑设计回顾(3)多比特信号上升沿检测的设计方式与陷阱?

- FPGA的设计艺术(11)FPGA的构建过程

- 高速串行总线设计基础(七)揭秘SERDES高速面纱之时钟校正与通道绑定技术

- FPGA的设计艺术(30)FPGA硬件逻辑调试刍论

- FPGA逻辑设计回顾(5)多比特信号的CDC处理方式之MUX同步器

- FPGA的设计艺术(14)使用函数和任务提升逻辑的可重用性

- FPGA零基础学习:数字电路中的数字表示

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友