芯片设计之CDC异步电路(二)

上文芯片设计之CDC异步电路(一)对比讲述了异步电路在前仿真中的行为与实际芯片的行为区别,本文继续讲几种常用的异步电路处理。

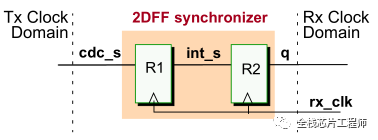

(一)单bit信号同步器最经典的2DFF 1-bit同步器如下,下图结构通常用于单bit控制信号的异步处理:

绝大数情况下,当第一个寄存器R1进入亚稳态后,在第二级寄存器R2采样R1的输出前,R1的输出已经能稳定在0或1。

注意:

- cdc_s信号必须做到glitch free,也就是我们通常说的寄存输出;

- int_s信号链路禁止组合逻辑,其本质也是杜绝glitch的出现。

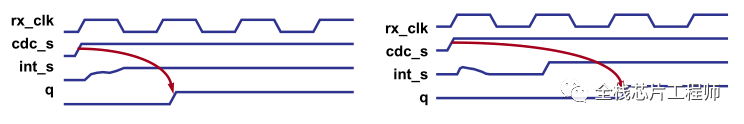

偏执狂的IC designer肯定会问,第一级寄存器R1的行为到底是啥样子的?由于cdc_s信号是Tx clock Domain,而R1寄存器的采用时钟是Rx clock Domain,当Rx clock采样时,若cdc_s正好跳变(不满足setup/hold),那么就会出现如下两种情况,而前仿真是无法仿真出下图2种行为的(具体见芯片设计之CDC异步电路(一)一文)。

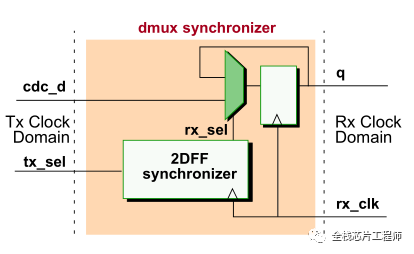

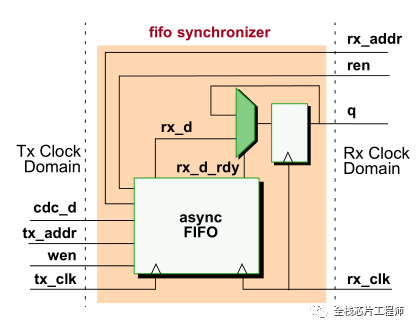

**(二**)DMUX同步器两级寄存器(先进工艺要求三级)的同步器通常用于控制信号的异步处理,但是data bus的异步处理呢?我们可以采用DMUX结构。 注意:

注意:

- tx_sel、rx_sel有效时,cdc_d数据总线必须保持稳定;

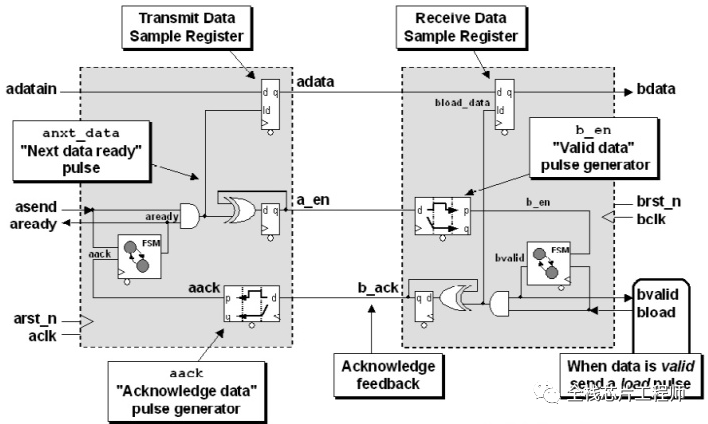

***(三**)**握手处理*源时钟域先将数据发送到总线上,并给出一个valid信号,而目标时钟域同步valid信号后,若valid信号为高电平则采样总线数据,并返回一个ready信号给源时钟域。源时钟域再次同步该ready信号,若ready信号为高,则代表一次握手成功,数据传输完毕,开始进行下一次数据传输。采用握手机制可以保证异步multi-bit数据传输不出现错误,但由于需要等待握手的完成再传输数据,因此传输效率较低。

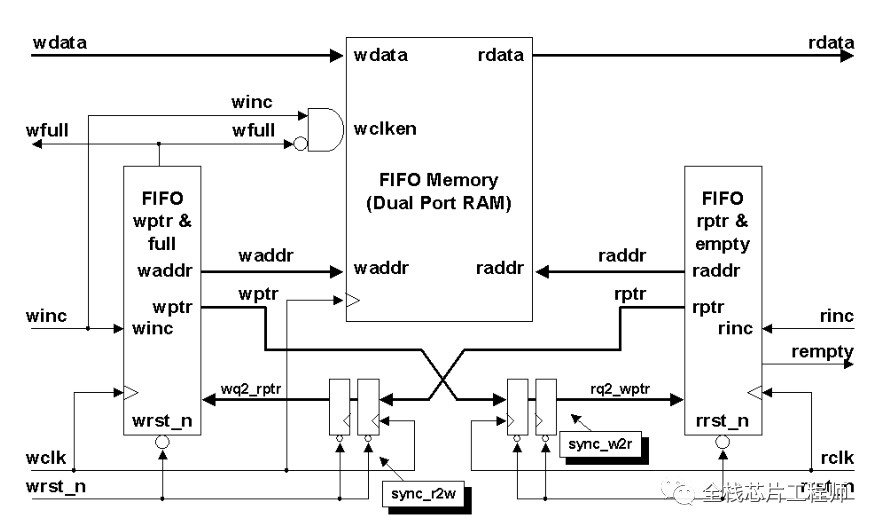

***(四)**异步FIFO*老生常谈的异步FIFO,其本质是采用格雷码,在地址连续的情况下,其对应格雷码每个周期只变化1bit,因此可以直接异步采样。

注意:

- FIFO的overflow、underflow问题;

- tx_addr是连续的,即地址hamming distance是1;

-

FIFO深度须2^n;

经典的FIFO结构如下:

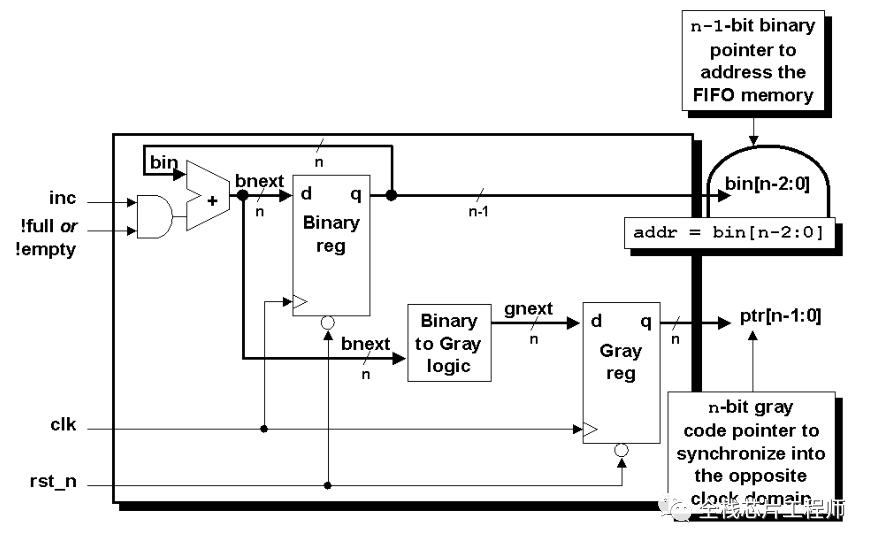

核心电路:是将FIFO读写地址指针的二进制码转成格雷码,方便同步器打两拍传递到对向时钟域去做空满判断。

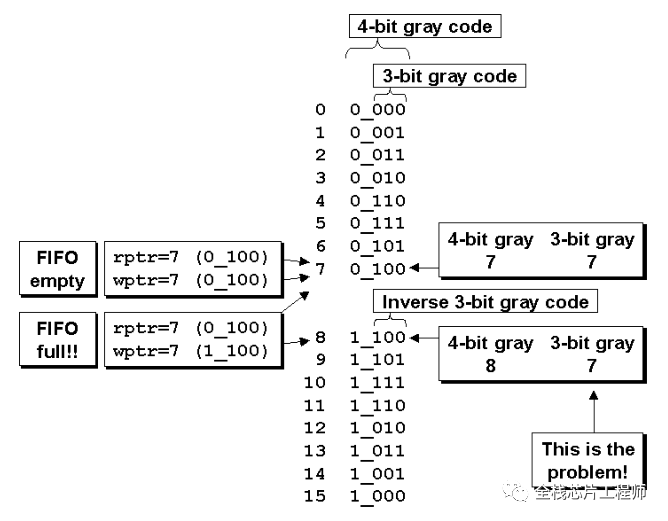

空满判断:为了区别空满,我们增加1bit的地址(MSB),我习惯直接用Gray码比较读写指针判定空满:

- 当Gray码读写指针完全相等时,FIFO空;

-

当Gray码读写指针最高2bit相反,其余bit相同时,FIFO满;通常二进制码比较空满是:最高bit不同,其余bit相同,则FIFO满,而格雷码则不同哈。

不能继续熬夜了,先睡觉了,抽空接着写。

感谢阅读文章,如果文章有用,麻烦点个“在看”或转发分享。

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:2765次2022-01-13 09:00:13

-

浏览量:3877次2022-02-20 09:00:18

-

浏览量:3008次2022-01-23 09:00:19

-

浏览量:4728次2022-08-17 09:01:18

-

浏览量:8710次2021-01-09 02:07:52

-

浏览量:7141次2022-04-01 09:00:15

-

浏览量:5523次2021-12-21 09:00:19

-

浏览量:10783次2021-01-17 00:16:33

-

浏览量:6991次2021-01-23 18:45:14

-

浏览量:12454次2021-01-02 00:02:19

-

浏览量:2608次2022-05-30 11:53:09

-

浏览量:9363次2021-02-20 17:50:13

-

浏览量:3169次2020-08-24 21:19:41

-

浏览量:3641次2020-12-02 09:57:51

-

浏览量:3054次2020-11-27 10:06:38

-

浏览量:5173次2022-01-02 09:00:13

-

浏览量:16780次2020-12-05 09:32:54

-

浏览量:6389次2022-03-26 09:00:12

-

浏览量:42149次2020-12-12 19:46:11

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友