EDA 工具迎来机器学习时代

Ramine Roane

Ramine Roane

赛灵思软件与 AI 产品管理副总裁

赛灵思近来在 EDA 领域取得的重大发展,将对 FPGA 设计生产力产生切实影响。

赛灵思近来在 EDA 领域取得的重大发展,将对 FPGA 设计生产力产生切实影响。

EDA 面临重重挑战

长期以来,EDA 面临着各种挑战:器件数量越来越多、设计越来越复杂。尽管摩尔定律逐步放缓,但在过去 20 多年间,FPGA 晶体管数量呈现的指数级增长丝毫未减。

赛灵思利用堆叠硅片互联等技术,在异构集成方面取得了领先地位,同时还增加了 ARM 处理器子系统、AI 引擎或众多连接块,如 NOC 连接块和其它硬件块,并以此取得了骄人成绩。然而,鱼与熊掌不能兼得。性能上带来了巨大优势,而设计简化性、编译时间和结果质量( QoR )往往需要做出妥协。

这也就导致了设计方法的多种多样,其丰富程度甚至超越了宇宙中原子的数量。换句话说,玩 EDA 比下围棋难得多。更糟糕的是,优化算法本身为多项式,会随设计大小呈指数级浮动。因此,通常在 EDA 中面临的取舍是,在编译时间和 QoR 之间进行抉择。

机器学习带来新曙光

AI 正推动编译速度与质量进入新阶段

众所周知,围棋、自主驾驶、RNA 翻译转化、蛋白质折叠等难题,现在都能通过机器学习求解。所谓机器学习,就是在大数据中寻找模式。在处理 PB 级数据时,**机器学习显然比人类做得更好。**

赛灵思和 EDA 公司都拥有着数十年的数据,目前也都在借助 AI 充分利用这些数据。然而在 EDA 公司中,采用机器学习的一项重要挑战是缺乏在特定领域更专业的技术积累。过去几年中,赛灵思大量投资于机器学习领域,不断获取 AI 技术与人才。

现在,赛灵思及整个学术界在 EDA 领域完成了大量 AI 学术研究,涵盖了 AI 技术在综合、平面规划、布置路由、静态时序分析等领域的应用。研究显示,与传统 EDA 算法相比,QoR 比最初提高了 10%。机器学习不仅有助于提高 QoR,还能缩短编译时间,并根据设计模式预测和加快设计收敛策略。

为了缩短编译时间,赛灵思在团队设计方面加倍投入。今年,新引入的特性可实现从系统设计到实现再到部署的层级设计。

在系统层面强化了 IP Integrator,使团队能够构建层级子系统。

在实现方面,新加入的特性支持真正与环境无关的编译和时序收敛。

系统其余部分运行时,部署以毫秒为单位一次性释放流程,以交换加速功能。

与环境无关的编译可显著加速时序收敛,因为每个团队只需完成其子系统的收敛,就能确保全面的设计聚合。

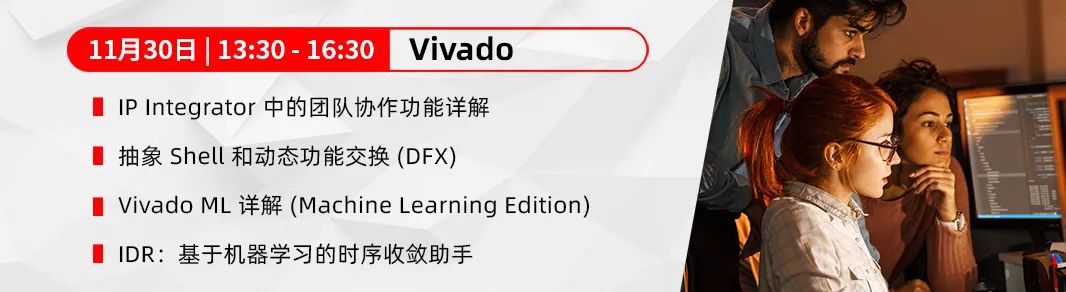

11 月 30 日 13:30,在 Xilinx Adapt - 中国站线上技术大会特别设立的开发者专场中,赛灵思资深软件工具专家高亚军( Lauren Gao ),将现场详解本文所提到的所有新功能及设计方法。点击下方图片即可预约报名。

Vivado ML

以最前沿机器学习优化加速设计

今年 6 月,赛灵思发布了 Vivado® ML 版。它是业界首个基于机器学习优化算法,以及先进的、面向团队协作的设计流程打造的 FPGA EDA 工具套件,借助基于机器学习的算法将 QoR 平均提升了 10%,并以模块化设计将编译时间平均缩短了 5 倍。

在 Vivado ML 中,赛灵思引入了 Abstract Shell (抽象外壳)概念,允许用户在系统内定义多个模块,以增量和并行方式进行编译。这种方法较之传统的全系统编译,能将平均编译时间加快 5 倍,最多高达 17 倍。

在 Vivado ML 中,赛灵思引入了 Abstract Shell (抽象外壳)概念,允许用户在系统内定义多个模块,以增量和并行方式进行编译。这种方法较之传统的全系统编译,能将平均编译时间加快 5 倍,最多高达 17 倍。

此外,Vivado ML 还改善了与 Vivado IP Integrator 之间协作设计,使模块化设计可以利用全新“模块设计容器( Block Design Container )”功能实现。而动态功能交换( DFX )等赛灵思独特的自适应特性,则可在运行时动态远程加载定制硬件加速器,让芯片资源得到更有效的利用。

11月30日-12月7日,Xilinx Adapt - 中国站将迎来“开发者系列”专场活动,11月30日 Vivado 专场日程安排如下:

点击下方图片锁定座位吧!

转载:赛灵思

- 分享

- 举报

暂无数据

暂无数据-

浏览量:3074次2023-04-19 09:16:00

-

浏览量:2586次2018-02-20 00:28:57

-

浏览量:915次2023-11-10 11:30:56

-

浏览量:4838次2021-04-09 16:28:04

-

浏览量:1674次2023-04-21 09:00:28

-

浏览量:1770次2018-03-08 19:41:39

-

浏览量:1138次2023-07-27 11:16:16

-

浏览量:6011次2021-02-20 17:09:58

-

浏览量:6167次2021-02-28 15:11:37

-

浏览量:3716次2019-09-18 22:22:32

-

浏览量:2666次2023-08-28 14:50:41

-

浏览量:2333次2018-10-15 21:38:57

-

浏览量:5674次2021-06-07 09:28:15

-

浏览量:3725次2017-12-08 21:44:23

-

浏览量:197次2023-08-15 22:50:27

-

浏览量:4855次2023-09-04 14:32:32

-

浏览量:1628次2023-01-05 17:44:00

-

浏览量:919次2023-07-05 10:16:37

-

浏览量:2213次2022-11-30 09:49:56

-

253篇

- 开启 5G NR 海量连接时代,第二代 Xilinx 单芯片射频平台现已量产

- MLPerf:主流机器学习平台效率大 PK

- 高速串行总线设计基础(九)揭秘SERDES高速面纱之线路均衡与误码检测

- 高速串行总线设计基础(八)揭秘SERDES高速面纱之CML电平标准与预加重技术

- FPGA的设计艺术(10)HDL是软件还是硬件?

- 高光时刻: Xilinx 自适应计算平台 和 Vitis 登上世界互联网领奖台

- SmartNIC 与普通的 NIC 有哪些显著性差异?

- FPGA逻辑设计回顾(11)FPGA以及PC中的RAM与ROM

- 让您的创新永不落伍: 赛灵思开发者大会(XDF)报名开启!

- FPGA的设计艺术(30)FPGA硬件逻辑调试刍论

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友