借助ROS 2实现软件定义自适应机器人

作者:Víctor Mayoral-Vilches,赛灵思机器人系统架构师;GiulioCorradi,赛灵思工业、视觉、医疗与科学首席架构师>

FPGA 能够自适应生成定制计算架构,以前所未有的灵活性、更短的设计周期、更低的开发成本,助力各类机器人应用。

01

机器人是一种**“系统集成艺术”**

机器人是一种复合系统,它由感知周边环境的传感器、根据感知采取行动的致动器和负责处理数据的计算构成,从而对其应用做出连贯一致的响应。在很大程度上,机器人技术是一种系统集成的艺术,在软件和硬件方面皆是如此。

以往的研究揭示,机器人领域中多达 70% 的资源被用于集成,而不是用于开发最终应用。直到最近,随着较低端的工业机器人走向大规模普及化,机器人公司才开始在硬件基础上着重软件开发。

尽管如此,机器人仍然是高度专业化的系统,旨在以高可靠性和高精度执行一系列任务。**因此,机器人内部的硬件和软件能力之间的关系十分重要。大多数机器人通过内部网络交换信息并满足时序要求。从这种意义上来讲,机器人属于时间敏感型网络。**

02

选择“适合的计算平台”

机器人系统的机载资源通常非常有限,如存储器、I/O 和磁盘或计算功能,会阻碍系统集成进程,使之难以满足非结构化、动态和不断变化环境的实时性要求。随着机器人内部网络安全的发展,这一点更是如此,因为它经常在使用寿命方面对机器人提出新要求,需要修改机器人的逻辑,从而对实时环路产生影响

正因如此,为机器人系统选择合适的计算平台至关重要。该平台既要简化系统集成、符合功耗限制,也要能够适应机器人应用不断变化的需求。

打造**自适应机器人**

Building Adaptive Robots

自适应机器人是指那些能够成功应对新状况的机器人。一台能够称得上“自适应”的机器人,必须具备以下三大特性其中之一。满足全部三项特性的机器人,可视为“完全自适应机器人”。

自适应机器人是指那些能够成功应对新状况的机器人。一台能够称得上“自适应”的机器人,必须具备以下三大特性其中之一。满足全部三项特性的机器人,可视为“完全自适应机器人”。

自适应机器人基本要求

自适应机器人基本要求

自适应计算是自适应机器人的第三项基本特性。对于机器人而言,主要指机器人能够在运行过程中适配其计算系统的一个或多个属性(如确定性、功耗或吞吐量)。在此方面,FPGA 正是实现自适应计算的理想技术,因其兼具通用性和强大功能,同时效率高、成本低。

在 FPGA 上不仅可以实现其他处理架构,还可以实现并行处理。因此,FPGA 可以用于处理几乎任何机器人内部的任务。另一方面,FPGA 能够针对每一种机器人应用的需求,专门定制数据路径宽度和寄存器长度。

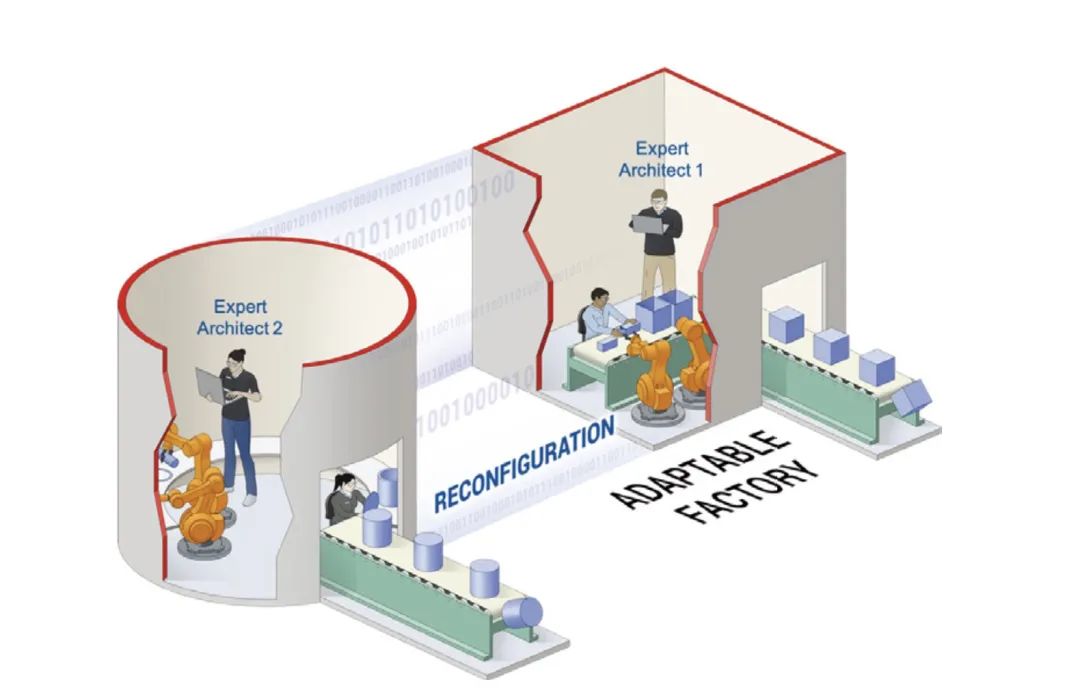

如果说,CPU 和 GPU 是工人按照顺序依次将输入加工成输出的车间,那么,FPGA 就是灵活的自适应工厂,能够针对手中的具体任务定制创设装配线和传送带。

FPGA 的工业类比

FPGA 的工业类比

Kria SOM 是机器人的理想计算平台

传统的机器人软件开发,是基于预先定义的架构和约束条件,在给定机器人的 CPU 中进行功能编程。一旦机器人遇到适配需求,就会导致复杂的系统集成操作。然而,如果使用 FPGA,构建机器人行为就是为解决任务的架构编程。机器人架构师可以纯粹从软件创建自己的硬件设计,并通过各种平台完成交付。

左右滑动查看三种自适应计算解决方案

2021 年,赛灵思推出了自适应 Kria 系统模块(SOM)。作为机器人专家与 FPGA 技术交互的三种途径之一,采用 Kria SOM 将预装配电路板插入定制的承载电路板,能够帮助硬件工程师加快产品开发速度,避免因计算平台分心,并集中注意力创造增值。

2021 年,赛灵思推出了自适应 Kria 系统模块(SOM)。作为机器人专家与 FPGA 技术交互的三种途径之一,采用 Kria SOM 将预装配电路板插入定制的承载电路板,能够帮助硬件工程师加快产品开发速度,避免因计算平台分心,并集中注意力创造增值。

如需了解 Kria SOM ,以及 TSN(时间敏感型网络)的专家介绍,欢迎点击下方图片,报名参加 Xilinx Adapt - 中国站,全中文讲解与问答。

赛灵思最新白皮书《自适应计算在机器人领域的应用》,围绕 ROS 2 机器人专家的视角讲解自适应计算,提出了一种能够让 FPGA 在 ROS 2 生态系统中起主要作用的架构,适用于多种平台和技术且便于移植,为机器人专家充分运用自适应计算、实现软件定义硬件铺平了道路。完整白皮书请点击“阅读原文”获取。

赛灵思最新白皮书《自适应计算在机器人领域的应用》,围绕 ROS 2 机器人专家的视角讲解自适应计算,提出了一种能够让 FPGA 在 ROS 2 生态系统中起主要作用的架构,适用于多种平台和技术且便于移植,为机器人专家充分运用自适应计算、实现软件定义硬件铺平了道路。完整白皮书请点击“阅读原文”获取。

推荐阅读

Xilinx Adapt 技术大会中国站,来了!

转载:赛灵思

- 分享

- 举报

暂无数据

暂无数据-

2023-04-14 13:44:09

-

浏览量:5446次2019-12-10 11:02:13

-

浏览量:882次2023-08-30 09:20:09

-

浏览量:5863次2020-11-25 09:49:19

-

浏览量:3032次2020-11-18 14:34:59

-

浏览量:906次2023-07-20 10:57:55

-

浏览量:9584次2020-12-10 18:35:14

-

浏览量:5392次2017-12-13 22:25:35

-

2023-04-14 13:55:03

-

浏览量:2218次2018-01-27 13:18:48

-

浏览量:5445次2020-07-30 18:42:39

-

浏览量:930次2023-04-14 14:42:21

-

浏览量:1867次2022-01-17 09:01:39

-

浏览量:700次2023-08-24 15:30:23

-

浏览量:2225次2022-01-05 09:00:22

-

浏览量:790次2023-08-24 10:03:33

-

浏览量:1640次2023-04-14 14:37:29

-

浏览量:470次2023-09-05 09:12:28

-

浏览量:1430次2023-03-23 10:43:10

-

253篇

- 【转载】Display Port概述以及应用

- FPGA逻辑设计回顾(13)RAM以及ROM的IP核定制以及关键参数

- FPGA的设计艺术(9)FPGA开发技巧与工程管理

- MLPerf:主流机器学习平台效率大 PK

- FPGA的设计艺术(6)STA实战之SmartTime时序约束及分析示例(I)

- SmartNIC 架构:向加速器转型以及 FPGA 占据主导地位的理由

- FPGA的设计艺术(18)如何使用Verilog中的数组对存储器进行建模?

- 12G-SDI高清视频开发案例,让4K视频采集更便捷!基于Xilinx MPSoC高性能平台

- FPGA的设计艺术(15)逻辑设计及仿真利器之各式各样的循环

- FPGA 并非软件开发,一文看懂 FPGA 重点知识

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友