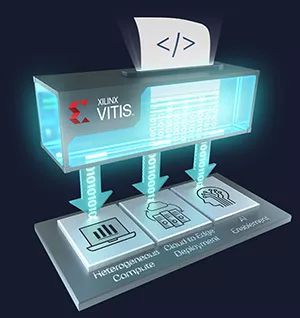

突破软硬壁垒,解锁全员创新 —— Xilinx 隆重发布 Vitis 统一软件平台

今天,赛灵思大中华区销售副总裁唐晓蕾 ( Maria) 及赛灵思软件和人工智能高级经理罗霖( Andy )在北京隆重发布里程碑式的 Vitis™ 统一软件平台,以“突破软硬壁垒,解锁全员创新” 为主题,揭开赛灵思通过软件革新,解锁软件开发者的硬件加速壁垒,将赛灵思独特的自适应计算能力带给全员开发者的新篇章。

图:唐晓蕾通过赛灵思从器件到平台转型战略和产业发展趋势介绍 Vitis 发布的行业意义。

图:唐晓蕾通过赛灵思从器件到平台转型战略和产业发展趋势介绍 Vitis 发布的行业意义。

图:罗霖详细介绍 Vitis 技术细节、功能、资源及发展路线。

【Vitis】这是一款 统一软件平台,可以让包括软件工程师和 AI 科学家在内的广大开发者都能受益于硬件灵活应变的优势。

历经五年、投入总计 1000 个人工年而打造,Vitis 统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思硬件架构。此外,Vitis 平台不限制使用专有开发环境,而是可以集成到通用的软件开发工具中,并利用丰富的业经优化的开源库,使开发者能够专注于算法的开发。

历经五年、投入总计 1000 个人工年而打造,Vitis 统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思硬件架构。此外,Vitis 平台不限制使用专有开发环境,而是可以集成到通用的软件开发工具中,并利用丰富的业经优化的开源库,使开发者能够专注于算法的开发。

Vitis 独立于 Vivado™ 设计套件,后者仍然继续为希望使用硬件代码进行编程的用户提供支持。但是,Vitis 也能够通过将硬件模块封装成软件可调用的函数,从而提高硬件开发者的工作效率。

Vitis 独立于 Vivado™ 设计套件,后者仍然继续为希望使用硬件代码进行编程的用户提供支持。但是,Vitis 也能够通过将硬件模块封装成软件可调用的函数,从而提高硬件开发者的工作效率。

随着计算需求呈指数级增长,工程师与科学家常常受到固定芯片性能的局限。赛灵思打造了一个卓越的设计环境,使各学科领域的编程人员与工程师能够使用他们已熟知并掌握的工具和框架,共同开发与优化他们的软硬件。这意味着他们可以根据自己的应用调整硬件架构,而不需要新型芯片。

随着计算需求呈指数级增长,工程师与科学家常常受到固定芯片性能的局限。赛灵思打造了一个卓越的设计环境,使各学科领域的编程人员与工程师能够使用他们已熟知并掌握的工具和框架,共同开发与优化他们的软硬件。这意味着他们可以根据自己的应用调整硬件架构,而不需要新型芯片。

—— Victor Peng,赛灵思总裁兼首席执行官

| Vitis 统一软件平台 |

Vitis 堆栈

Vitis 堆栈

Vitis 平台构建在基于堆栈的架构之上,该架构可以无缝插入到开源的标准开发系统与构建环境,而且最重要的是,它包含一套丰富的标准库。

基础层是 Vitis 目标平台。该平台由电路板和预编程 I/O构成。第二层称为 Vitis 核心开发套件,覆盖开源赛灵思运行时库,以管理不同域间的数据移动,包括子系统、即将发布的 Versal ACAP™ 内的 AI 引擎和必要的外部主机。此外,该层也提供编译器、分析器和调试器等核心开发工具。虽然赛灵思提供的是世界一流的设计环境,但是这些工具设计的目的是能与业界标准的构建系统与开发环境无缝集成。

在第三层,8 个 Vitis 库提供 400 余种优化的开源应用。这 8 个库分别是:Vitis 基本线性代数子程序(BLAS)库、Vitis 求解器库、Vitis 安全库、Vitis 视觉库、Vitis 数据压缩库、Vitis 计量金融库、Vitis 数据库集和 Vitis AI 库。借助这些库,软件开发者可以使用标准的应用编程接口(API)来实现硬件加速。

Vitis AI 和特定领域架构

Vitis AI 和特定领域架构

Vitis 平台的第 4 层,也是最具有变革意义的一层是 Vitis AI。它集成了特定领域架构(DSA)。DSA 提供了针对AI模型的硬件实现,开发者可以使用包括 TensorFlow 和 Caffe 等业界领先框架对其进行配置与编程。Vitis AI 提供的工具链能在数分钟内完成优化、量化和编译操作,在赛灵思器件上高效地运行预先训练好的AI模型。此外,它也为从边缘到云端的部署提供了专用 API,实现业界一流的推断性能与效率。赛灵思很快还将推出另一个 DSA(Vitis Video),支持从 FFmpeg 直接进行编码并提供同样超级简单且功能极强大的端到端视频解决方案。由合作伙伴公司提供的 DSA 包括:与 GATK 集成用于基因分析的Illumina,与ElasticSearch 集成用于大数据分析的BlackLynx,以及当前我们客户正在使用的专有DSA。

REC

点击边框调出视频工具条 Vitis 统一软件平台视频简介 (中文)

点击边框调出视频工具条 Vitis 统一软件平台视频简介 (中文)

Vitis 开发者网站

Vitis 开发者网站

赛灵思还宣布推出了一个开发者网站,方便开发者获取示例、教程和文档,同时作为连接Vitis开发者社区的空间。它将由赛灵思和Vitis专家及爱好者共同管理,并将提供Vitis有关的最新更新、提示和技巧的宝贵信息。

Vitis 供货信息

Vitis 供货信息

Vitis 统一软件平台支持软件开发者无需新型芯片即可提高专用硬件的效率。该平台可免费用于赛灵思开发板,下个月即可下载。

点击“阅读原文”,注册 Vitis 邮件提醒以率先获得通知。

转载:赛灵思

- 分享

- 举报

暂无数据

暂无数据-

浏览量:2648次2022-01-03 09:00:44

-

浏览量:2542次2022-01-05 09:00:22

-

浏览量:2767次2022-01-23 09:00:26

-

浏览量:2183次2022-01-31 09:00:13

-

浏览量:2499次2022-01-12 09:00:26

-

浏览量:3312次2020-11-11 10:44:22

-

浏览量:2928次2019-06-28 10:35:50

-

浏览量:2444次2021-12-30 13:59:54

-

浏览量:2893次2022-01-06 09:00:16

-

2022-01-02 09:00:38

-

浏览量:4234次2021-01-06 10:15:22

-

浏览量:2454次2022-01-15 09:00:26

-

浏览量:3137次2022-01-04 09:00:38

-

浏览量:2186次2022-01-14 09:00:21

-

浏览量:2350次2022-03-10 11:55:28

-

浏览量:1600次2023-06-12 14:34:29

-

2022-01-07 09:00:27

-

浏览量:5242次2021-03-29 17:56:49

-

浏览量:6325次2020-08-20 14:18:11

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友