OCV、AOCV时序分析(一)

随着芯片工艺的发展,对于STA的要求也越来越高,并且设计的复杂度不断提升,传统的WC-BC模式已无法准确的反应芯片的实际真实时序。OCV正是在这种情况下被提出并实际应用到STA中。随着工艺的进一步发展,我们发现OCV模式也并不能满足我们的要求,我们期望能更精确的分析出实际的时序情况,而OCV模式本身带有太多的余量,并且分析方法也相对比较悲观。正是在这种情况下,我们提出了更精确的AOCV模式来进行时序分析。

静态时序分析工具提供的3种分析模式分别是:

- single_mode

- BC-WC

- OCV mode(AOCV,POCV)

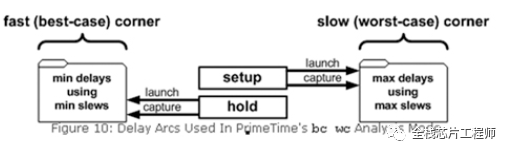

如下图,BC-WC模式下,setup check的检查都在worst-case下计算,而hold check的检查都在best-case下计算。

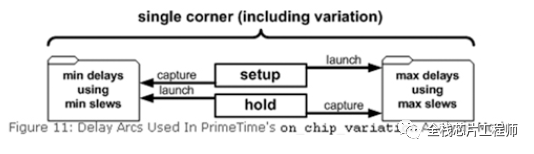

如下图,OCV模式下,setup/hold check的检查在worst-case/hold check下有交叉,具体分析流程见下面介绍。

OCV会对时序分析提出更严格的要求。那为什么需要OCV呢,因为制造工艺的限制,同一芯片上不同位置的MOS晶体管的性能会有一些差异。库中的PVT是一个"点",比如工艺1.0,1.2V,25℃,但实际芯片的PVT永远不会落在一个点上,而是一个范围。比如有些cell的PVT是工艺0.98,1.18V,20℃,有些cell的PVT是工艺1.01,1.21V,30℃。这些cell的PVT都不在同一个点上,怎么去分析呢?这时候就需要OCV了。

(一)OCV分析

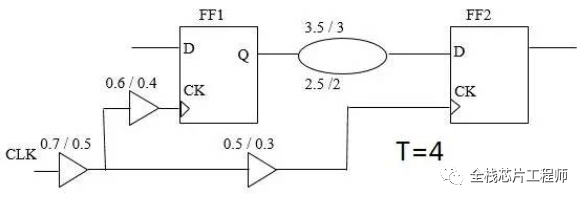

- OCV建立时间分析,暂时不考虑CPPR

clock period = 4

Launch clock late path (max) = 0.7 + 0.6 = 1.3

Data late path (max) = 3.5

Capture clock early path (min) = 0.5 + 0.3 = 0.8

Setup = 0.2

Data arrival time = 1.3 + 3.5 = 4.8

Data required time = 4 + 0.8 - 0.2 = 4.6

Slack =Data required time - Data arrival time= 4.6 - 4.8 = -0.2

- OCV保持时间分析,暂时不考虑CPPR

Launch clock early path (min) = 0.5 + 0.4 = 0.9

Data early path (min) = 2

Capture clock late path (max) = 0.7 + 0.5 = 1.2

Hold = 0.2

Data arrival time = 0.9 + 2 = 2.9

Data required time =1.2+0.2 = 1.4

Slack = Data arrival time - Data required time= 2.9 - 1.4 = 1.5

使用以上OCV的办法会使得timing analysis过于悲观,时序分析难以通过,因此,基于BC-WC的timing derate的OCV办法出现。- timing derate

计算OCV的一种简单方法,在某单一条件(BC-WC)下,把指定path的delay放大或者缩小一些,这个比率就是derate。

1)timing derate在setup check中Date arrival time即data path和launch clock path需要使用-late 选项,使得路径变慢。Date require time即capture clock path需要使用-early选项,加快路径延迟。

setup check 一般是工作在WC条件下,因此不需要在late path上(即launch clock path以及data path上)再加time derate,因为在WC条件下,launch clock path以及data path上的延迟已经是所有条件下最差的delay了,没有必要再加大延迟,但是WC条件下capture clock path上的delay用的是SS corner,延迟是最大的,因此需要加快。因此,做setup check,time derate只需要这样设置:

set_timing_derate -early 0.9set_timing_derate -late 1.0对于不同工艺,derate数值一般由实际工程经验总结而来。2)timing derate在hold check中Data require time中的capture clock path使用-late选项,使路径变慢。Data arrival time中的data path和launch clock path使用-early选项,使路径加快。

实际上,Hold check一般在BC条件下,因此,launch clock path与data path不需要再进一步减小delay, 因为已经是最小delay, 但是BC条件下的capture clock path用的FF corner,延时是最小的,需要derate。可以使用如下设置:

set_timing_derate -early 1.0set_timing_derate -late 1.2

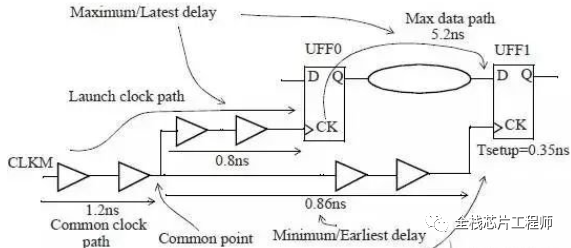

- CPPR(Clock Reconvergence Pessimism Removal),共同路径悲观去除。

针对common clock path那1.2ns的延迟,在setup分析时,launch clock path中没有被derate, 而在capture clock path中被time derate 1.2*0.9 =1.08. 显然这是相互矛盾的。考虑CPPR之后,我们必须减去一个CPP因子=1.2-1.08=0.12。

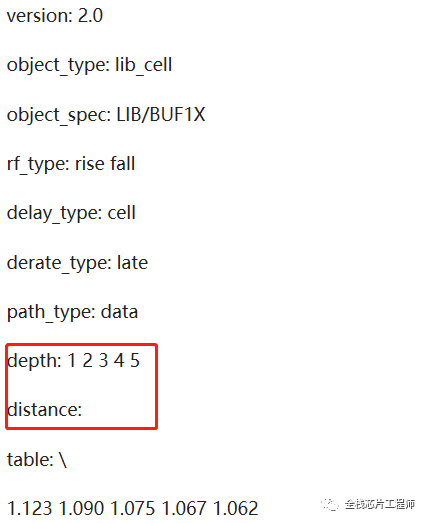

(二)AOCV分析AOCV全称Stage Based Advanced OCV,在OCV分析过程中,我们会给data path,clock path上设定单一的timing derate值。随着工艺演变的加速,这种设置方法是过于悲观的,OCV是片上误差,设定单一的timing derate值就代表一条path上所有的cell delay都或大于或小于标准值,因此不能一味的加大或减小delay来模拟片上误差。实际中的variation,很少是一个统一的数值,而大概率是服从正态分布的。AOCV提出:对于一条path上,级数越多其variation分布越接近正态分布,因而这条path整体的variation也越小。在实际设计中,会根据一条line上cell的级数不同而设置不同的dereate值。AOCV有专门的libary库,我们称为AOCV table。按照维度分为两种,一种是一位的只以stage count作为计算的表格,如下depth就是stage。

我们可以看出,级数(depth)越深,对应的derate越小。通过这种方式来剔除部分不必要的悲观量,使得设计在尽量覆盖实际情况的前提下更加容易收敛。

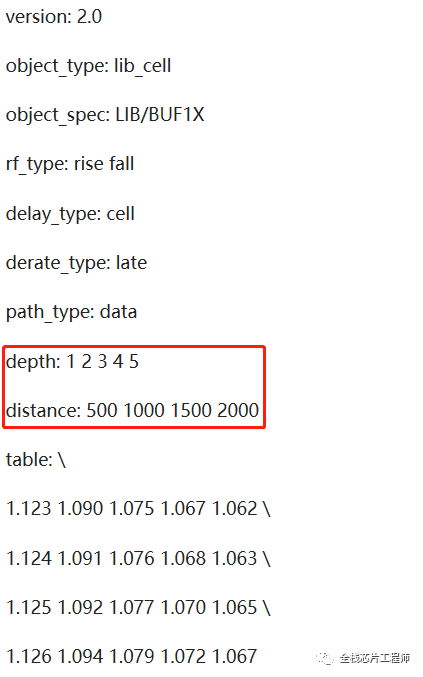

另外一种是以distance和stage count混合组成的二维AOCV table。它在计算derate时同时考虑了timing path的距离因素,当然这个虽然更加精确,但是会增加runtime,所以一般现在一维表格用的更多。

随着数据路径的增长,OCV效应会减弱;随着跨越距离的增加,OCV效应又会增强。AOCV就是要通过考虑这些OCV效应的变化从而避免过度悲观的OCV分析。如何来有效降低OCV的过度悲观,是我们提高时序分析准确性的关键。

OCV和AOCV就先讲到这里,接下来继续介绍POCV和LVF的内容,敬请关注公众号!

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:4145次2021-12-22 09:00:26

-

浏览量:7277次2021-12-23 09:00:16

-

浏览量:9953次2021-02-20 17:50:13

-

浏览量:4037次2022-03-15 09:00:13

-

浏览量:6577次2021-02-21 16:01:28

-

浏览量:6293次2021-02-21 21:08:27

-

浏览量:12336次2020-11-30 23:56:05

-

浏览量:7523次2021-02-21 01:20:21

-

浏览量:10994次2021-12-11 15:12:29

-

浏览量:11262次2019-11-27 10:01:41

-

浏览量:4650次2021-04-05 12:09:13

-

浏览量:3813次2022-08-16 19:12:41

-

浏览量:14365次2022-01-09 09:00:11

-

浏览量:4298次2021-02-24 14:20:44

-

浏览量:215次2025-09-24 14:21:43

-

浏览量:6435次2021-03-22 01:26:53

-

浏览量:2147次2018-05-30 22:51:53

-

浏览量:3403次2019-11-09 19:10:44

-

浏览量:1128次2024-01-25 13:00:44

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友