LDO vs DC-DC

一般电源管理芯片就是LDO(low dropout regulator)和DC-DC,芯片升压要选DC-DC,降压可根据需求选DC-DC或者LDO。

LDO:优点是噪声低、静态电流小、体积小、外围电路简单、成本低;缺点是输入输出电压差较大会导致转换效率低,原因是LDO利用电阻分压来降压,降下来的电压转换成了热量,因此能量损耗大。

DC-DC:优点是大电流、转换效率高;缺点是噪声大、体积大。LDO设计

LDO(low dropout regulator),低压差+线性+稳压器。

“低压差”:输出压降比较低,例如输入3.3V,输出可以达到3.2V。 “线性”:LDO内部的MOS管工作于线性电阻。 “稳压器”说明了LDO的用途是用来给电源稳压。

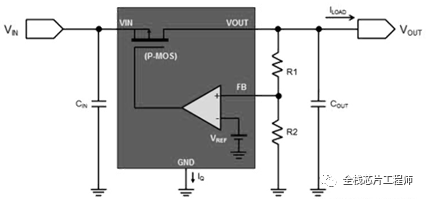

PMOS LDO基本结构框图如下,主要由PMOS、运放、反馈电阻和基准参考电压构成。

输出电压经电阻分压后与带隙基准电压做比较,通过运放输出Vg来调节输出。当Vout由于负载变化等原因导致电压下降时,运放FB点电压下降,与Vref电位相比较,放大器会减小它的输出,使得PMOS的栅极电压下降,进而使得|Vgs|增加,PMOS的导通电流就越大,从而使得Vout上升,完成负反馈调节。

例如,采用5V电源供电时,3.3V LDO的效率不会超过66%,但当输入电压降至3.6V时,其效率将增加到最高到91.7%。LDO功耗为(VIN – VOUT) × IOUT。电荷泵

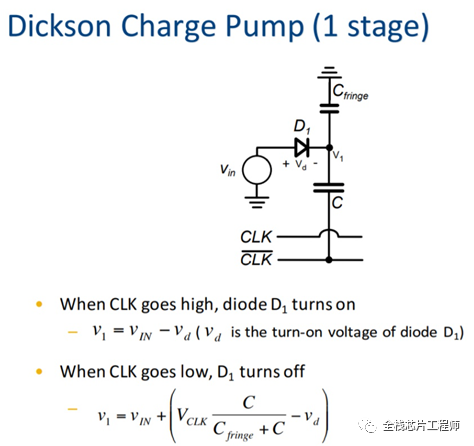

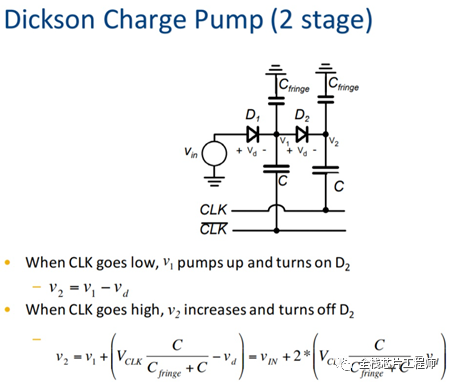

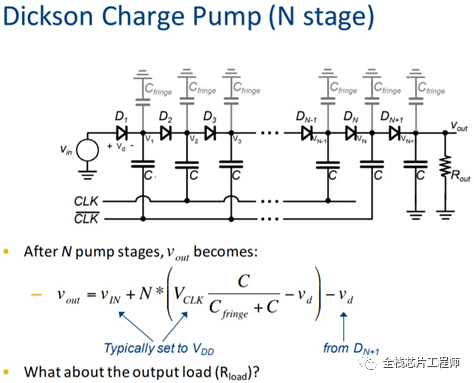

可见,在忽略边缘电容Cfringe的情况下,每经过一级,电压被“泵”高“VCLK - Vd”。一个更简单例子如下,理想情况下,二极管的导通电压为0V(正常0.6-0.7V):

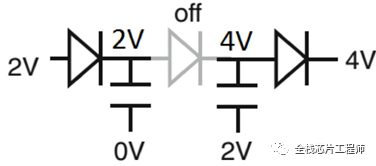

初始状态:

VDD=2V,输⼊电压Vin=2V,输出电压Vout=2V。右边电容下极板电压从0v跳变到2V,由于电容两端电压不能突变,所以上极板的电压变为4V,经过二极管后输出也是4V。

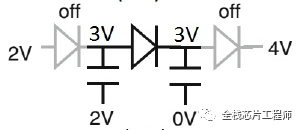

CLK为高时:

第⼀个电容冲到4V,第⼆个电容掉到2V,中间⼆极管导通,电荷共享后两个电容都达到3V。

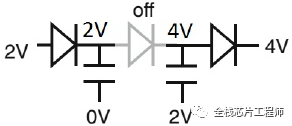

CLK为低时:

第⼀个电容掉到1V,第⼆个电容升到5V;然后第⼀个电容被Vin冲到2V,第⼆个电容向Vout放电直到电位降到4V(假设后面有clamp电路,超过4v会倒掉)。

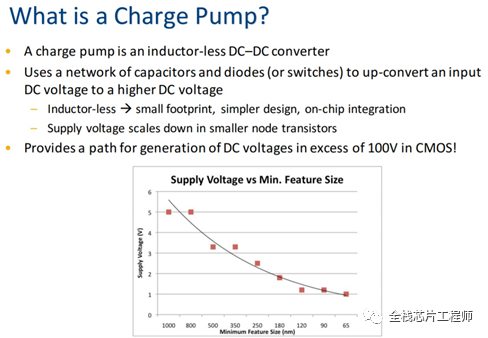

电荷泵称为开关电容DC-DC变换器,与基于电感的DC-DC开关电源相比较时,又称为无感式DC-DC电源变换器。电荷泵采用电容为开关和储能元件,在当前CMOS工艺条件下的集成更为容易,因此集成度更高、成本低。

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:1899次2019-11-15 08:58:58

-

浏览量:1972次2023-08-22 17:38:04

-

浏览量:585次2025-08-06 16:59:48

-

浏览量:1204次2023-03-13 10:12:43

-

浏览量:1739次2022-09-29 11:50:08

-

浏览量:22071次2021-06-18 00:29:01

-

浏览量:3858次2020-12-16 11:06:42

-

浏览量:2097次2023-07-21 17:25:16

-

浏览量:3921次2023-06-26 08:57:07

-

浏览量:4777次2023-03-24 16:30:17

-

浏览量:1642次2023-03-17 17:42:08

-

浏览量:3527次2022-10-28 09:28:29

-

浏览量:2960次2020-10-31 09:31:02

-

浏览量:2777次2020-07-03 18:27:11

-

浏览量:1985次2019-09-04 17:56:37

-

2023-04-07 15:12:43

-

浏览量:996次2023-07-05 10:17:52

-

浏览量:8602次2019-09-26 16:29:28

-

浏览量:4247次2020-12-03 13:59:05

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友