芯片后仿之SDF 3.0解析(一)

SDF文件是在VCS/NC-Verilog后仿真运行时将STD/IO/Macro门级verilog中specify的延迟信息替换为QRC/Star-RC抽取的实际物理延时信息,所以如果SDF文件的条件信息在verilog的specify中没有的话,就会报SDFCOM_INF的warning,意思是IOPATH not found。

本文解析SDF的Header Section信息、Cell Entries信息,尤其重点讲解Cell Entries的Delay Entries信息。

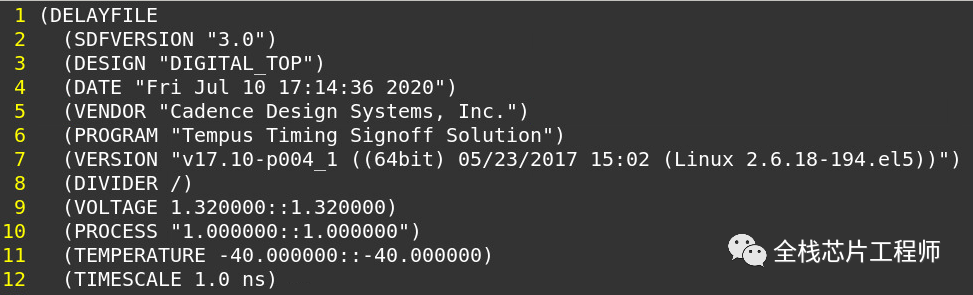

- 下文先讲SDF文件的第一部分Header Section

- SDF Version Entry,包括1.0、2.1、3.0,SDF3.0是1995年release。

- Design Name Entry,设计顶层名

- Date Entry,SDF生成日期,PT或Tempus产生

-

Vendor Entry,Vendor信息,如下图

- Program Version Entry

- Hierarchy Divider Entry

-

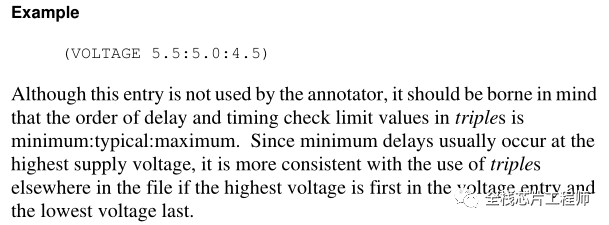

Voltage Entry,SDF3.0官方解释如下

-

Process Entry,SDF3.0官方解释如下

-

Temperature Entry,SDF3.0官方解释如下

- Timescale Entry,SDF3.0官方解释如下

- 下文继续讲解SDF文件的第二部分Cell Entries:

- 下文继续讲解SDF文件的第二部分Cell Entries:

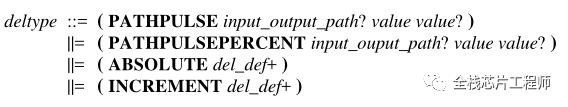

完整的Delay Entries信息格式如下:

- PATHPULSE

- PATHPULSEPERCENT

- ABSOLUTE Delays

- INCREMENT Delays

-

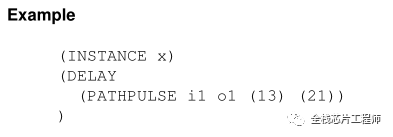

PATHPULSE举例说明:

-

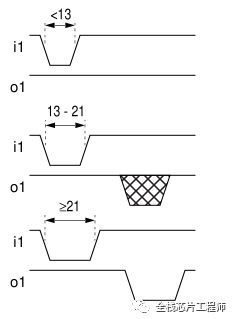

当从i1到o1输出的低电平脉冲小于13ns时,该低电平脉冲直接被忽略;

-

当从i1到o1输出的低电平脉冲介于13ns~21ns时,输出为X态;

-

当从i1到o1输出的低电平脉冲大于21ns时,正常输出低电平;

2. PATHPULSEPERCENT本质上和PATHPULSE是一回事,只不过是按照path延时比例来计算什么时候丢弃输入脉冲宽度不足的信号(pulse rejection limit),什么时候将输入脉冲宽度不足的信号显示为X态(X limit)。比如:

2. PATHPULSEPERCENT本质上和PATHPULSE是一回事,只不过是按照path延时比例来计算什么时候丢弃输入脉冲宽度不足的信号(pulse rejection limit),什么时候将输入脉冲宽度不足的信号显示为X态(X limit)。比如:

以上图为例,the high-to-low delay is 37, 因此,the pulse

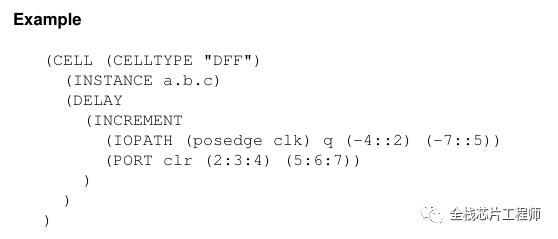

rejection limit is 25% of 37 and the X limit is 35% of 37.3. ABSOLUTE DelaysABSOLUTE Delays中的物理延时数据就是用来替换verilog specify中的延时数据的。4. INCREMENT Delays

用来叠加在verilog specify中的延时数据上的,INCREMENT Delays是存在负数的情况的,叠加后的延时若是负数的话,某些EDA工具可能不支持或直接强制延时为0。

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:5541次2021-12-21 09:00:19

-

浏览量:6490次2021-12-21 09:00:28

-

浏览量:8324次2022-01-01 09:00:13

-

浏览量:3155次2021-12-21 09:00:33

-

浏览量:8161次2022-02-09 09:00:13

-

浏览量:5191次2022-01-02 09:00:13

-

浏览量:6129次2021-07-01 16:47:45

-

浏览量:3502次2020-09-25 12:02:04

-

浏览量:4943次2021-09-28 13:45:07

-

浏览量:5038次2020-08-15 17:29:07

-

浏览量:3059次2020-08-21 19:39:43

-

浏览量:6999次2021-12-11 15:12:36

-

浏览量:4743次2022-08-17 09:01:18

-

浏览量:14580次2020-12-02 16:57:03

-

浏览量:3886次2022-02-20 09:00:18

-

浏览量:2880次2022-01-12 09:00:12

-

浏览量:3022次2022-01-23 09:00:19

-

浏览量:2777次2022-01-13 09:00:13

-

浏览量:2790次2020-03-12 13:43:17

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友