SRAM工作原理

1.1 SRAM工作原理

静态随机存取存储器(Static Random Access Memory,SRAM)是随机存取存储器的一种,所谓“静态”,是指只要保持通电,储存的数据就可以恒常保持。而动态随机存取存储器(DRAM)所储存的数据就需要周期性地刷新。本文先简述SRAM的工作原理。

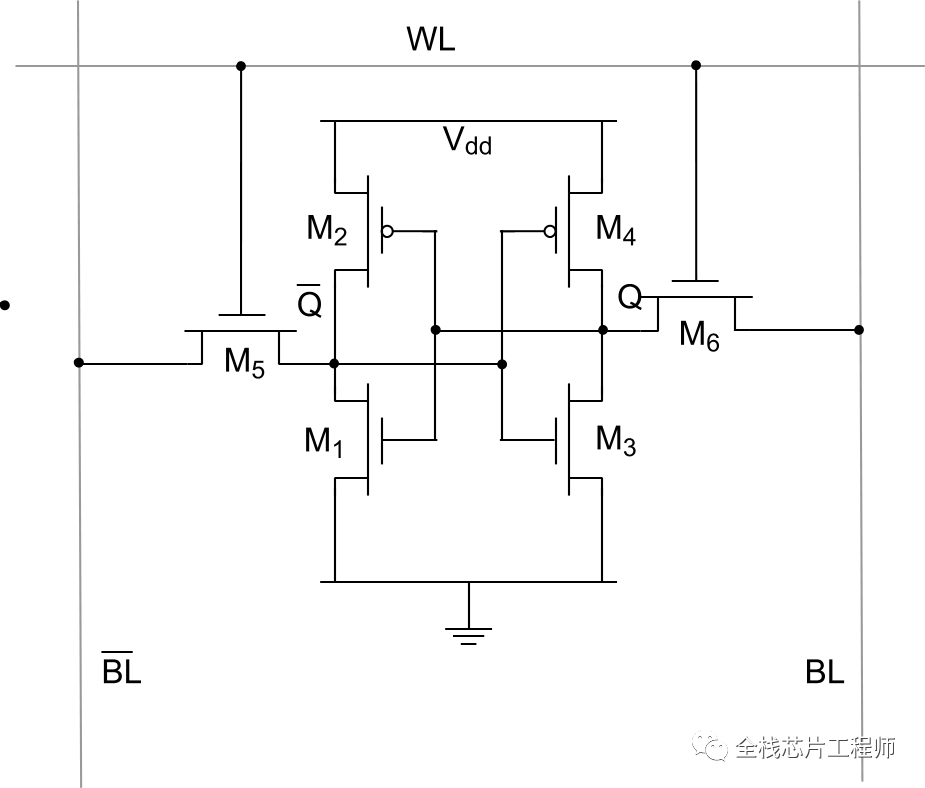

如下图所示,6T SRAM由M1、M2组成一个inverter,由M3、M4组成另一个inverter,这两个inverter的output分别接到另一个inverter的input,构成一个latch,从而可以将数据锁住。

连接到M5、M6的gate信号是word line(缩写成WL),是用来控制SRAM bit-cell的开关信号,M5、M6一起打开或关闭。M5、M6的Drain端是读出或写入的bit line(缩写成BL)。若要写入1,则BL驱动电压为VDD;若要写入0,则BL驱动电压为0。

1. SRAM写操作

当bit-cell存储的内容为1而要写入0,即Q的电压值为VDD,此时只需要将WL电压值提高到VDD且BL为0,那么Q电压值将通过M6被拉低,Q’的电压值将通过M5被拉高,再由M1/M2,M3/M4两个反相器推挽,bit-cell存储的内容就从1变成0了。此时WL电压拉低即可完成数据锁存。

2. SRAM读操作

读出bit-cell存储单元时,先将BL和BL’拉到等电位,这个电位通常为pre-charge voltage电压,一般为VDD(或VDD-Vth),当BL及BL’两端电位相等之后可以将之浮接(floating)或通过阻抗接至pre-charge voltage电压源,然后将WL打开,利用Q及Q’的寄生电容通过M6、M5与BL、BL’产生charge sharing及分压的效果从而让BL与BL’产生电压差,最后利用外部的sense amplifier将差异信号放大从而读出0或1。

简言之,6T SRAM的写是利用外部电压改变bit-cell的锁存电荷值,而读是bit-cell的内部锁存电荷值去驱动外部相同电位的BL、BL’,bit-cell的驱动能力有限,因此需要sense amplifier来放大。

发散一下:

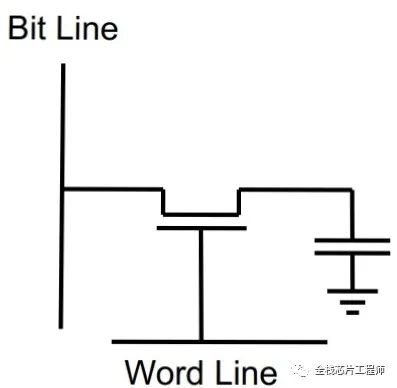

动态DRAM的每个单元可以看作是一个MOS管和一个电容组合,电容充电后是1,没充电是0,WL被选中后,MOS管导通,BL就和电容导通,可以进行读写操作。相比SRAM而言,DRAM容易漏电,因此需要刷新,但其结构简单、集成度高、成本低,因此被大规模使用。

转载:全栈芯片工程师

- 分享

- 举报

暂无数据

暂无数据-

浏览量:2917次2020-08-04 20:10:32

-

浏览量:2968次2019-12-27 11:38:54

-

浏览量:1931次2019-08-22 17:14:34

-

浏览量:3370次2021-04-08 11:32:15

-

浏览量:723次2023-04-21 12:59:31

-

浏览量:2821次2020-04-28 16:17:08

-

浏览量:2078次2018-04-02 11:00:18

-

浏览量:5582次2021-05-08 15:04:36

-

浏览量:4124次2020-11-13 09:40:22

-

浏览量:2543次2020-08-05 20:49:45

-

浏览量:2040次2022-05-30 09:56:07

-

浏览量:1552次2024-01-26 15:15:36

-

浏览量:1382次2020-11-04 15:32:57

-

浏览量:2354次2019-07-17 15:26:14

-

浏览量:1561次2019-11-29 16:15:38

-

浏览量:5361次2019-11-09 09:37:38

-

浏览量:5016次2022-03-30 09:00:15

-

浏览量:2247次2018-02-15 23:55:45

-

浏览量:10402次2021-06-25 16:41:43

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

david

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友