DP83867IS SGMII eye diagram问题

1. 前言

使用的是带CPU的DP83867IS,通过SGMII接口

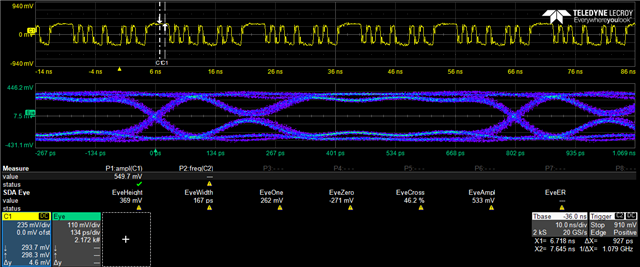

从PHY到CPU的眼图看起来很好

而从CPU到PHY的眼图很差

2. 问题梳理

(1)能证实SGMII道有100欧姆的阻抗吗?

(2)能不能做一个误码率测试来看看眼图是否仍然是可以接受的?

(3)因为从PHY到CPU的眼睛是好的,可能有一个问题在CPU的传输侧

可以尝试从CPU端检查这个问题

对于1/,必须有100欧姆阻抗

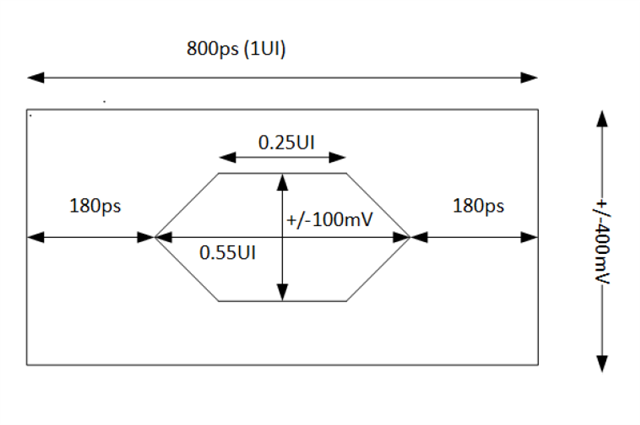

对于2/,我复制了下面的eye mask,它的左边一定会失败

对于3/,正在内部检查CPU

3. 调试记录

(1)SGMII rx对的输入阻抗是多少?

SGMII rx对的输入阻抗为100欧姆差分

(2)有一个CPU评估板,使用相同的CPU和PHY从其他供应商,波形看起来很好

(3)对于DP83867来说,封装引脚和内部模之间的飞行时间是多少,或者导线有多长?

如果内部线太长,上升边会出现毛刺或台阶

在SGMII模式下对DP83867进行了大量测试,

没有发现上升边缘有任何故障或台阶

内部导线的长度应该太短,以免造成任何问题

做了很多测试,甚至在PHY引脚侧剪断了线,波形仍然很好

所以我们有点100%肯定DP83867 SGMII输入有bug

4.几个疑问

(1)是否在另一个DP83867或另一个PHY上尝试过这个,并看到相同的问题?

(2)在最初的示波器捕获中,在哪里测量信号?是在DP83867的SGMII引脚还是在其他地方?

(3)在最近的捕获中,它正在测量由CPU传输的信号,但是CPU没有连接到PHY,对吗?

对于1,我有另一个板与相同的CPU和不同的PHY,

eye diagram要好得多

因为连接是相当简单的只是连接CPU和PHY通过一个AC couple电容

对于2,都在DP83867的SGMII引脚处测量

对于3,切断PHY侧的电线

也用TDR进行了测量,会显示阻抗曲线

发现DP83867的内部阻抗下降了很多,差不多32欧姆

5. 整改建议

(1)设置DP83867环回SGMII,看看从CPU到PHY的问题是否也从PHY到CPU

(2)在CPU方面进行一些测量,看看您是否看到了同样的问题

- 分享

- 举报

暂无数据

暂无数据-

浏览量:4704次2021-07-03 14:35:11

-

浏览量:4637次2021-07-16 10:09:05

-

浏览量:7064次2021-07-14 18:01:13

-

浏览量:4655次2021-07-17 16:19:56

-

浏览量:6313次2021-06-24 10:54:24

-

浏览量:6716次2021-03-02 09:35:15

-

浏览量:5845次2021-06-19 14:43:01

-

浏览量:10035次2021-06-19 14:22:58

-

浏览量:7277次2021-06-17 15:14:12

-

浏览量:8815次2021-06-17 14:48:29

-

浏览量:2190次2020-07-07 09:07:51

-

浏览量:1309次2025-01-16 21:26:58

-

浏览量:1069次2023-01-12 16:03:41

-

浏览量:6909次2021-04-20 16:37:57

-

浏览量:5615次2021-05-10 17:48:42

-

浏览量:3591次2021-11-20 15:15:21

-

浏览量:1996次2023-04-14 11:48:45

-

浏览量:10203次2022-06-08 14:09:35

-

浏览量:13433次2020-12-10 00:29:44

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

free-jdx

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友