AXI总线(1)从AXI-lite入手了解协议(读)

前言

我们常在各种场合遇到axi总线,例如在使用高速总线协议aurora协议,例如在生成常用IP核(例如RAM)时的AXI总线选择,例如在使用zynq等等,当然,在纯粹的FPGA玩家中,axi大多数还是出现在高速总线的内部互联中。

上面说的只是我在赛灵思FPGA使用中的一点认识,当然AXI不可能只存在赛灵思中,AXI总线已经成为与赛灵思或英特尔提供的IP核合作的重要标准。这一通用标准旨在使设计与各种片上系统内核(如赛灵思的MicroBlaze或英特尔的NiosII)的接口变得简单。该总线也被ARM使用,因此它自然适合Zynq和Soc+FPGA产品。

要实现正确的性能和高速性能,可能是一个挑战。今天,我们将仅限于AXI-lite总线:AXI的一个版本,既不支持突发,也不支持锁定,也不支持交易ID,也不支持不同的服务质量保证。

构想AXI系列博文的目的也是在实践中经常遇到AXI总线,虽然也在IP核中使用,但是总感觉不得要领,于是想更深入的了解下,从基础开始,总结并分享。

分清AXI信号含义

如果没有从头开始认识AXI总线的话,恐怕大家都有一个感受,AXI的各种信号是什么含义?哪个信号是主设备的信号,哪个是从设备的信号,奇怪的字母组合代表什么含义?

这些都搞不清,更别提看懂协议看懂时序图了。

本篇作为起始之篇,本小节就先了解这些内容。

AXI总线作为主从设备通信的总线,通信的关键是各种READY和VALID信号。*VALID用于发出有效(valid)请求或确认(acknowledgement)的信号。这两个信号共同构成一个握手。当信道的一方有信息要发送时,无论是请求(request)还是确认(acknowledgement),都会设置一个有效(valid)信号,而另一方则控制一个就绪(ready)信号。AXI规范还包含一个非常具体的要求:有效(valid)信号的拉高永远不能依赖于同一通道的就绪(ready)信号。

有效(valid)信号的拉高永远不能依赖于同一通道的就绪(ready)信号。

这句话的意思是:valid和ready是解耦合的,主设备不会因为从设备没有ready好而不发出valid请求,当然反之亦然;

我们常常看到AXI信号的各种前缀以及后缀,例如:

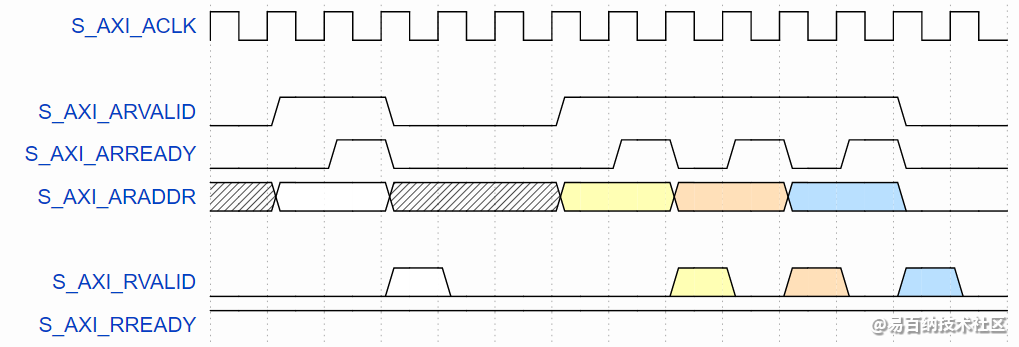

这是一个AXI-lite的读通信协议时序图,前缀S_*的含义是这些信号是从设备的输入以及输出;

AXI的含义是该信号是AXI信号,这是AXI信号的专属;

我们还可以看到在VALID以及READY等等我们熟悉的信号前面还有AR,R之类的字符,这是什么含义呢?

这就得从AXI的结构来看了:

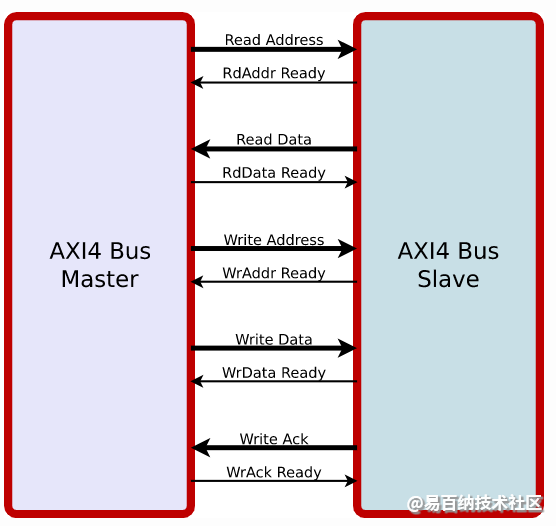

一般的AXI有五个这样的通道,而不是一个读写请求通道和一个确认-响应通道。对于向总线写数据,有写地址通道、写数据通道和写响应通道。对于从总线上读取数值,有一个读地址-请求通道和一个读响应通道。

今天,我们只讨论这个接口的AXI-lite版,可以认为是轻量版,精简版。与完整的AXI规范不同,AXI-lite从这种交互中删除了很多功能。也许最大的区别是,在AXI-lite中,任何读写请求一次只能引用一个数据,而且不需要为每个事务提供唯一的标识符。还有其他一些小的区别。AXI-lite没有要求实现锁定、服务质量或任何缓存协议。

有这些损失也是正常的,既然是精简版,精简了内容,还要求全面的效果,怎么可能呢?

鱼与熊掌不可兼得也!

说了这么多,可以说AR,R之类的含义了,AR是Address Read,R表示Read。这些也是根据上面的AXI BUS的五个通道信息得来的。

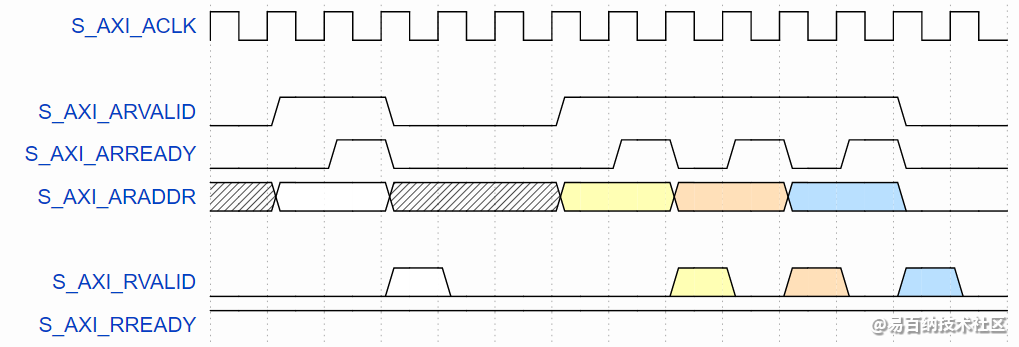

我们再来看这个时序图:

就可以知道一些信息了:

S_AXI_ARVALID,作为从设备的输入,由主设备产生该信号,表示主设备要发起读请求了,要读就得有读地址,读地址伴随着读地址有效信号,即该信号。读地址就是时序图中的S_AXI_ARADDR,AR的含义同样如此。

当从设备准备好接受时,就是拉高准备信号Ready,即S_AXI_ARREADY信号。

S_AXI_ARVALID与S_AXI_ARREADY信号同时为高,表示达成握手,我请求有效了,你也准备好了,就通信吧,你情我愿。

从设备接收到请求信号后以及地址后,就得响应人家的请求呀,最终就是吐出人家要的读数据,S_AXI_RVALID,即读数据有效信号,主设备收到该信号后,就知道数据返回了,主设备如果空闲,S_AXI_RREADY有效,就收到了读数据,一次大的握手完成。当然,上述时序图没有画出读数据信号,读返回数据与S_AXI_RVALID保持同步。

AXI-lite 读

关于AXI-lite的读,在上一小节已经给出大概过程了,就是一次简单的握手。

大致过程就是上一小节说的那样,但是,事实上,还有一个信号没有说全,下面引出:

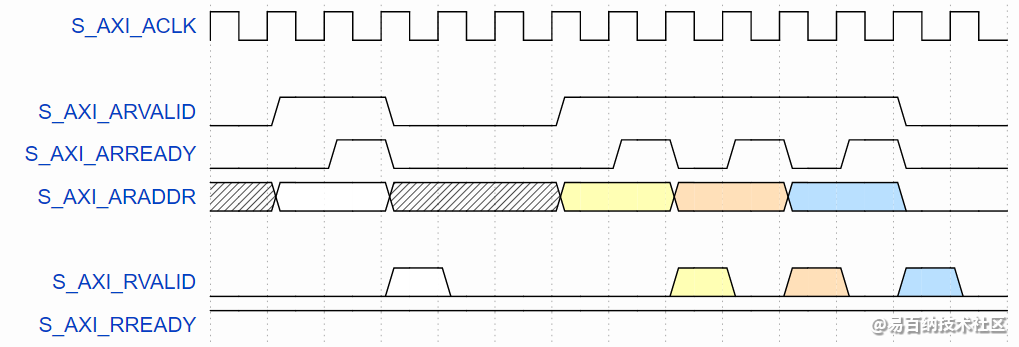

在从设备响应读请求中,在这个例子中,从机发出确认信号S_AXI_RVALID后,由于主设备将S_AXI_RREADY保持在高电平,所以确认只需要保持一个高电平。此外,除了S_AXI_RVALID之外,从机还将读取结果S_AXI_RDATA返回,以及S_AXI_RRESP,即任何潜在错误状况的指示器。与上面的S_AXI_ARADDR信号一样,这两个信号也是确认信号的一部分。

下面对上述过程的描述给出补充总结:

-

一旦S_AXI_ARVALID被拉高,它必须保持高电平,直到S_AXI_ARVALID && S_AXI_ARREADY。

-

当S_AXI_ARVALID为真,但从机还没有提出S_AXI_ARREADY时,S_AXI_ARADDR必须保持不变。

同样,一旦S_AXI_RVALID回复确认请求被拉高,它也必须保持高电平,直到S_AXI_RVALID&&S_AXI_RRESP都为真。

-

与读地址通道一样,当S_AXI_RVALID为真而主设备还没有拉高S_AXI_RREADY时,S_AXI_RDATA和S_AXI_RRESP必须保持不变。

-

对于每一个有S_AXI_ARVALID && S_AXI_ARREADY的请求,在某个时间段内必须有一个S_AXI_RVALID && S_AXI_RREADY的时钟周期。

需要注意的是AXI总线协议中没有总线终止功能。因此,在发生总线错误后,你仍然需要处理任何剩余的确认。

为了使事情顺利进行,我们还想坚持在一些实现定义的最小的时钟等待之后,从机必须提出S_AXI_ARREADY。

这同样适用于反向链接:当S_AXI_RVALID为高时,主站不应该被允许无限期地保持S_AXI_RREADY为低。

最后

下一篇博文给出写的过程。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:7296次2022-05-11 08:10:28

-

浏览量:2648次2023-04-19 09:15:44

-

浏览量:17027次2020-12-03 00:29:52

-

浏览量:15927次2018-09-27 20:15:39

-

浏览量:6128次2022-05-09 11:00:58

-

浏览量:6681次2022-05-10 12:41:18

-

2020-07-01 11:02:45

-

浏览量:3166次2020-08-26 17:29:05

-

浏览量:3555次2022-02-24 09:00:15

-

浏览量:11706次2020-12-19 13:31:48

-

浏览量:3939次2020-11-11 09:50:43

-

浏览量:3845次2021-11-20 15:05:18

-

浏览量:1796次2020-01-04 10:19:25

-

浏览量:10367次2021-06-08 17:32:00

-

浏览量:1291次2023-12-11 11:01:31

-

浏览量:3383次2022-06-08 14:16:22

-

浏览量:2603次2020-08-21 14:05:19

-

浏览量:3923次2020-08-18 19:54:58

-

浏览量:862次2024-03-06 15:44:49

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友