DS90UH948-Q1 连接947 fpdlink显示方案黑屏问题调试2

1. 前言

承接上篇

https://www.ebaina.com/articles/140000012744

2. 上电流程注意事项

要求只有在SER已经开始发送有效的视频信号后才启动DES。

参考948 datasheet图9-1、表9-1

在上电状态机状态达到0x1B之前以及将reg 0x23和0x24设置为0x00之后使用系统。

如果reg 0x24甚至在更长的时间后不能达到状态0x1B,这意味着序列有一些错误。

状态机到达0x1B的条件是:

A)连接已被检测与连接反序列化器

b)序列化器锁相环已锁定到输入OLDI时钟

3. 检测上电顺序

发现948比947早

并且948的开机顺序与948的数据表不一致

但是屏幕供应商批准了这个设计

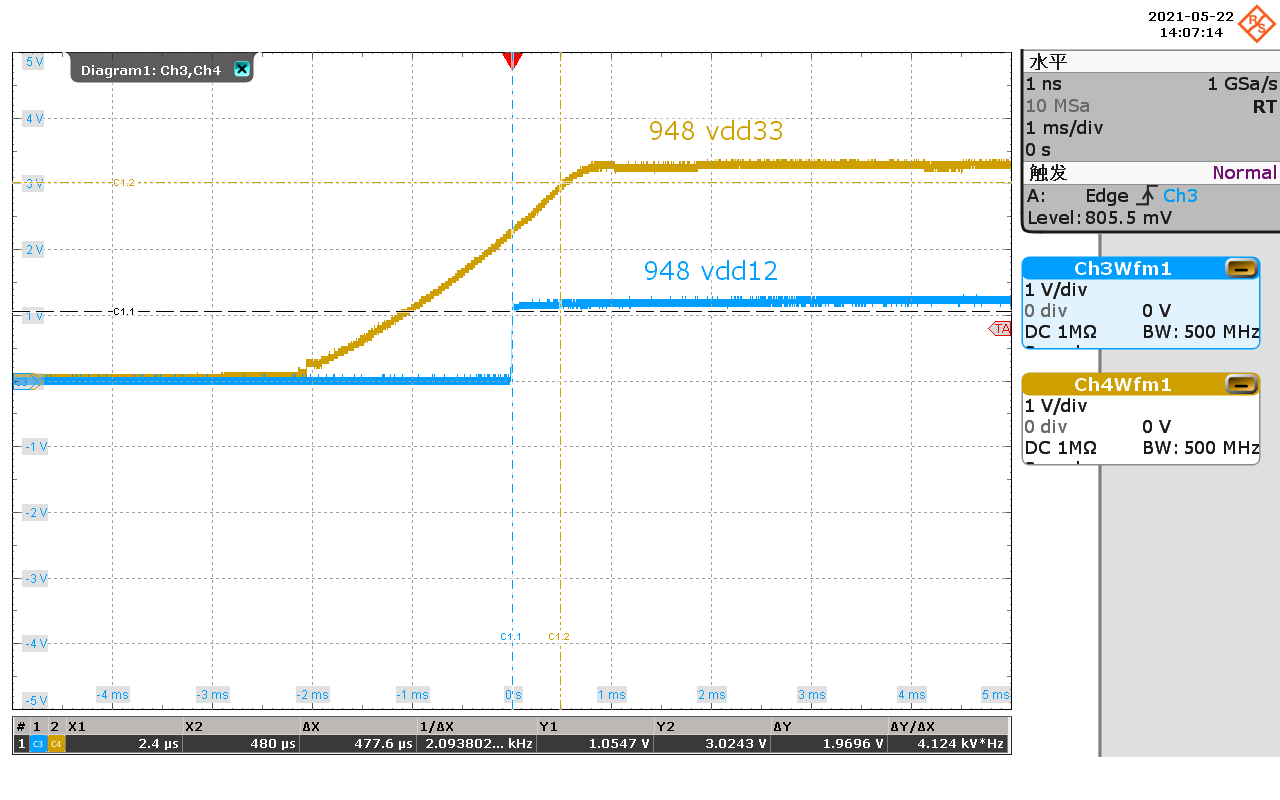

在这里附上948的时序图,请帮助我们判断948的通电顺序是否正确

提供的上电顺序错误。在VDD33或VDD12之前,PDB不能切换到高

参考图9-1和表9-1

已经固定了948 PDB和947+948的上电顺序

上电后链路可以正常建立,这是一个改进

然而,在执行947勘误表时,发现软复位947、复位FPD PLL、复位OLDI操作会导致UNLOCK,且UNLOCK不能长时间重锁,时间超过2min

正常的系统会在几十毫秒内重新锁定

4. 测试947的CLK

通常应该在短时间内获得LOCK

这只有在输入CLK到947不稳定时才可能

我测量了947的输入CLK波形,在丢锁时是稳定的,947reg0xC=0x4

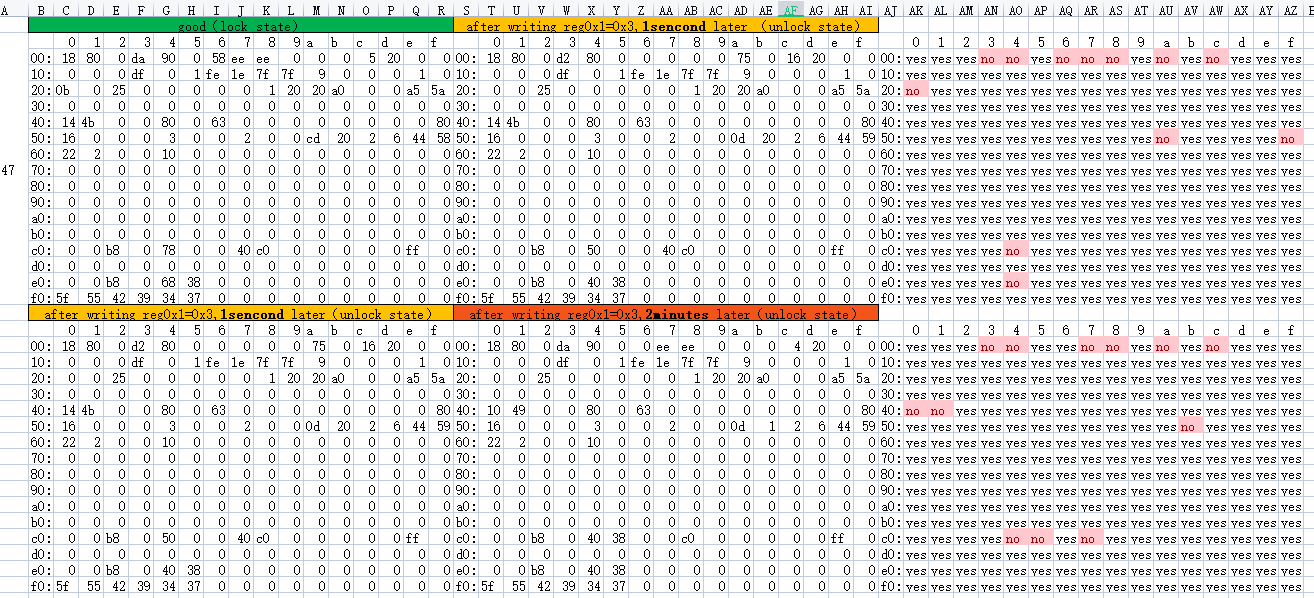

下图显示了我们删除勘误表后的测试过程

上电后屏幕显示正常,链路正常

写入947reg0x1=0x3后,947reg0xC从0x5变为0x16

显示屏由正常显示变为黑屏,长时间无法恢复

目前,948的通电时间比947晚3秒,

5. check 寄存器配置

这些reg转储是在第一次上电和软复位后采取的

它是好的前软复位947,坏后软复位947

948升级比947晚了3秒。

这个时间是否合理,这个时间应该设定多久?

# i2cdump -f -y 1 0xc

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 18 80 00 da 90 00 58 ee ee 00 00 00 05 20 00 00 ??.??.X??...? ..

10: 00 00 00 df 00 01 fe 1e 7f 7f 09 00 00 00 01 00 ...?.??????...?.

20: 0b 00 25 00 00 00 00 00 01 20 20 a0 00 00 a5 5a ?.%.....? ?..?Z

30: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

40: 14 4b 00 00 80 00 63 00 00 00 00 00 00 00 00 80 ?K..?.c........?

50: 16 00 00 00 03 00 00 02 00 00 cd 20 02 06 44 59 ?...?..?..? ??DY

60: 22 02 00 00 10 00 00 00 00 00 00 00 00 00 00 00 "?..?...........

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 b8 00 78 00 00 40 c0 00 00 00 00 00 ff 00 ..?.x..@?.......

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 b8 00 68 38 00 00 00 00 00 00 00 00 00 00 ..?.h8..........

f0: 5f 55 42 39 34 37 00 00 00 00 00 00 00 00 00 00 _UB947..........

/ # i2cdump -f -y 1 0xc

No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 18 80 00 da 90 00 58 ee ee 00 00 00 05 20 00 00 ??.??.X??...? ..

10: 00 00 00 df 00 01 fe 1e 7f 7f 09 00 00 00 01 00 ...?.??????...?.

20: 0b 00 25 00 00 00 00 00 01 20 20 a0 00 00 a5 5a ?.%.....? ?..?Z

30: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

40: 14 4b 00 00 80 00 63 00 00 00 00 00 00 00 00 80 ?K..?.c........?

50: 16 00 00 00 03 00 00 02 00 00 cd 20 02 06 44 59 ?...?..?..? ??DY

60: 22 02 00 00 10 00 00 00 00 00 00 00 00 00 00 00 "?..?...........

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 b8 00 68 38 00 00 c0 00 00 00 00 00 ff 00 ..?.h8..?.......

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 b8 00 68 38 00 00 00 00 00 00 00 00 00 00 ..?.h8..........

f0: 5f 55 42 39 34 37 00 00 00 00 00 00 00 00 00 00 _UB947..........

/ # i2cset -f -y 1 0xc 0x1 0x3

/ # i2cdump -f -y 1 0xc

\No size specified (using byte-data access)

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 18 80 00 d2 80 00 00 00 00 00 75 00 16 20 00 00 ??.??.....u.? ..

10: 00 00 00 df 00 01 fe 1e 7f 7f 09 00 00 00 01 00 ...?.??????...?.

20: 00 00 25 00 00 00 00 00 01 20 20 a0 00 00 a5 5a ..%.....? ?..?Z

30: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

40: 14 4b 00 00 80 00 63 00 00 00 00 00 00 00 00 80 ?K..?.c........?

50: 16 00 00 00 03 00 00 02 00 00 0d 20 02 06 44 59 ?...?..?..? ??DY

60: 22 02 00 00 10 00 00 00 00 00 00 00 00 00 00 00 "?..?...........

70: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

80: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

90: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

a0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

b0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

c0: 00 00 b8 00 50 00 00 40 c0 00 00 00 00 00 ff 00 ..?.P..@?.......

d0: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

e0: 00 00 b8 00 40 38 00 00 00 00 00 00 00 00 00 00 ..?.@8..........

f0: 5f 55 42 39 34 37 00 00 00 00 00 00 00 00 00 00 _UB947..........- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

6. 分析结果

(1)VDD12应该晚于VDD3V3/VDDIO或同时出现,但不能早于VDD3V3/VDDIO

(2)复位操作

如果您想要数字重置947,应该将0x01写入0x01,

否则您将重置所有寄存器为默认值,必须重新配置并再次应用所有的Erratas。

(3)DS90UH948Q-Q1启动条件

DS90UH948Q-Q1应该在兼容的序列化器开始发送有效视频数据后启动

如果这如果条件不满足,则在接收输入数据后需要进行数字(软件)复位或硬复位(切换PDB引脚)

这要求防止DS90UH948Q-Q1锁定到任何随机或噪声信号,确保DS90UH948Q-Q1具有确定性

启动行为、指定的锁定时间和最佳的自适应均衡器设置

7. 其它几个问题

(1)单链路模式下,端口1 (DOUT1)是否可以配置输出fpdlink?

不可以,与单个通道反序列化器配对时,主通道总是port0

(2)输入到947的OpenLDI时钟频率是45M,可以使用双链路模式吗?

双模式下最小oLDI CLK为50MHz,单模式下最小oLDI CLK为25MHz

(3)需要使用强制单链接模式吗?目前软件配置了自动匹配模式,为什么大部分开机时都是双链路模式?

如果使用自动检测,该设备应该工作在单一模式

(4)在双链路模式下,两个转发通道都发送I2c数据吗?

如果使用双链路模式,两条链路都有I2C通信

- 分享

- 举报

暂无数据

暂无数据-

浏览量:5288次2021-07-06 16:47:24

-

浏览量:6336次2021-06-30 09:32:11

-

浏览量:4704次2021-07-12 17:06:16

-

浏览量:6424次2021-07-15 16:35:07

-

浏览量:7027次2021-06-24 11:51:22

-

浏览量:6480次2021-04-20 16:37:57

-

浏览量:6367次2021-07-09 15:17:28

-

浏览量:9228次2020-11-13 14:54:14

-

浏览量:5390次2021-07-09 15:20:08

-

浏览量:5082次2021-04-20 16:55:59

-

浏览量:6746次2019-09-09 14:36:52

-

浏览量:15163次2020-11-13 15:08:38

-

浏览量:4934次2021-06-30 10:41:01

-

2021-07-30 17:04:37

-

浏览量:4709次2021-07-23 11:31:27

-

浏览量:4712次2021-07-23 11:33:52

-

浏览量:4203次2021-05-13 10:17:28

-

浏览量:4620次2021-07-30 15:48:52

-

浏览量:5318次2021-07-09 15:23:33

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

free-jdx

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友