SN65DPHY440SS Re-Timer驱动器意外跳变分析2

1. 前言

承接上篇

https://www.ebaina.com/articles/140000012728

2. EVM的波形

在我看来,DPHY440在重置期间没有将时钟和数据线放入LP11

D0_N和CLK_P是DPHY440的输出吗?

你能捕获输入波形并与EVM进行比较吗?

我已经捕获了EVM的波形

我只有一个4通道的示波器,所以我为这些捕获探测了VCC,然

后在验证其功能之后探测了VDD

同样,这只是使用EVM

无论复位状态如何,VCC都不会从1.8V开始改变

VDD名义上是1.2V,复位低到0V。

在Reset完成高电压充电之前,它返回到1.2V

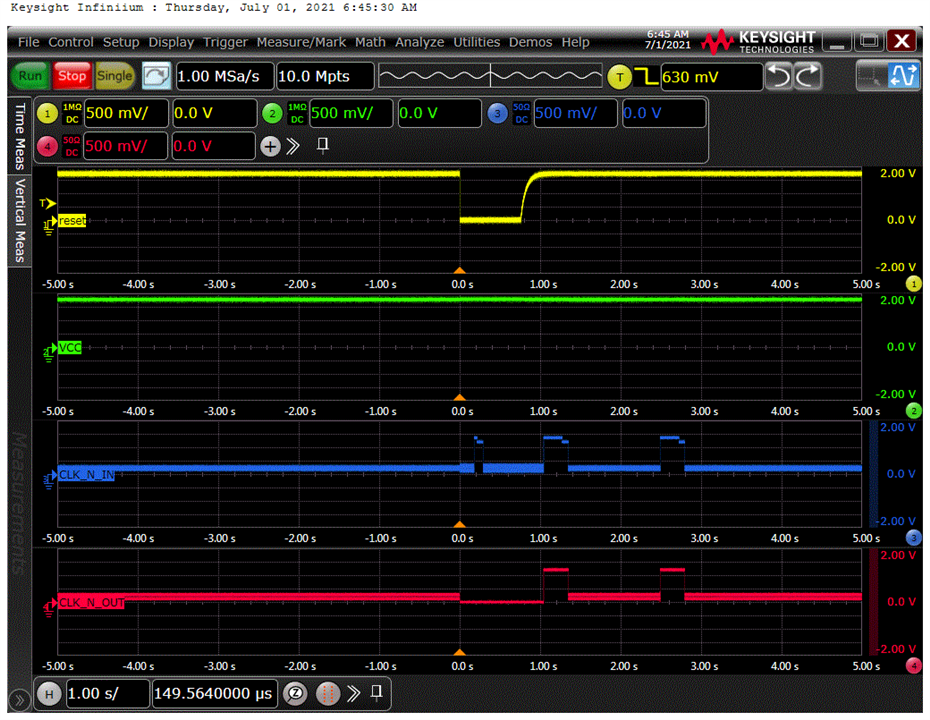

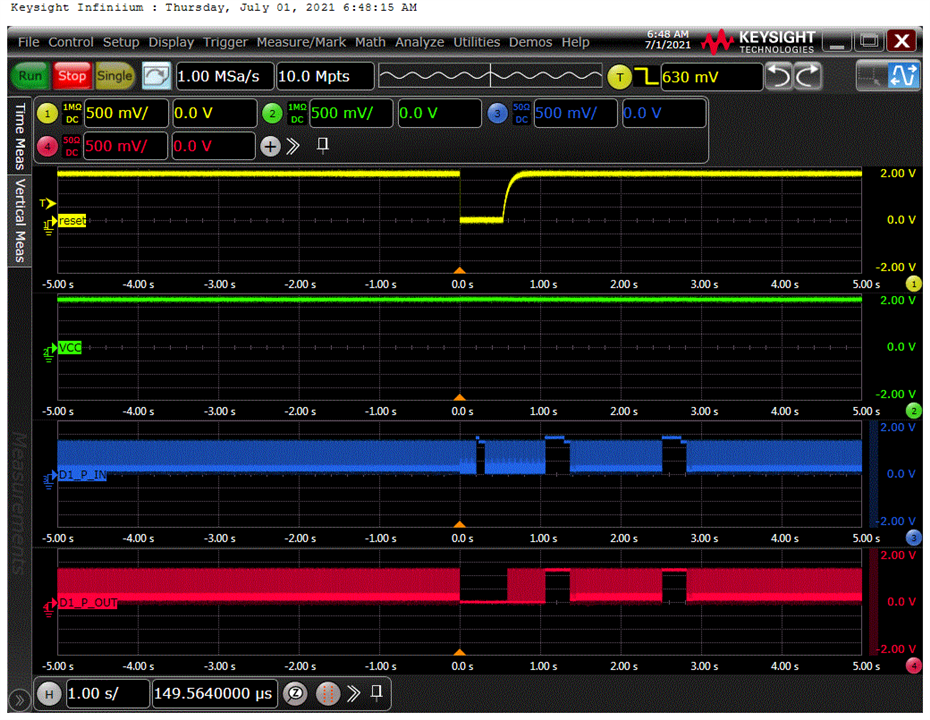

(1)下面是重置、VCC、CLK_N(重新计时器之前)和CLK_N(重新计时器之后)的两个捕获

Nominal:

On Reset:

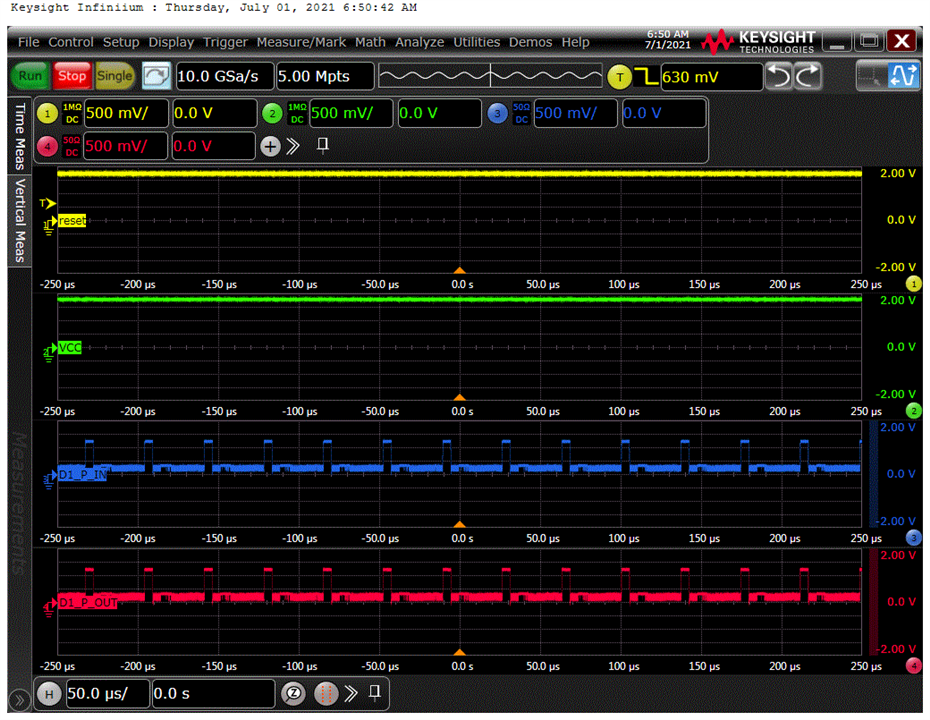

(2)下面是Reset、VCC、DA2_P和DB2_P(重新计时器之后)的两个捕获

Nominal:

On Reset:

我的系统被设置为在LP和HS之间运行连续时钟和数据切换

Reset low时,Re-Timer的输出归零

当复位返回高,可以看到时钟和数据都表现出一对扩展LP状态之前,以进入正常状态

3. 使用re-timer 采集波形

以下是在我的PCB上使用re-timer的相同捕获:

无论复位状态如何,VCC都不会从1.8V开始改变

VDD名义上是1.8V,复位低时变为0V

这似乎表现出与EVM明显不同的行为,所以我在这里截取了一个范围捕获

下面是重置、VCC、CLK_N(重新计时器之前)和CLK_N(重新计时器之后)的两个捕获

Nominal:

On Reset:

下面是Reset、VCC、DA2_P和DB2_P(重新计时器之后)的两个捕获

Nominal:

On Reset:

4. 修改建议

时钟和数据有一个直流偏移

不知道是来自测量装置还是电路板

确认DPHY440热垫和单板接地之间的连接是否牢固

建议在热垫和电路板地面之间至少有75%的焊锡覆盖

- 分享

- 举报

暂无数据

暂无数据-

浏览量:4674次2021-07-03 16:30:38

-

浏览量:6828次2021-08-10 14:13:11

-

浏览量:936次2023-10-12 17:35:59

-

浏览量:1994次2023-11-23 15:09:34

-

浏览量:5370次2021-08-10 14:24:09

-

浏览量:614次2025-06-16 17:14:39

-

浏览量:2101次2020-06-23 17:33:04

-

浏览量:4323次2020-12-07 14:15:12

-

浏览量:7796次2020-12-08 09:48:56

-

浏览量:1257次2023-03-24 10:57:56

-

浏览量:911次2023-11-01 17:33:57

-

浏览量:3593次2020-10-14 09:30:05

-

浏览量:7522次2020-08-15 17:22:26

-

浏览量:4713次2021-09-22 16:39:28

-

浏览量:2682次2020-10-15 10:52:46

-

浏览量:3312次2020-11-11 10:44:22

-

浏览量:1926次2020-06-15 19:10:09

-

浏览量:1129次2023-10-11 17:54:56

-

2022-09-16 15:24:48

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

free-jdx

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友