Jetson Nano平台更改DP1上DisplayPort的设备树4

1. 前言

承接上篇

https://www.ebaina.com/articles/140000012663

2. 检测电源

看起来像nvidia,hpd-gpio仍然需要hpd-gpio

确定dpaux1也有和dpaux相同的配置吗?

这是sor/dpaux和sor1/dpaux1在当前设备树中的样子:

sor {

compatible = "nvidia,tegra210-sor";

reg = <0x0 0x54540000 0x0 0x40000>;

reg-names = "sor";

status = "disabled";

nvidia,sor-ctrlnum = <0x0>;

nvidia,dpaux = <0x73>;

nvidia,xbar-ctrl = <0x2 0x1 0x0 0x3 0x4>;

clocks = <0x26 0xde 0x26 0xb6 0x26 0x12f>;

clock-names = "sor_safe", "sor0", "pll_dp";

resets = <0x26 0xb6>;

reset-names = "sor0";

nvidia,sor-audio-not-supported;

linux,phandle = <0x6d>;

phandle = <0x6d>;

hdmi-display {

compatible = "hdmi,display";

status = "disabled";

linux,phandle = <0x116>;

phandle = <0x116>;

};

dp-display {

compatible = "dp, display";

status = "disabled";

linux,phandle = <0x117>;

phandle = <0x117>;

};

prod-settings {

#prod-cells = <0x3>;

prod_c_dp {

prod = <0x5c 0xf000f10 0x1000310 0x60 0x3f00100 0x400100 0x68 0x2000 0x2000 0x70 0xffffffff 0x0 0x180 0x1 0x1>;

};

};

};

sor1 {

compatible = "nvidia,tegra210-sor1";

reg = <0x0 0x54580000 0x0 0x40000>;

reg-names = "sor";

interrupts = <0x0 0x4c 0x4>;

status = "okay";

nvidia,sor-ctrlnum = <0x1>;

nvidia,dpaux = <0x74>;

nvidia,xbar-ctrl = <0x0 0x1 0x2 0x3 0x4>;

clocks = <0x26 0x16f 0x26 0xde 0x26 0x16e 0x26 0xb7 0x26 0x12f 0x26 0xf3 0x26 0xca 0x26 0x7d 0x26 0x6f 0x26 0x80>;

clock-names = "sor1_ref", "sor_safe", "sor1_pad_clkout", "sor1", "pll_dp", "pll_p", "maud", "hda", "hda2codec_2x", "hda2hdmi";

resets = <0x26 0xb7 0x26 0x7d 0x26 0x6f 0x26 0x80>;

reset-names = "sor1", "hda_rst", "hda2codec_2x_rst", "hda2hdmi_rst";

nvidia,sor1-output-type = "dp";

nvidia,active-panel = <0x75>;

linux,phandle = <0x6a>;

phandle = <0x6a>;

hdmi-display {

compatible = "hdmi,display";

status = "disabled";

linux,phandle = <0x118>;

phandle = <0x118>;

disp-default-out {

nvidia,out-xres = <0x1000>;

nvidia,out-yres = <0x870>;

};

};

dp-display {

compatible = "dp, display";

status = "okay";

nvidia,hpd-gpio = <0x5b 0xe1 0x1>;

nvidia,is_ext_dp_panel = <0x1>;

linux,phandle = <0x75>;

phandle = <0x75>;

disp-default-out {

nvidia,out-type = <0x3>;

nvidia,out-align = <0x0>;

nvidia,out-order = <0x0>;

nvidia,out-flags = <0x0>;

nvidia,out-pins = <0x1 0x0 0x2 0x0 0x3 0x0 0x0 0x1>;

nvidia,out-parent-clk = "pll_d2";

};

dp-lt-settings {

lt-setting@0 {

nvidia,drive-current = <0x0 0x0 0x0 0x0>;

nvidia,lane-preemphasis = <0x0 0x0 0x0 0x0>;

nvidia,post-cursor = <0x0 0x0 0x0 0x0>;

nvidia,tx-pu = <0x0>;

nvidia,load-adj = <0x3>;

};

lt-setting@1 {

nvidia,drive-current = <0x0 0x0 0x0 0x0>;

nvidia,lane-preemphasis = <0x0 0x0 0x0 0x0>;

nvidia,post-cursor = <0x0 0x0 0x0 0x0>;

nvidia,tx-pu = <0x0>;

nvidia,load-adj = <0x4>;

};

lt-setting@2 {

nvidia,drive-current = <0x0 0x0 0x0 0x0>;

nvidia,lane-preemphasis = <0x1 0x1 0x1 0x1>;

nvidia,post-cursor = <0x0 0x0 0x0 0x0>;

nvidia,tx-pu = <0x0>;

nvidia,load-adj = <0x6>;

};

};

};

prod-settings {

#prod-cells = <0x3>;

prod_c_dp {

prod = <0x5c 0xf000f10 0x1000310 0x60 0x3f00100 0x400100 0x68 0x2000 0x2000 0x70 0xffffffff 0x0 0x180 0x1 0x1>;

};

};

};

dpaux {

compatible = "nvidia,tegra210-dpaux";

reg = <0x0 0x545c0000 0x0 0x40000>;

interrupts = <0x0 0x9f 0x4>;

nvidia,dpaux-ctrlnum = <0x0>;

status = "okay";

clocks = <0x26 0xb5>;

clock-names = "dpaux";

resets = <0x26 0xb5>;

reset-names = "dpaux";

linux,phandle = <0x73>;

phandle = <0x73>;

prod-settings {

#prod-cells = <0x3>;

prod_c_dpaux_dp {

prod = <0x124 0x37fe 0x24c2>;

};

prod_c_dpaux_hdmi {

prod = <0x124 0x700 0x400>;

};

};

};

dpaux1 {

compatible = "nvidia,tegra210-dpaux1";

reg = <0x0 0x54040000 0x0 0x40000>;

interrupts = <0x0 0xb 0x4>;

nvidia,dpaux-ctrlnum = <0x1>;

status = "okay";

clocks = <0x26 0xcf>;

clock-names = "dpaux1";

resets = <0x26 0xcf>;

reset-names = "dpaux1";

linux,phandle = <0x74>;

phandle = <0x74>;

prod-settings {

#prod-cells = <0x3>;

prod_c_dpaux_dp {

prod = <0x124 0x37fe 0x24c2>;

};

prod_c_dpaux_hdmi {

prod = <0x124 0x700 0x400>;

};

};

};检查一下power tree

“hardware/nvidia/platform/t210/porg/kernel-dts/porg-platforms/tegra210-porg-fixed-p3448-0000-a00.dtsi”

看看它是否符合你的设计

在nano devkit上,当DP电缆插入设备时,

应该可以看到avdd-io-edp-1v05被拉到高

gpio-511 ( |avdd-io-edp-1v05 ) out hi既然1v8没有回应,

看来电源是不正确的

3. check 官方dts

这个文件定义了DP和HDMI的电源。

hardware/nvidia/platform/t210/porg/kernel-dts/porg-platforms/tegra210-porg-power-tree-p3448-0000-a00.dtsi

这些“p3448_avdd_io_edp”调节器在

tegra210-porg-fixed-p3448-0000-a00.dtsi中定义。

必须检查电源是否真的与板设计一致

例如,

目前p3448_avdd_io_edp是由gpio = <&max77620 7 0>提供的。

DP电源也使用PMIC的gpio作为电源

它是这样连接的:

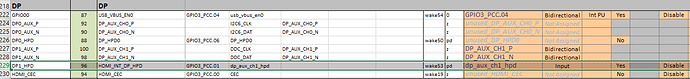

DP1_HPD = 96

如果有nano devkit,可以插入一个dp电缆,并看到dmesg

它应该打印如下内容

tegradc tegradc.1: dp: plug event received该日志由驱动程序“kernel/nvidia/drivers/video/tegra/dc/ dpc”打印,由dpaux完成。

可以使用dtc工具将整个dtb文件转换回dts

可以将我的dts与官方dts进行比较

通常只有sor/tegradc/ pinmux和dpaux来比较

现在得到dmesg:

[ 33.909503] avdd-io-edp-1v05: disabling我仍然需要调整gpio = <&max77620 7 0>

查询pin 96

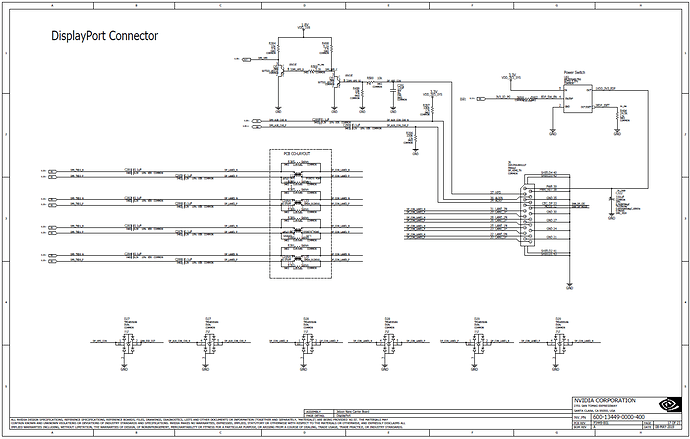

4. 检查原理图

现在所做的是将设备树与硬件上的电源相匹配。

如果有gpio来控制电源,那么将gpio写为稳压器,

并将其放到DT中相应的场中。

电路图是这样的

只是所有的东西都连接到DP1

如果这些是一直通电的电源,请将这些字段输入DT &battery_reg。

这是一个不需要控制的虚拟系统。

设置了gpio=<&battery_reg>;

gpio-511我现在看不见,不能监控

如果认为设备树都很好,那么可以对比pinmux。

也许可以比较一下你的板子和devkit之间的这些状态,看看有什么不同。

或者做进一步的工作,如跟踪驱动程序代码

(1)下面是devkit的一个例子:

Name:Bank:Port CNF OE OUT IN INT_STA INT_ENB INT_LVL

拔了电缆

CC: 7:0 92 80 80 02 00 12 121200

插入电缆

CC: 7:0 92 80 80 02 00 12 121200(2)把vdd-dp- pwrr -supply稳压器从&p3448_avdd_io_edp改成max77620_ldo8

DP0端口的电源轨由模块中PMIC的GPIO7控制,

DP1的电源轨来自PMIC的LDO8。

关于你之前的问题。

INTLVL中断选择(Edge/Level)

INTENB 中断使

INTSTA GPIO中断状态

OE 允许输出

已经检查过了,是正确的GPIO→96→PCC 1

5. 与官方板对比

从00到02,我没有看到任何变化

总是保持与→CC: 7:0 92 80 80 02 00 12 121200

我的板子:

Cc: 7:0 92 80 80 000 00 10 101000

to

Cc: 7:0 92 80 80 02 00 10 101000

在devkit和自己主板上检查/sys/kernel/debug/gpio,

查看hpd引脚上的区别

(1)devki

gpio:

Gpio-511 (|avdd-io-edp-1v05) out lo

和

Gpio-511 (|avdd-io-edp-1v05) out high

tegra_gpio:

总是一样

Cc: 7:0 92 80 80 02 00 12 121200

(2)我的板子

gpio:

Gpio-511不再显示!!

我们已经删除了max77620 7 0

gpio-511消失,在gpio列表中

tegra_gpio:

CC: 7:0 92 80 80 00 00 10 101000

to

CC: 7:0 92 80 80 02 00 10 101000

认为电源轨仍然没有正确配置,

因为日志看起来就像没有电源一样

需要进一步检查

6. 回溯dts

为什么把hdmi-display放在sor1下ok,把dp-display放在disabled ??

sor1 {

compatible = “nvidia,tegra210-sor1”;

reg = <0x0 0x54580000 0x0 0x40000>;

reg-names = “sor”;

interrupts = <0x0 0x4c 0x4>;

status = “okay”;

nvidia,sor-ctrlnum = <0x1>;

nvidia,dpaux = <0x75>;

nvidia,xbar-ctrl = <0x0 0x1 0x2 0x3 0x4>;

clocks = <0x26 0x16f 0x26 0xde 0x26 0x16e 0x26 0xb7 0x26 0x12f 0x26 0xf3 0x26 0xca 0x26 0x7d 0x26 0x6f 0x26 0x80>;

clock-names = “sor1_ref”, “sor_safe”, “sor1_pad_clkout”, “sor1”, “pll_dp”, “pll_p”, “maud”, “hda”, “hda2codec_2x”, “hda2hdmi”;

resets = <0x26 0xb7 0x26 0x7d 0x26 0x6f 0x26 0x80>;

reset-names = “sor1”, “hda_rst”, “hda2codec_2x_rst”, “hda2hdmi_rst”;

nvidia,ddc-i2c-bus = <0x76>;

nvidia,hpd-gpio = <0x5b 0xe1 0x1>;

nvidia,active-panel = <0x77>;

linux,phandle = <0x6a>;

phandle = <0x6a>; hdmi-display {

compatible = "hdmi,display";

status = "okay";

generic-infoframe-type = <0x87>;

linux,phandle = <0x77>;

phandle = <0x77>;

disp-default-out {

nvidia,out-xres = <0x1000>;

nvidia,out-yres = <0x870>;

nvidia,out-type = <0x1>;

nvidia,out-flags = <0x2>;

nvidia,out-parent-clk = "pll_d2";

nvidia,out-align = <0x0>;

nvidia,out-order = <0x0>;

};

};

dp-display {

compatible = "dp, display";

status = "disabled";

linux,phandle = <0x119>;

phandle = <0x119>;

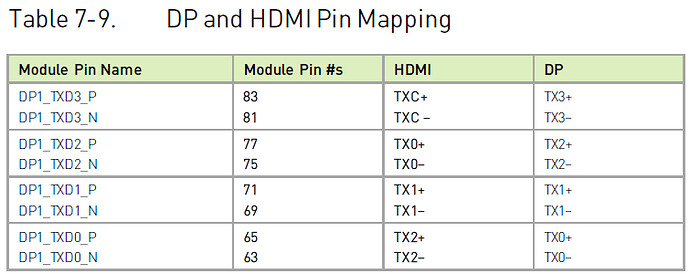

};确保设计中的车道贴图是正确的,

以下是用DP配置交换的lane0和lane2,这与HDMI设置不同。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:8813次2021-06-17 14:48:29

-

浏览量:10034次2021-06-19 14:22:58

-

浏览量:7276次2021-06-17 15:14:12

-

浏览量:12925次2021-06-16 17:06:40

-

浏览量:7884次2021-07-31 15:26:23

-

浏览量:2648次2023-11-29 12:31:57

-

浏览量:3019次2024-02-20 10:27:52

-

浏览量:8003次2021-08-04 17:14:53

-

浏览量:11212次2021-06-11 11:24:45

-

浏览量:10203次2022-06-08 14:09:35

-

浏览量:13212次2021-02-19 16:56:03

-

浏览量:9419次2021-05-14 14:43:43

-

浏览量:7734次2021-03-22 11:45:10

-

浏览量:2368次2019-11-07 14:15:02

-

浏览量:8616次2021-01-08 15:04:53

-

浏览量:2737次2020-04-08 10:32:05

-

浏览量:6429次2021-05-28 13:52:17

-

浏览量:9991次2021-04-27 17:56:41

-

浏览量:1539次2024-02-21 17:08:25

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

free-jdx

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友