FPGA硬件算法(3)流水线逻辑处理的几种策略

新的FPGA学生纠结的事情之一是,数字逻辑中的一切都以并行方式进行。

这些学生中有许多人有计算机科学背景。他们理解算法是如何工作的,以及一件事必须按照特定的顺序在另一件事之后发生。但是,他们往往对算法中的每一步都占据一块数字逻辑的想法感到纠结,而这块数字逻辑将在每一个时钟上发挥作用(无论是否使用)。

对操作排序的一个解决方案是创建一个巨大的状态机。但现实是,FPGA倾向于一次性创建每个状态的所有逻辑,然后只在每个时钟结束时选择正确的答案。

另一方面,如果FPGA无论如何都要实现所有的操作逻辑,为什么不把每个操作安排成一个序列,每个阶段做一些有用的事情呢?这种方法将算法重新安排成一个流水线。在完成同样的算法时,流水线往往比状态机的方法更快,甚至可以更节省资源(不一定如此)。

因此,让我们讨论一下处理与流水线逻辑相关的信号的几种不同策略。一般来说,没有一个适合所有情况的策略。你选择的策略将取决于你的算法的需求,以及它的数据源(输入)和目的地(输出)。

全局有效信号CE

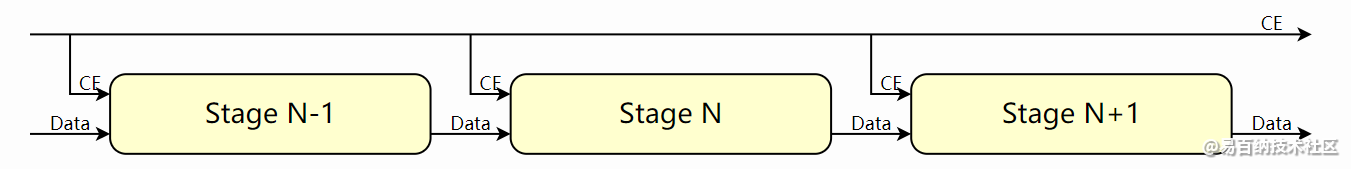

我们要讨论的第一个处理流水线的策略是使用一个全局有效信号。在每个阶段,当全局有效信号为真时,进入流水线的数据是有效的。同样地,每个阶段完成所需的时钟不会超过有效信号之间的时间。我喜欢用CE或 "时钟使能 "信号来表示这种有效逻辑。因此,图1显示了这种通信的框图。

基本规则是这样的:

有一条全局CE线,与时钟同步。这条线在新数据准备好的时候是真的。

只有当这条CE线为真时,逻辑才被允许转换。

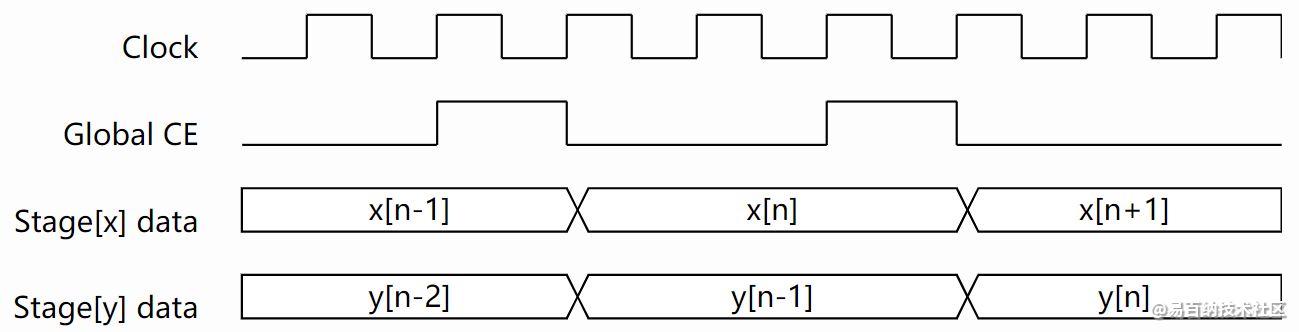

下面的时序图可以描述这种工作方式:

这种方法的好处是,本身不需要真正的流水线逻辑。每个阶段只是等待全局有效信号为真,然后应用其逻辑。

在Verilog中这种方法类似于:

always @(posedge i_clk)

if (i_ce)

begin

output <= (some function of)(i_input);

end // else *NOTHING*. Nothing is allowed to change without CE=1- 1

- 2

- 3

- 4

- 5

不过,你可能很快就会发现,这种方法并不能处理所有的流水线需求。然而,虽然它不能处理所有的流水线需求,但它可以处理一个关键问题集的需求:信号处理。

在一个典型的信号处理应用中,数据或者从模拟到数字(A/D)转换器进入FPGA,或者从FPGA出来到数字到模拟(D/A)转换器,或者可能两者都有。采样率定义了CE信号需要达到高电平的时间。数字逻辑工程师的工作是沿途对采样进行操作。

由于数据以固定的速率在FPGA中移动,并且由于它从未突然改变速度,全局有效信号对它来说相当有效。

应用包括数字滤波、数字锁相环、数字控制振荡器等等。事实上,任何以固定数据速率工作的东西通常都是这种流水线方法的良好候选者。

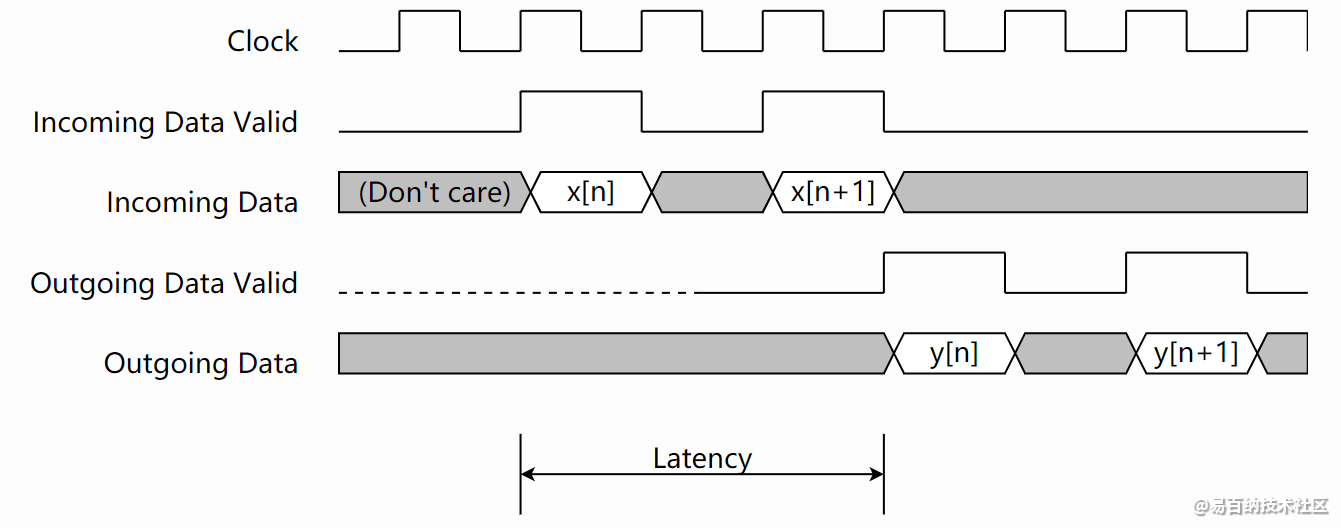

非全局有效的 CE

不过,我们上面讨论的全局有效信号有两个基本问题。第一个问题是,没有办法知道一个输出样本是否 "有效"。第二个问题是,整个操作依赖于一个统一的时钟来产生CE信号。如果数据是以突发方式产生的,而你不仅想知道输出何时有效,还想知道输出是否有效,那会怎样?在这种情况下,需要另一种方法。

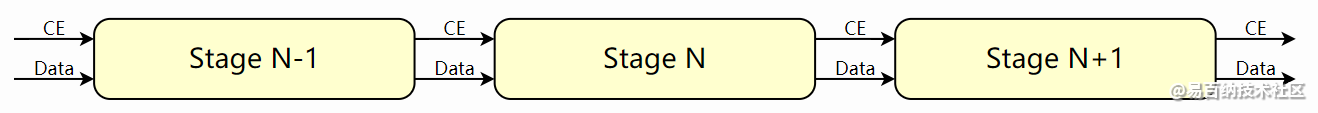

我将把这第二种方法称为 "traveling CE "方法。基本上,通道中的每个阶段都将CE向前传播,如图3所示。

这种方法的基本规则是。

-

每当CE信号为真时,与之相关的数据也必须是有效的。

-

在每个处理阶段结束时,必须产生一个CE信号,以及该阶段的输出数据。

-

CE信号必须被初始化为零。此外,如果要使用任何复位,CE必须在任何复位时被设置为零。数据在复位时是不关心的,但CE线必须被设置为零)。

-

除了在CE信号上,任何东西都不允许改变。因此,只有当i_ce(输入到流水线阶段的CE线)为高电平时,才会参考传入的数据。

-

最后,每一块逻辑都必须随时准备好,等待新的数值进入流水线。这种特殊的流水线策略不能处理停滞。

在Verilog中,这种方法类似于:

initial o_ce = 1'b0;

always @(posedge i_clk)

if (i_reset)

o_ce <= 1'b0;

else

o_ce <= i_ce;

always @(posedge i_clk)

if (i_ce)

o_output <= ... // some function of i_input;

// else *NOTHING*. Nothing is allowed to change except on

// a reset or an i_ce- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

当流水线可以被分离成不超过一个输入有效信号的阶段时,这种方法非常有效。同样,当任何阶段都不依赖于任何来自未来结果的反馈时,这种方法也很有效。换句话说,如果没有任何东西需要等待,那么这种流水线方法的效果就相当好。

这种流水线方法的应用包括逻辑乘法、傅里叶变换处理(例子)、视频处理等等。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:5164次2021-04-11 01:10:40

-

浏览量:11019次2021-04-11 14:45:45

-

浏览量:851次2023-09-20 19:02:57

-

浏览量:4589次2021-06-20 20:10:03

-

浏览量:5071次2020-11-04 09:47:48

-

浏览量:1730次2020-07-02 16:11:35

-

浏览量:14575次2020-12-02 16:57:03

-

浏览量:6037次2022-05-10 09:00:38

-

浏览量:21225次2020-12-10 16:21:29

-

浏览量:14177次2020-12-06 17:48:56

-

浏览量:1927次2019-07-04 12:02:50

-

2020-07-01 11:02:45

-

2024-01-11 15:44:19

-

浏览量:1872次2022-01-14 09:00:21

-

浏览量:7930次2021-02-07 00:59:28

-

浏览量:2285次2020-06-15 11:56:32

-

浏览量:2272次2020-06-18 09:34:12

-

浏览量:658次2023-10-21 13:46:38

-

浏览量:2323次2018-02-11 19:52:32

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友