xavier nx平台调试spi从模式1

1. 前言

想运行spi测试通过连接的spi1和spi3的jetson xavier nx板。

在连接spi1-spi3之前,我连接了spi1的MOSI-MISO (spi3的MOSI-MISO),

并使用spidev_test.c示例进行了测试,以确认tx rx在spi1和spi3上都可以正常工作。

刚开始调试时有以下几个问题

(1)连接spi1和spi3时,如何设置主模式和从模式?

是否更新pinmux吗?

(2)下面两种方法之间的spi1-spi3如何连接?

a. spi1 MISO <-> spi3 MISO / spi1 MOSI <-> spi3 MOSI / spi1 SCK<-> spi3 SCK / spi1 CS0 <-> spi CS0

b. spi1 MISO <-> spi3 MOSI / spi1 MOSI <-> spi3 MISO / spi1 SCK<-> spi3 SCK / spi1 CS0 <-> spi CS0(3)如何做rx在spi 从模式?

当数据进入时是否出现中断?

查看spi示例(spidev_test.c), ioctl(fd, SPI_IOC_MESSAGE(1), &tr)用于检查tx和rx。

这是检查rx的唯一方法吗?

2. 参考方法

(1)配置如下

将tegra124-spi-slave添加到设备树中。

使用两个xavier,一个用于master,另一个用于slave

这是master dts

spi0: spi@3210000 {

compatible = “nvidia,tegra186-spi”;

reg = <0x0 0x03210000 0x0 0x10000>;

interrupts = <0 36 0x04>;

#address-cells = <1>;

#size-cells = <0>;

iommus = <&smmu TEGRA_SID_GPCDMA_0>;

dma-coherent;

dmas = <&gpcdma 15>, <&gpcdma 15>;

dma-names = “rx”, “tx”;

nvidia,dma-request-selector = <&gpcdma 15>;

spi-max-frequency = <65000000>;

nvidia,clk-parents = “pll_p”, “clk_m”;

clocks = <&bpmp_clks TEGRA194_CLK_SPI1>,

<&bpmp_clks TEGRA194_CLK_PLLP_OUT0>,

<&bpmp_clks TEGRA194_CLK_CLK_M>;

clock-names = “spi”, “pll_p”, “clk_m”;

resets = <&bpmp_resets TEGRA194_RESET_SPI1>;

reset-names = “spi”;

status = “okay”;

nvidia,clock-always-on;

spi@0 {

compatible = “spidev”;

reg = <0>;

spi-max-frequency = <65000000>;

status = “okay”;

};

};

这是slave dts

spi0: spi@3210000 {

compatible = “nvidia,tegra124-spi-slave”;

reg = <0x0 0x03210000 0x0 0x10000>;

interrupts = <0 36 0x04>;

#address-cells = <1>;

#size-cells = <0>;

iommus = <&smmu TEGRA_SID_GPCDMA_0>;

dma-coherent;

dmas = <&gpcdma 15>, <&gpcdma 15>;

dma-names = “rx”, “tx”;

nvidia,dma-request-selector = <&gpcdma 15>;

spi-max-frequency = <65000000>;

nvidia,clk-parents = “pll_p”, “clk_m”;

clocks = <&bpmp_clks TEGRA194_CLK_SPI1>,

<&bpmp_clks TEGRA194_CLK_PLLP_OUT0>,

<&bpmp_clks TEGRA194_CLK_CLK_M>;

clock-names = “spi”, “pll_p”, “clk_m”;

resets = <&bpmp_resets TEGRA194_RESET_SPI1>;

reset-names = “spi”;

status = “okay”;

nvidia,clock-always-on;

spi@0 {

compatible = “spidev”;

reg = <0>;

spi-max-frequency = <65000000>;

nvidia,slave-ready-gpio=<&tegra_main_gpio TEGRA194_MAIN_GPIO(T, 3) 0>;

nvidia,enable-hw-based-cs;

status = “okay”;

};

};(2)测试方法

打开SSH终端,首先用下面的命令启动spi从属

./spidev_test -D /dev/spidev0.0 -s 150000 -n100 -g30 -p4 -z在另一个终端中,使用以下命令启动spi master

./spidev_test -D /dev/spidev3.1 -s 150000 -n100 -g30 -p4 -z3. 调试记录

继续以下方式修改dts。

(1)执行/opt/nvidia/jetson-io/jetson-io.py命令,激活spi1、spi3

(2)

sudo dtc -I dts -O dtb -o ~/user-custom.dts /boot/tegra194-p3668-all-p3509-0000-user-custom.dtb(3)修改user-custom.dts

spi@3210000 {

compatible = “nvidia,tegra186-spi”;

reg = <0x0 0x3210000 0x0 0x10000>;

interrupts = <0x0 0x24 0x4>;

#address-cells = <0x1>;

#size-cells = <0x0>;

iommus = <0x2 0x20>;

dma-coherent;

dmas = <0x19 0xf 0x19 0xf>;

dma-names = “rx”, “tx”;

spi-max-frequency = <0x3dfd240>;

nvidia,clk-parents = “pll_p”, “clk_m”;

clocks = <0x4 0x87 0x4 0x66 0x4 0xe>;

clock-names = “spi”, “pll_p”, “clk_m”;

resets = <0x5 0x5b>;

reset-names = “spi”;

status = “okay”;

linux,phandle = <0xf2>;

phandle = <0xf2>;

spi@0 {

compatible = “spidev”;

reg = <0x0>;

spi-max-frequency = <0x2faf080>;

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <0x10>;

nvidia,tx-clk-tap-delay = <0x0>;

};

};

spi@1 {

compatible = “spidev”;

reg = <0x1>;

spi-max-frequency = <0x2faf080>;

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <0x10>;

nvidia,tx-clk-tap-delay = <0x0>;

};

};

};

spi@3230000 {

compatible = “nvidia,tegra186-spi-slave”;

reg = <0x0 0x3230000 0x0 0x10000>;

interrupts = <0x0 0x26 0x4>;

#address-cells = <0x1>;

#size-cells = <0x0>;

iommus = <0x2 0x20>;

dma-coherent;

dmas = <0x19 0x11 0x19 0x11>;

dma-names = “rx”, “tx”;

spi-max-frequency = <0x3dfd240>;

nvidia,clk-parents = “pll_p”, “clk_m”;

clocks = <0x4 0x89 0x4 0x66 0x4 0xe>;

clock-names = “spi”, “pll_p”, “clk_m”;

resets = <0x5 0x5d>;

reset-names = “spi”;

status = “okay”;

linux,phandle = <0xf4>;

phandle = <0xf4>;

spi@0 {

compatible = “spidev”;

reg = <0x0>;

spi-max-frequency = <0x2faf080>;

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <0x10>;

nvidia,tx-clk-tap-delay = <0x0>;

};

};

spi@1 {

compatible = “spidev”;

reg = <0x1>;

spi-max-frequency = <0x2faf080>;

controller-data {

nvidia,enable-hw-based-cs;

nvidia,rx-clk-tap-delay = <0x10>;

nvidia,tx-clk-tap-delay = <0x0>;

};

};

};(4)

sudo dtc -I dts -O dtb -o /boot/tegra194-p3668-all-p3509-0000-user-custom.dtb ~/user-custom.dts(5)reboot

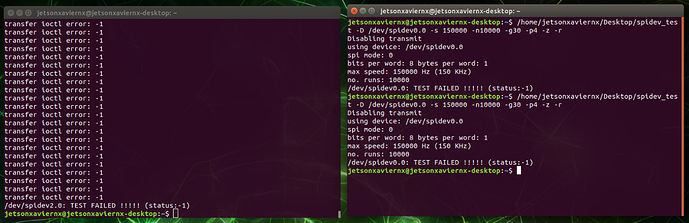

通过以这种方式修改dts, spi1(master, spidev0.0)、spi3(slave, spidev2.0)被连接并按如下方式执行。

/spidev_test -D /dev/spidev2.0 -s 150000 -n10000 -g30 -p4 -z

./spidev_test -D /dev/spidev0.0 -s 150000 -n10000 -g30 -p4 -z结果如图所示

当我在从模式运行它,一个传输错误发生和主测试失败。

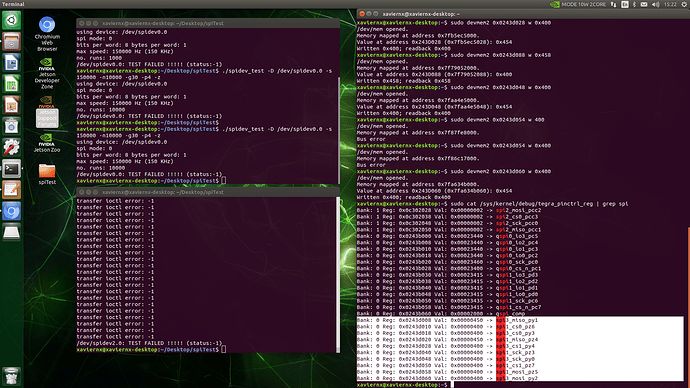

(5)让devmem2读取那些REG来确认设置。

使用了devmem2来临时更改寄存器值。

检查dmesg时,出现以下错误。

[ 280.340212] spi-tegra124-slave 3230000.spi: Tx is not supported in mode 0

[ 280.340215] spi-tegra124-slave 3230000.spi: spi can not start transfer, err -22

[ 280.340301] spi_master spi2: failed to transfer one message from queue

- 分享

- 举报

暂无数据

暂无数据-

浏览量:8042次2021-06-09 14:29:23

-

浏览量:8512次2021-06-09 14:49:23

-

浏览量:8205次2021-05-11 17:51:48

-

2021-05-06 16:03:00

-

浏览量:6740次2021-07-09 15:17:28

-

浏览量:9968次2021-05-19 17:32:00

-

浏览量:8513次2021-06-04 16:25:58

-

浏览量:9420次2021-05-14 14:43:43

-

浏览量:10536次2021-05-26 14:17:15

-

浏览量:9991次2021-04-27 17:56:41

-

浏览量:6686次2021-06-03 17:33:36

-

浏览量:12260次2021-05-06 16:22:01

-

浏览量:5643次2021-07-09 15:23:33

-

浏览量:7717次2021-05-11 17:04:57

-

浏览量:5660次2021-07-09 15:20:08

-

浏览量:5616次2021-05-10 17:48:42

-

浏览量:11212次2021-06-11 11:24:45

-

浏览量:7759次2021-05-20 16:37:42

-

浏览量:8181次2021-05-20 17:08:14

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

free-jdx

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友