FPGA的设计艺术(27)状态机简易实现(HDL描述)

前言

状态机是逻辑设计中接触最多的内容,可谓是各种场合的热点,本文从基础讲起,直接触及最核心的几个要素,更多内容,请参考更多英文网站及文献。

状态机介绍

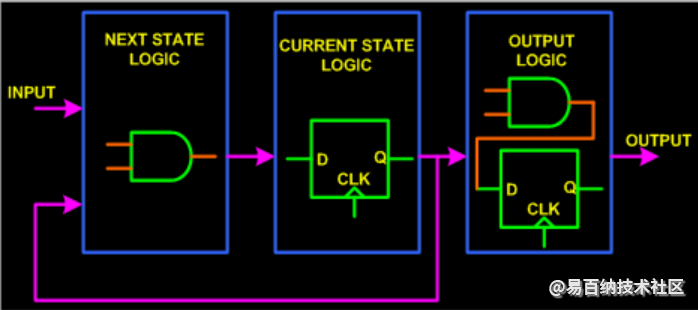

基本上,FSM由组合,顺序和输出逻辑组成。组合逻辑用于确定FSM的下一个状态,顺序逻辑用于存储FSM的当前状态。输出逻辑是组合逻辑和顺序逻辑的混合,如下图所示。

状态机的描述方式

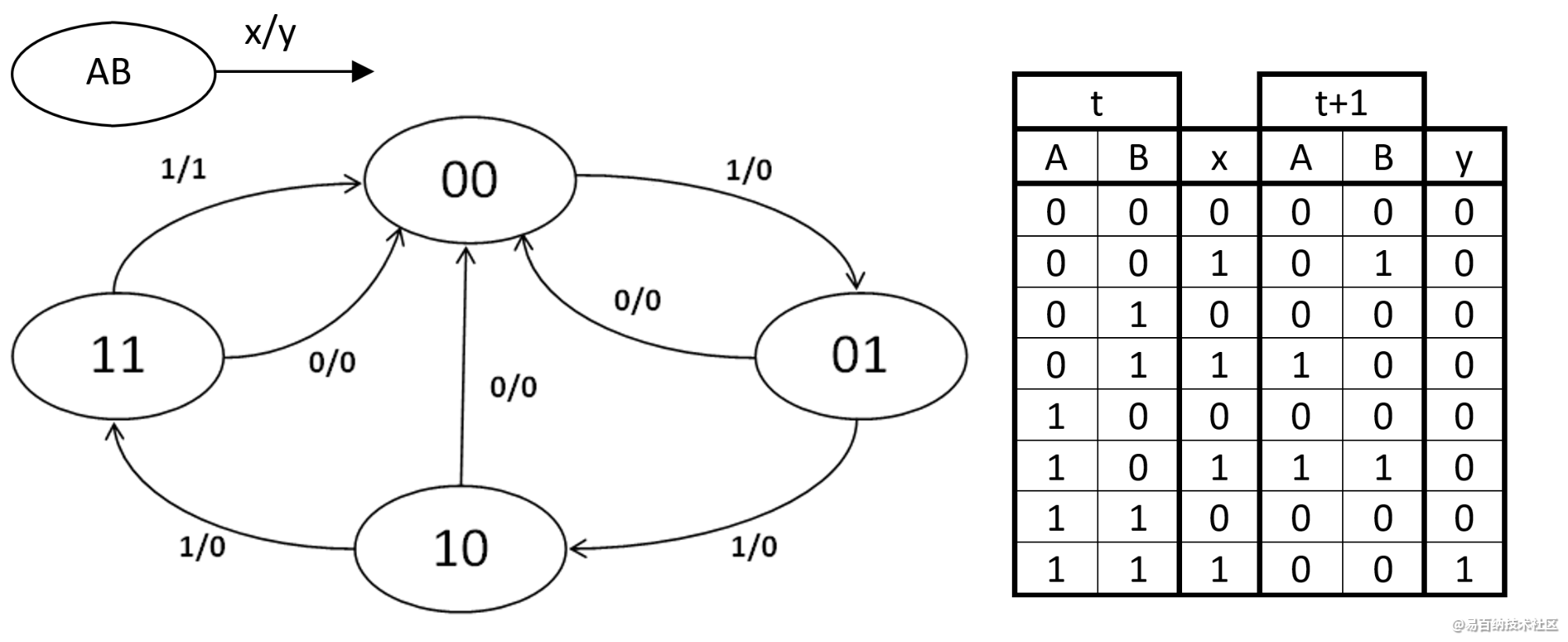

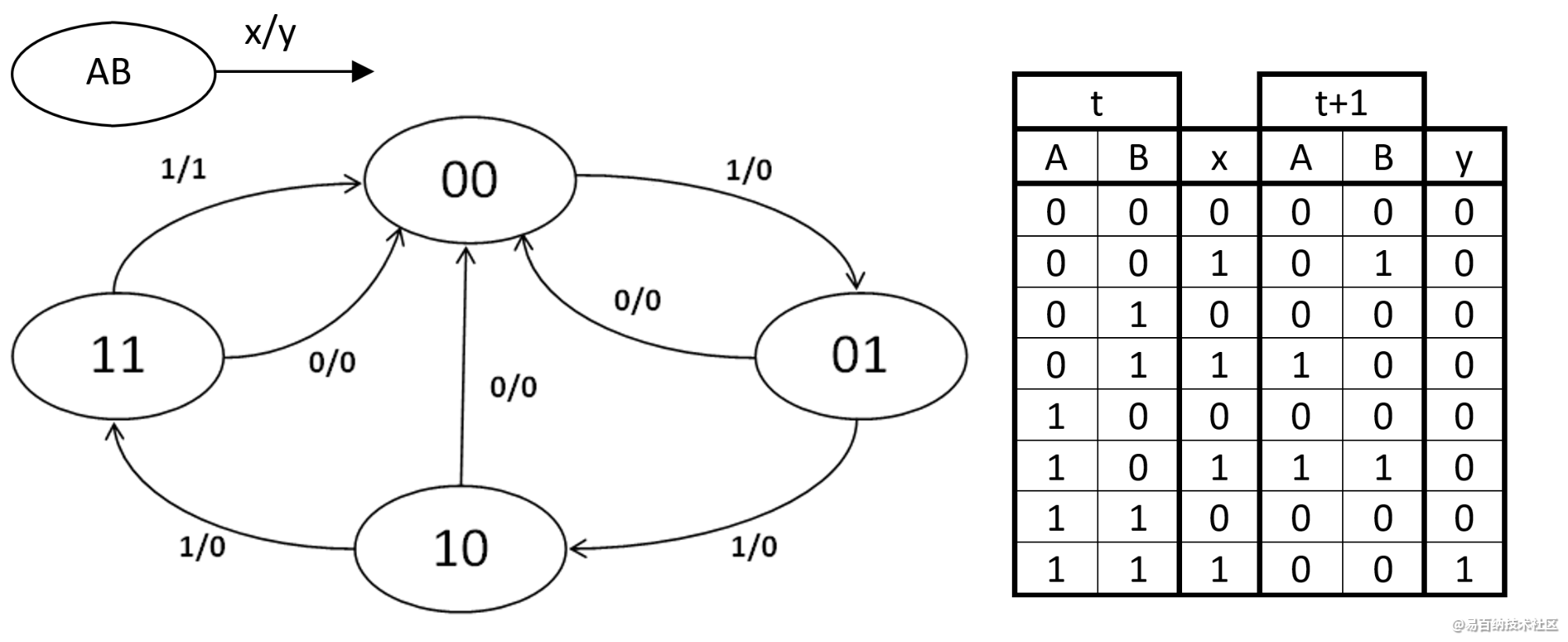

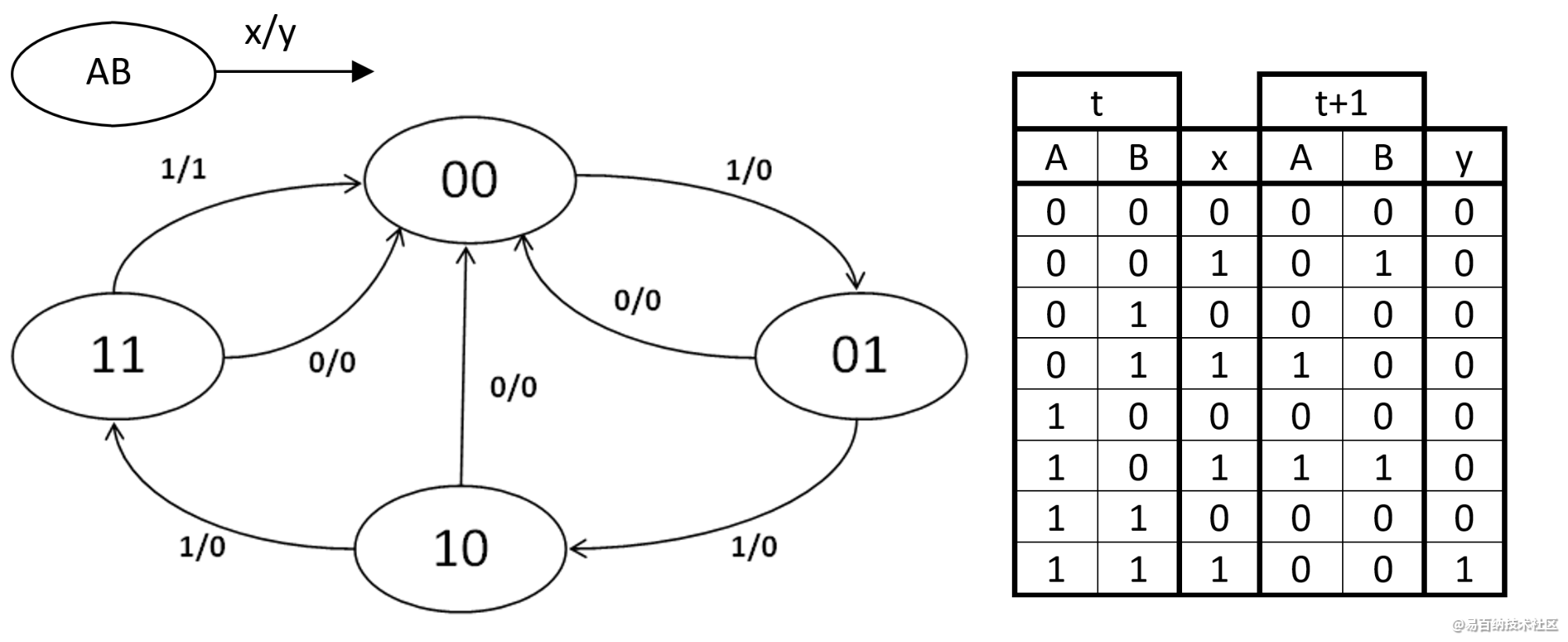

有限状态机的描述方式很多,但是最流行的两个是状态图和状态表。两种表示形式的示例如图所示。

而就这两种而言,最最常用也最直观的还是状态转移图。

状态机的类型

状态机有两种类型:

-

Mealy状态机:其输出取决于当前状态和当前输入。在上图中,整体上就是一个Mealy型状态机。

-

Moore状态机:其输出仅取决于当前状态。在上图中,当蓝色方框内电路去除时,电路变为Moore状态机。

根据需要,我们可以选择状态机的类型。但总的来说,大多数情况下,我们都会使用Mealy型状态机。

同样,使用上图的例子:

输出y不仅取决于当前状态,还取决于输入x,因此这是一个Mealy状态机。

状态机的编码方式

由于我们需要在数字电路中表示状态机,我们可以选择以下几种方式的一种来对我们的状态进行编码:

二进制编码:每个状态都用二进制代码表示(即000、001、010 ....)

格雷编码:每个状态都用格雷码表示(即000、001、011等)

独热码:只有一位为高,其余位为低(即0001、0010、0100、1000)

独冷码:只有一位是低的,其余的都是高的(即1110,1101,1011,0111)

我们可以在逻辑编码时,使用任意一种编码,但有时候综合结果并非所想,这时我们需要使用综合属性来选择使用哪种编码方式。

推荐阅读:

Vivado 随笔(3) 其他综合属性 dont_touch、fsm_encoding?

状态机的实现示例

拿这个例子而言,我们直接知道了状态转移图,根据状态转移图可以使用HDL语言描述这个状态转移图,描述方式灵活多变,简洁易懂,容易实现即可:

状态机的一个很好的构造是Case 语句。每种情况的主体都应检查状态变量及其期望的行为。以下代码显示了此结构。

case (state)

STATE_0: // Code for State 0

STATE_1: // Code for State 1

// ...

STATE_N: // Code for State N

endcase- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

实际实现为:

module MyFSM(

input clk,

input x,

output y);

reg [1:0] state;

assign y = state[1] & state[0] & x;

always @ (posedge clk)

case (state)

2'b00: state <= x?2'b01:2'b00;

2'b01: state <= x?2'b10:2'b00;

2'b10: state <= x?2'b11:2'b00;

2'b11: state <= 2'b00;

endcase

endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

注意,这里的输出使用了组合逻辑实现,也可以使用时序逻辑来实现,看自己期待哪种结果,如果使用时序逻辑,其结果也就是多一个时钟的问题,后续的设计可适当匹配, 这都不是事。

例如:

module MyFSM(

input clk,

input x,

output reg y);

reg [1:0] state;

always@(posedge clk) begin

y <= state[1] & state[0] & x;

end

// assign y = state[1] & state[0] & x;

always @ (posedge clk)

case (state)

2'b00: state <= x?2'b01:2'b00;

2'b01: state <= x?2'b10:2'b00;

2'b10: state <= x?2'b11:2'b00;

2'b11: state <= 2'b00;

endcase

endmodule- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

这也相当于对组合逻辑输出结果打一拍。这样其实对于逻辑设计来说更常见,不会出现非预期的结果,大家其实心里都默认时序输出。仿真时,也是这样预期的。

参考资料

https://inst.eecs.berkeley.edu/~cs150/sp12/resources/FSM.pdf

https://www.allaboutcircuits.com/technical-articles/creating-finite-state-machines-in-verilog/

- 分享

- 举报

暂无数据

暂无数据-

浏览量:5446次2021-03-14 01:12:39

-

浏览量:2722次2020-12-07 10:07:25

-

浏览量:4625次2021-04-27 00:05:09

-

浏览量:5402次2021-03-20 00:58:29

-

浏览量:5982次2021-02-14 01:58:16

-

浏览量:7956次2021-02-07 00:59:28

-

浏览量:5218次2021-03-14 01:58:15

-

浏览量:1365次2023-04-11 15:24:20

-

浏览量:5845次2021-04-27 00:06:35

-

浏览量:9398次2021-02-20 17:50:13

-

浏览量:4599次2021-06-20 20:10:03

-

浏览量:4202次2021-03-13 01:55:14

-

浏览量:4290次2021-03-12 23:39:20

-

浏览量:5177次2021-05-23 23:50:14

-

浏览量:3705次2019-11-21 09:05:53

-

浏览量:6794次2021-03-14 02:34:44

-

浏览量:7136次2021-03-15 23:18:36

-

浏览量:12028次2021-05-23 01:13:25

-

浏览量:9289次2021-03-21 22:58:26

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友