技术专栏

nvidia xavier nx平台SPI接口调试记录

,#### 1. 前言

现有的硬件使用CS0和CS1在一个SPI上连接一个FRAM和一个TPM模块。

在Jetson Nano上运行ok。

Xavier NX模块的问题是硬件控制芯片选择信号(CS0)的不同行为。

以下描述适用于FRAM, TPM是没有问题的,是两种配置。

SPI由“ioctl”函数控制,利用了“cs_change”选项。

FRAM需要操作码,24位地址和内存数据。

从操作码到数据流结束,CS必须保持低。

下面的代码在Nano上运行良好:

uint8_t tx[4] = { OPCODE_WRITE };

tx[1] = (uint8_t) (address >> 16) & 0xFF;

tx[2] = (uint8_t) (address >> 8) & 0xFF;

tx[3] = (uint8_t) (address & 0xFF);

struct spi_ioc_transfer tr = { .tx_buf = (unsigned long) tx, .rx_buf = 0,

.len = 4, .delay_usecs = delay, .speed_hz = 0, .bits_per_word = 0,

.cs_change = 0, };

struct spi_ioc_transfer tr2 = { .tx_buf = (unsigned long) send, .rx_buf = 0,

.len = len, .delay_usecs = delay, .speed_hz = 0, .bits_per_word = 0,

.cs_change = 1, };

ret = ioctl(fd, SPI_IOC_MESSAGE(1), &tr);

if (ret < 0)

{

spi_fram_debug_out("can't send spi message");

}

ret = ioctl(fd, SPI_IOC_MESSAGE(1), &tr2);2.查看波形

cs_change选项在Nano上可以正常工作,但在Xavier NX上不行。

我认为问题是由DTS文件中的设置引起的。

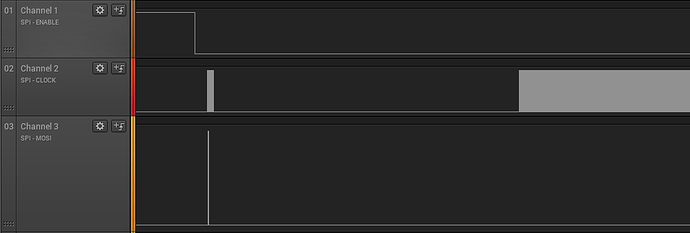

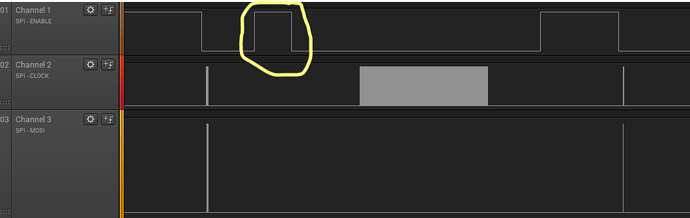

为了说明这个问题,下面是Nano设置中的捕获:

3.修改SPI dts

尝试将spi*_xxx添加到dts中

header-40pin-pinmux {

phandle = <0x179>;

linux,phandle = <0x179>;

pin37 {

nvidia,lpdr = <0x0>;

nvidia,io-high-voltage = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x1>;

nvidia,pins = "spi3_mosi_py2";

nvidia,function = "spi3";

};

pin28 {

nvidia,lpdr = <0x1>;

nvidia,io-high-voltage = <0x1>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x0>;

nvidia,pins = "gen2_i2c_scl_pcc7";

nvidia,function = "i2c2";

};

pin27 {

nvidia,lpdr = <0x1>;

nvidia,io-high-voltage = <0x1>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x0>;

nvidia,pins = "gen2_i2c_sda_pdd0";

nvidia,function = "i2c2";

};

pin26 {

nvidia,lpdr = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x2>;

nvidia,pins = "spi1_cs1_pz7";

nvidia,function = "spi1";

};

pin24 {

nvidia,lpdr = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x2>;

nvidia,pins = "spi1_cs0_pz6";

nvidia,function = "spi1";

};

pin23 {

nvidia,lpdr = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x1>;

nvidia,pins = "spi1_sck_pz3";

nvidia,function = "spi1";

};

pin22 {

nvidia,lpdr = <0x0>;

nvidia,io-high-voltage = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x1>;

nvidia,pins = "spi3_miso_py1";

nvidia,function = "spi3";

};

pin21 {

nvidia,lpdr = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x1>;

nvidia,pins = "spi1_miso_pz4";

nvidia,function = "spi1";

};

pin19 {

nvidia,lpdr = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x1>;

nvidia,pins = "spi1_mosi_pz5";

nvidia,function = "spi1";

};

pin18 {

nvidia,lpdr = <0x0>;

nvidia,io-high-voltage = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x2>;

nvidia,pins = "spi3_cs0_py3";

nvidia,function = "spi3";

};

pin16 {

nvidia,lpdr = <0x0>;

nvidia,io-high-voltage = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x2>;

nvidia,pins = "spi3_cs1_py4";

nvidia,function = "spi3";

};

pin13 {

nvidia,lpdr = <0x0>;

nvidia,io-high-voltage = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x1>;

nvidia,pins = "spi3_sck_py0";

nvidia,function = "spi3";

};

pin10 {

nvidia,lpdr = <0x0>;

nvidia,io-high-voltage = <0x0>;

nvidia,enable-input = <0x1>;

nvidia,tristate = <0x1>;

nvidia,pull = <0x2>;

nvidia,pins = "uart1_rx_pr3";

nvidia,function = "uarta";

};

pin8 {

nvidia,lpdr = <0x0>;

nvidia,io-high-voltage = <0x0>;

nvidia,enable-input = <0x0>;

nvidia,tristate = <0x0>;

nvidia,pull = <0x0>;

nvidia,pins = "uart1_tx_pr2";

nvidia,function = "uarta";

};

};修改完后测试仍没变化

4. 回环测试

通过loopback测试SPI成功。

spi mode: 0x0

bits per word: 8

max speed: 500000 Hz (500 KHz)

TX | FF FF FF FF FF FF 40 00 00 00 00 95 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF F0 0D | ......@....?.................?

RX | FF FF FF FF FF FF 40 00 00 00 00 95 FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF F0 0D | ......@....?.................?

5. 原因分析

TPM在Nano和Xavier NX这两个平台上都运行良好。

FRAM在Nano上运行,但在Xavier NX上没有。

软件完全一样。

因此,我不确定建议的环回测试可能已经确定了什么问题,因为CS线没有涉及。

这都是关于上面所看到的帧- cs上的额外“故障”。

基本上硬件CS工作,但选项" cs_change = 0 "之前的ioctl被忽略在Xavier上

与此同时,我们对此进行了更深入的研究,但仍然没有解决方案。我们已经相信这种行为与DTS配置无关,因为CS引脚的硬件控制基本工作。

6. 逻辑分析仪测试

7. 验证SPI补丁

Nano和Xavier NX都使用了相同的spi-tegra114.c源。

不理解的是,Nano在这个代码基础上运行得很好,但Xavier NX不行。

据我所知,没有针对不同平台的编译器开关。

查阅相关资料

添加如下patch

diff --git a/drivers/spi/spi-tegra114.c b/drivers/spi/spi-tegra114.c

index d6e50c9..cc6c820 100644

--- a/drivers/spi/spi-tegra114.c

+++ b/drivers/spi/spi-tegra114.c

@@ -1455,10 +1455,8 @@ static int tegra_spi_transfer_one_message(struct spi_master *master,

msg->actual_length += xfer->len;

complete_xfer:

- if (prefer_last_used_cs)

cmd1 = tspi->command1_reg;

- else

- cmd1 = tspi->def_command1_reg;

+

if (ret < 0 || skip) {

if (cstate && cstate->cs_gpio_valid)

gpio_set_value(spi->cs_gpio, gval);添加此patch后

重新刷新kernel后,验证ok

声明:本文内容由易百纳平台入驻作者撰写,文章观点仅代表作者本人,不代表易百纳立场。如有内容侵权或者其他问题,请联系本站进行删除。

红包

95

7

评论

打赏

- 分享

- 举报

评论

0个

手气红包

暂无数据

暂无数据相关专栏

-

浏览量:10907次2021-06-08 17:32:00

-

浏览量:8042次2021-06-09 14:29:23

-

浏览量:8512次2021-06-09 14:49:23

-

浏览量:7759次2021-05-20 16:37:42

-

浏览量:8180次2021-05-20 17:08:14

-

浏览量:10036次2021-05-25 17:31:40

-

浏览量:9968次2021-05-19 17:32:00

-

浏览量:8708次2021-05-25 15:32:16

-

浏览量:9419次2021-05-14 14:43:43

-

浏览量:10535次2021-05-26 14:17:15

-

浏览量:9990次2021-04-27 17:56:41

-

2021-05-06 16:03:00

-

浏览量:12258次2021-05-06 16:22:01

-

浏览量:7014次2021-04-21 17:42:58

-

浏览量:7713次2021-05-11 17:04:57

-

浏览量:5614次2021-05-10 17:48:42

-

浏览量:9164次2021-03-16 14:44:24

-

2021-04-23 15:54:21

-

浏览量:7884次2021-07-31 15:26:23

置顶时间设置

结束时间

删除原因

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

打赏作者

free-jdx

您的支持将鼓励我继续创作!

打赏金额:

¥1

¥5

¥10

¥50

¥100

支付方式:

微信支付

微信支付

举报反馈

举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

审核成功

发布时间设置

发布时间:

请选择发布时间设置

是否关联周任务-专栏模块

审核失败

失败原因

请选择失败原因

备注

请输入备注

微信扫码分享

微信扫码分享 QQ好友

QQ好友