FPGA的设计艺术(7)STA实战之SmartTime时序约束及分析示例(II)

前言

本文续FPGA的设计艺术(6)STA实战之SmartTime时序约束及分析示例(I),分析了时钟的不确定性,多周期路径,以及门控时钟的STA分析方法。可以使用各大厂家的时序分析工具,大多数都自带GUI界面,通过这些界面可以进行这些类似的分析。

在SmartTime中分析具有抖动/时钟不确定性的设计

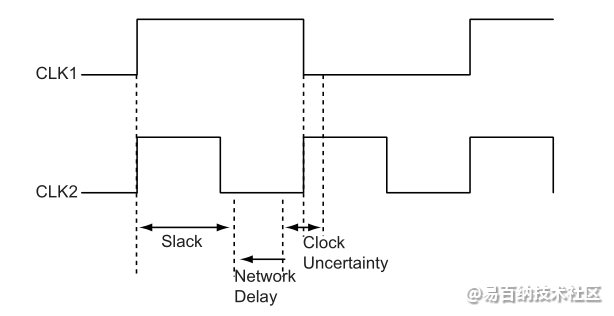

SmartTime在跨时钟域时序分析期间使用启动的时钟沿与捕获的时钟沿之间的关系。但是,时钟生成和时钟分配系统的非理想性(也称为抖动)表现为时钟沿到达的不确定性。 SmartTime中的时钟不确定性约束使您可以指定不同时钟之间的这些不确定性。时钟到时钟的不确定性定义了两个时钟波形之间的时序不确定性或最大时钟偏斜。

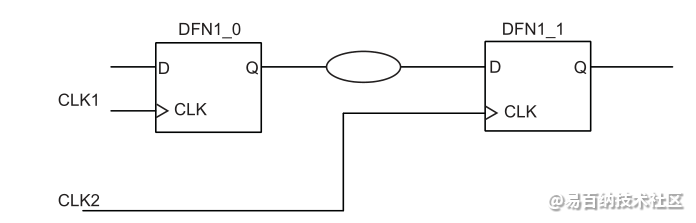

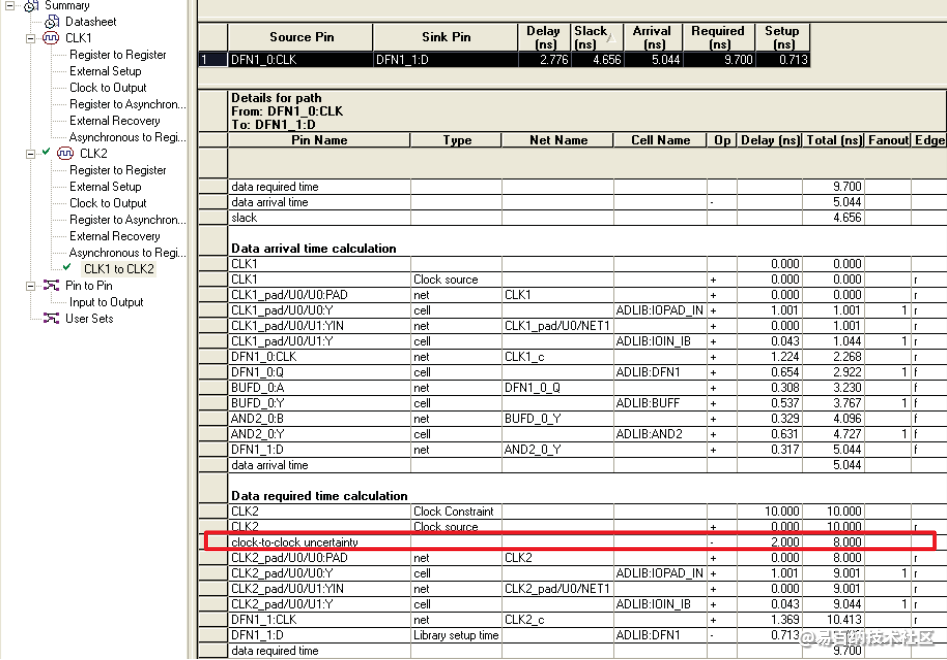

一个具有两个外部时钟CLK1和CLK2的设计示例如下图所示。假设这两个时钟的跟踪抖动为2 ns。在时序分析期间,可以将此跟踪抖动添加为clock_uncertainty。

分析具有时钟不确定性的设计

- 指定两个参考时钟的时钟频率和其他属性。

对于的约束语句为:

create_clock -name{CLK2}-period 10.000-waveform{0.000 5.000}{CLK2}

create_clock -name{CLK1}-period 10.000-waveform{0.000 5.000}{CLK1}- 1

- 2

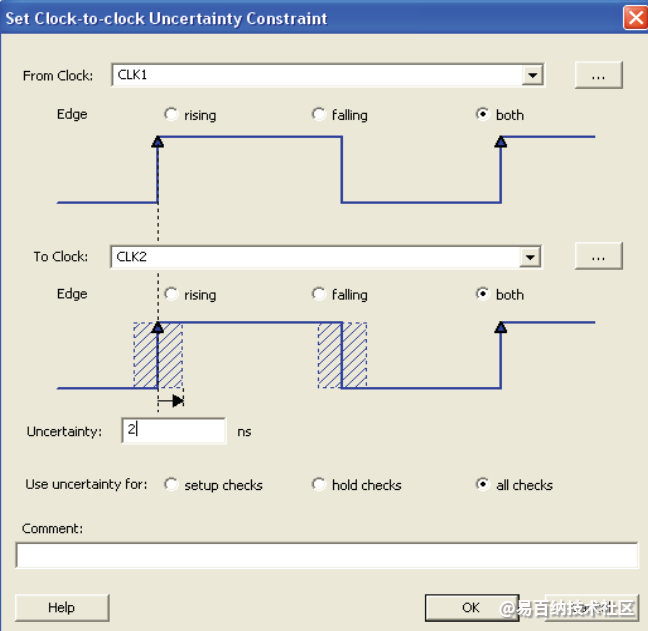

- 在CLK1和CLK2之间施加2 ns的时钟不确定性,以添加时钟到时钟的不确定性约束。

对应的约束语句为:

set_clock_uncertainty1-from{CLK1}-to{CLK2}- 1

- 启用跨时钟域分析。SmartTime时序分析视图将时钟不确定性约束用于时序检查。下图显示了如何在建立检查中使用时钟到时钟不确定性约束。

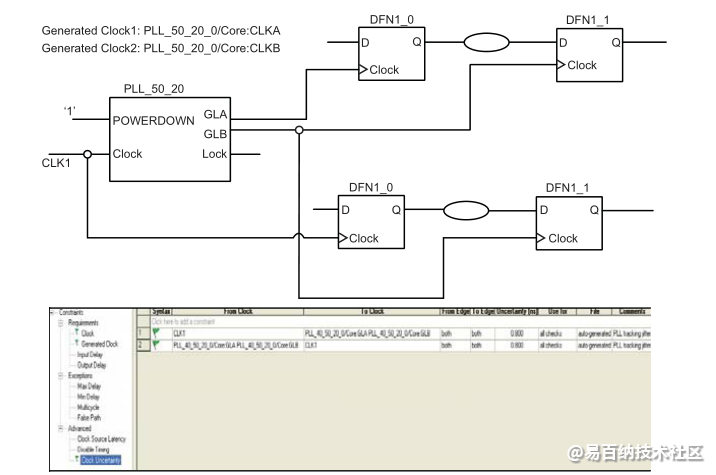

注意:如果在设计中使用PLL,则SmartTime会自动在PLL参考时钟和PLL输出时钟之间添加时钟不确定性。但是,SmartTime不会在输出时钟之间增加时钟不确定性(输出时钟是从同一VCO时钟生成的)。下图显示了一个设计示例,该示例具有来自PLL参考时钟和PLL输出时钟以及PLL输出时钟的数据路径。当添加参考时钟约束时,该工具会自动添加生成的时钟和时钟不确定性约束。

create_clock -name{CLK1}-period 25.000-waveform{0.000 12.500}{CLK1}

create_generated_clock -name{PLL_40_50_20_0/Core:GLA}-divide_by40 -

multiply_by20 -source{PLL_40_50_20_0/Core:CLKA}{PLL_40_50_20_0/Core:GLA}

create_generated_clock -name{PLL_40_50_20_0/Core:GLB}-divide_by16 -

multiply_by20 -source{PLL_40_50_20_0/Core:CLKA}{PLL_40_50_20_0/Core:GLB}- 1

- 2

- 3

- 4

- 5

分析具有单个时钟域的多周期路径

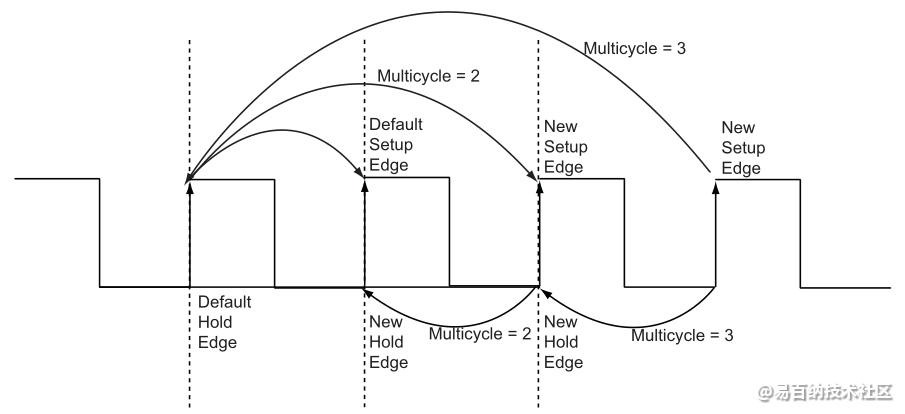

多周期路径是可能需要多个时钟周期才能将数据锁存到捕获寄存器的数据路径。多周期路径约束使您可以将捕获的时钟沿向前或向后移动启动的时钟沿。将多周期约束应用于建立(setup)时间时,它会通过将捕获的(目标)时钟沿向右移动来修改建立关系。

同样,将多周期约束应用于保持时,它会修改保持关系,将启动的(源)时钟沿更改为左侧。应用多循环路径约束需要设计知识。

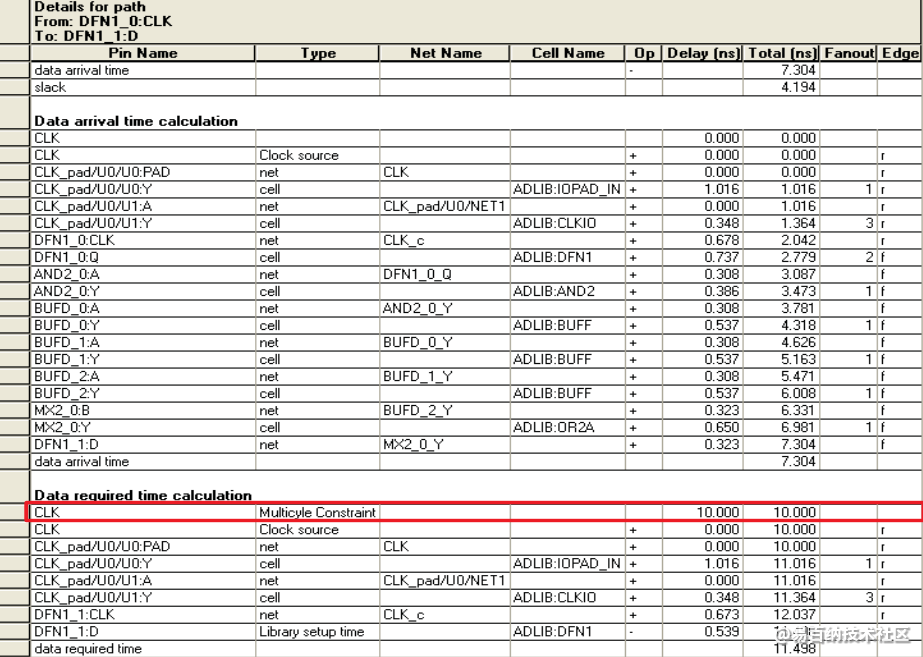

下图显示了一个设计示例,其中假定从DFN1_0到DFN1_1的路径是多周期路径。下例显示了如何在此设计上应用和分析多周期约束。

使用SmartTime分析多周期路径

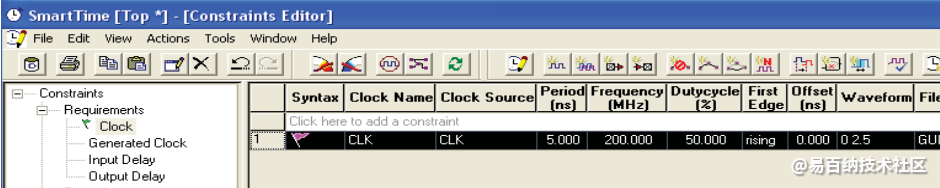

- 指定参考时钟的时钟频率和其他属性。

对应的约束语句为:

create_clock -name{CLK}-period 5.000-waveform{0.000 2.500}{CLK}- 1

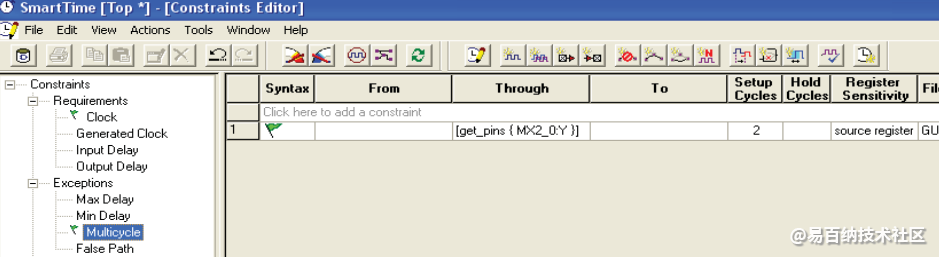

- 确定多周期的直通引脚并应用多周期约束。

对应的约束语句为:

set_multicycle_path-setup2 -through [get_pins{MX2_0:Y}]- 1

SmartTime时序分析视图将上述多周期约束用于时序检查。图31显示了如何在设置检查中使用多周期约束。

至于跨时钟域的多周期路径时序分析,这里就不提供了。可参考FPGA的设计艺术(6)STA实战之SmartTime时序约束及分析示例(I)

分析方法一致。

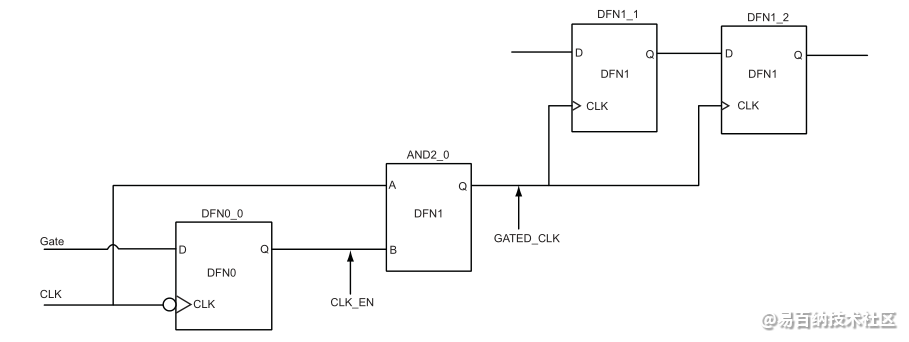

门控时钟分析

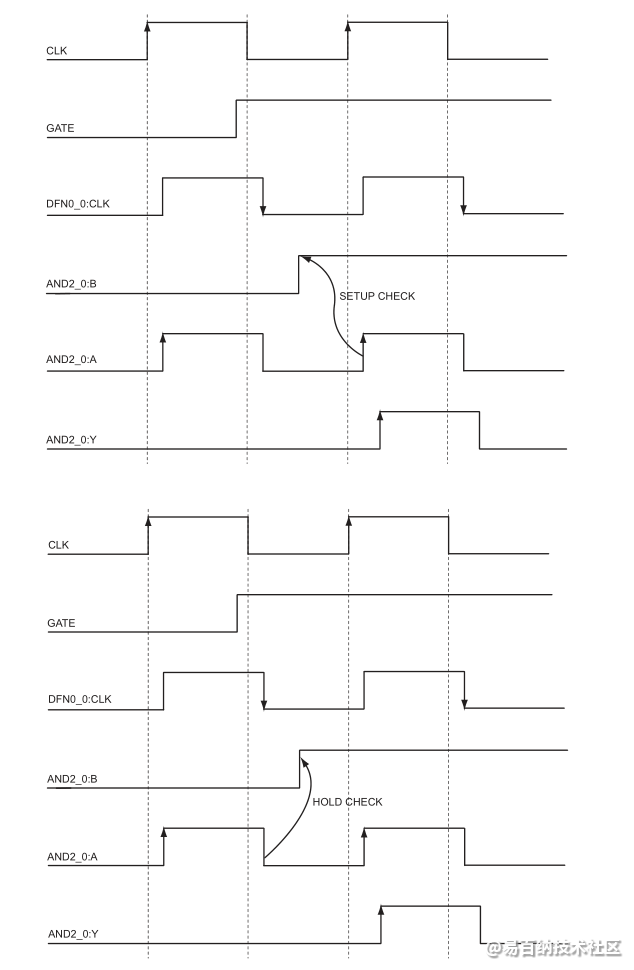

当时钟路径包含除反相器或缓冲器以外的逻辑时,将产生门控时钟信号。 SmartTime时序分析视图中的默认设置为参考时钟启用建立和保持分析。但是,它不对选通信号和时钟之间的选通单元进行时序分析。当时钟脉冲通过选通单元时,门控信号可能会发生跃迁,这可能导致削波和杂散时钟脉冲。下面提供有关手动执行此时序分析的详细信息。下图显示了门控时钟和时序波形的最通用电路。

仅当CLK_EN为高电平时,GATED_CLK信号才通过AND2_0传播到下游触发器。为了避免毛刺,DFN0_0的输出应在CLK的下降沿到达AND2_0的输入A之后,下一个上升的CLK到达AND2_0的输入A之前到达AND2_0的输入B。建立检查分析应使用以下时序计算:

- 发射沿:数据路径从CLK开始,经过DFN0_0(D-> Q),然后在AND2_0:B引脚处结束。上升沿和下降沿时序都必须计算,并且将使用较大的结果。

- 捕获的边沿:时钟路径始于CLK,结束于AND2_0:A引脚。必须仅检查时序的上升沿。

保持检查分析应使用以下时序:

- 启动边沿:数据路径从CLK开始,经过DFN0_0(D-> Q),并在AND2_0:B引脚处结束。时序必须针对DFN1_0 FF的时钟下降沿,然后针对AND2_0门的上升沿或下降沿,以较短者为准。

- 捕获的边沿:时钟路径始于CLK,结束于AND2_0:A引脚。时序必须用于延迟时钟的下降沿。

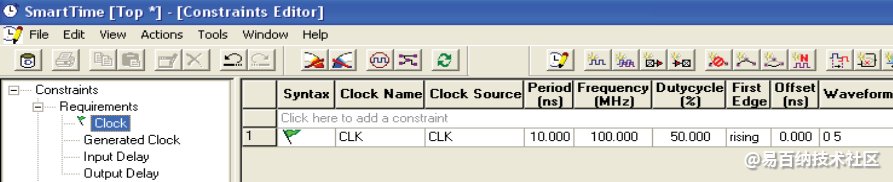

门控时钟分析

- 指定参考时钟频率和其他属性。

对应的约束语句为:

create_clock -name{CLK}-period 10.000-waveform{0.000 5.000}{CLK}- 1

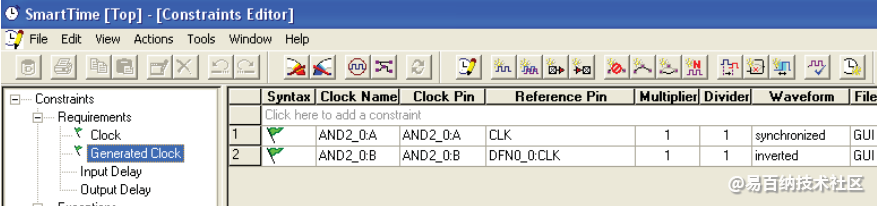

- 将AND2_0:A和AND2_0:B标识为生成的时钟,并应用生成的时钟约束。

对应的约束语句为:

create_generated_clock -name{AND2_0:A}-divide_by1 -source{CLK}{AND2_0:A}

create_generated_clock -name{AND2_0:B}-divide_by1 -invert -

source{DFN0_0:CLK}{AND2_0:B}- 1

- 2

- 3

- 启用跨时钟域分析。

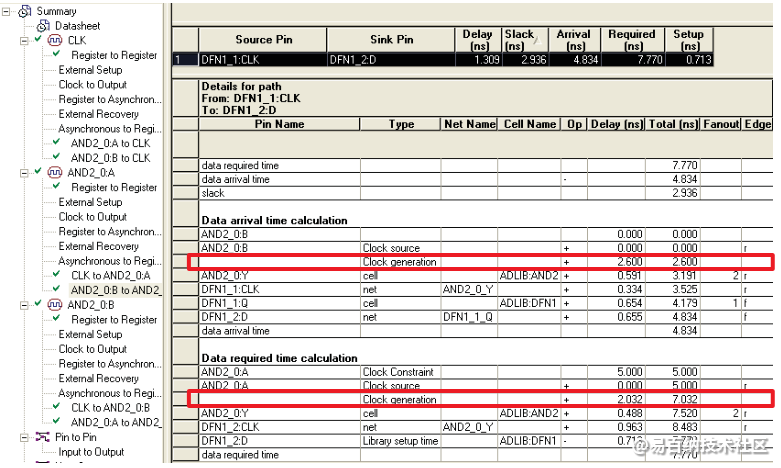

SmartTime最大延迟分析视图显示参考时钟和AND2_0:A至AND2_0:B时钟域。您需要从扩展的数据路径获取延迟值,并在门控单元上进行建立和保持计算。下图显示了扩展路径之一以及门控单元上的建立和保持计算。

Setup check = Capture edge - launch edge = (10 + 2.032) - (5 + 2.6) = 4.432 ns.

Hold check = Capture edge - launch edge = (5 + 2.6) - (5 + 2.032) = 0.56 ns.

注意:您需要使用最小延迟分析视图下的延迟号进行类似的计算。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:6286次2021-02-21 16:01:28

-

浏览量:10043次2021-02-20 22:37:06

-

浏览量:7187次2021-02-21 01:20:21

-

浏览量:9410次2021-02-20 17:50:13

-

浏览量:5222次2021-03-14 01:58:15

-

浏览量:6173次2021-03-22 01:26:53

-

浏览量:5600次2021-03-17 23:24:53

-

浏览量:5991次2021-02-14 01:58:16

-

浏览量:7974次2021-02-07 00:59:28

-

浏览量:5847次2021-04-27 00:06:35

-

浏览量:5063次2021-03-18 22:57:24

-

浏览量:4603次2021-06-20 20:10:03

-

浏览量:4207次2021-03-13 01:55:14

-

浏览量:4295次2021-03-12 23:39:20

-

浏览量:5179次2021-05-23 23:50:14

-

浏览量:5455次2021-03-14 01:12:39

-

浏览量:4630次2021-04-27 00:05:09

-

浏览量:4748次2022-08-17 09:01:18

-

浏览量:6802次2021-03-14 02:34:44

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友