FPGA的设计艺术(6)STA实战之SmartTime时序约束及分析示例(I)

前言

FPGA进行时序分析通常使用厂家的编译工具,进行时序分析,但是万变不离其宗,时序分析的知识通常都是通用的,原理都是一致的。下面根据SmartTime的资料来看下时序分析的实际操作是如何的,这在其他工具上通常也是可以找到的。

SmartTime时序分析概述

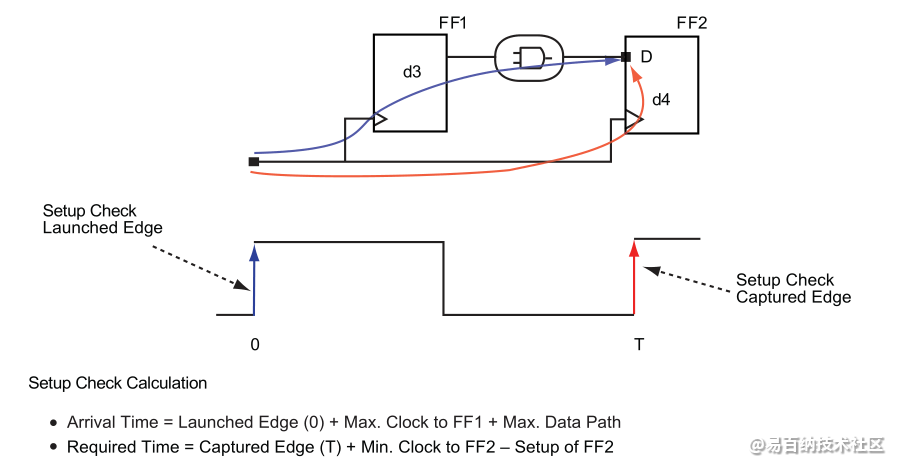

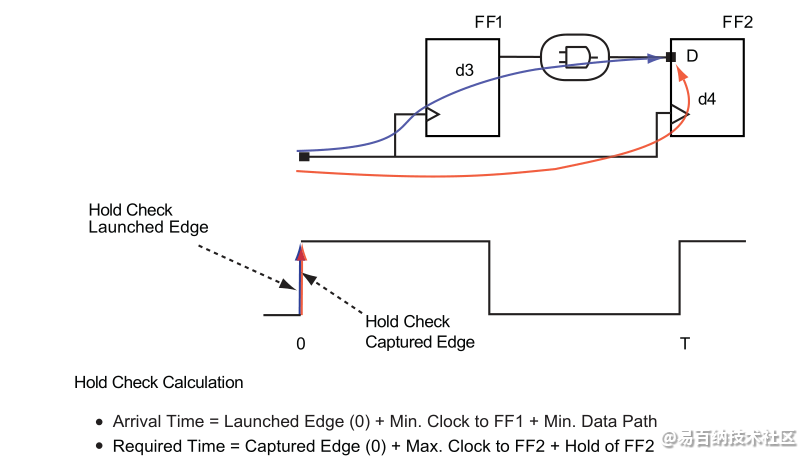

SmartTime是用于SmartFusion®可定制的片上系统(cSoC),RTAX™-S / SL,Fusion®,IGLOO®,ProASIC®3,Axcelerator®,eX和SXA系列的门级静态时序分析(STA)工具。 SmartTime图形用户界面(GUI)提供了用于静态时序分析的SmartTime时序分析器和用于在设计中应用SDC约束的SmartTime约束编辑器。 SmartTime时序分析器具有两个时序分析视图:最大延迟分析和最小延迟分析。最大延迟分析视图检查建立时序,最小延迟分析视图检查保持时序。 SmartTime约束编辑器使您可以创建,查看和编辑所选方案的时序约束,以用于SmartTime时序分析。 SmartTime中的设置检查涉及将最新的数据到达时间(最长的数据路径延迟)与最早的所需时间(最短的时钟路径延迟)进行比较。 SmartTime中的保持检查包括将最早的数据到达时间(最短的数据路径延迟)与最新的所需时间(最长的时钟路径延迟)进行比较。建立和保持检查都将计算相对于发射沿和捕获沿的时序延迟,如下图所示。这是所有时序分析的基础,也用于所有高级时序分析。

生成时钟的时序分析

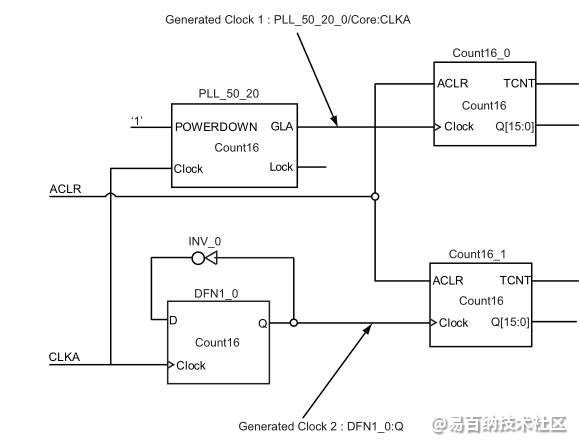

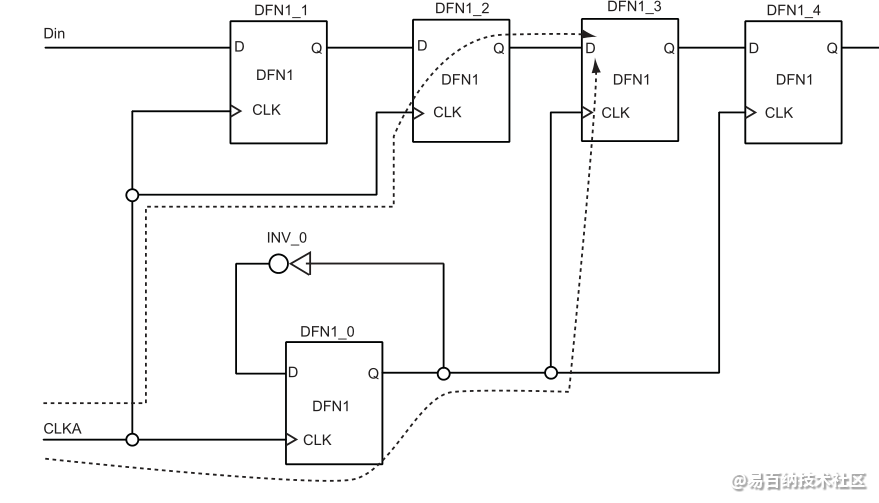

许多设计的时钟都是通过锁相环(PLL),时钟分频器或其他允许的方法在内部生成的。 SmartTime工具允许您为内部生成的时钟产生时钟约束,并验证其时序行为。您需要在主时钟上应用时钟约束。对于通过PLL生成的时钟,SmartTime为生成的时钟创建约束,并在时序分析期间自动应用约束。 对于通过时钟分频器生成的时钟,您需要手动应用生成的时钟约束。考虑如下图所示的设计示例。CLKA是主时钟,运行频率为50 MHz。 PLL_50_20_0 / Core:GLA和DFN1_0:Q是通过PLL和时钟分频器生成的。以下部分描述了这两个生成时钟的时序分析。

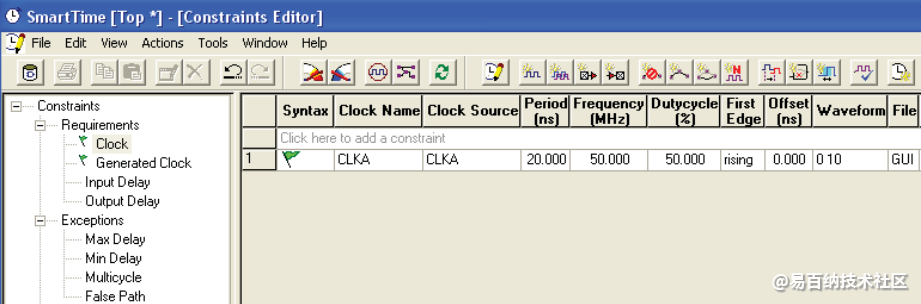

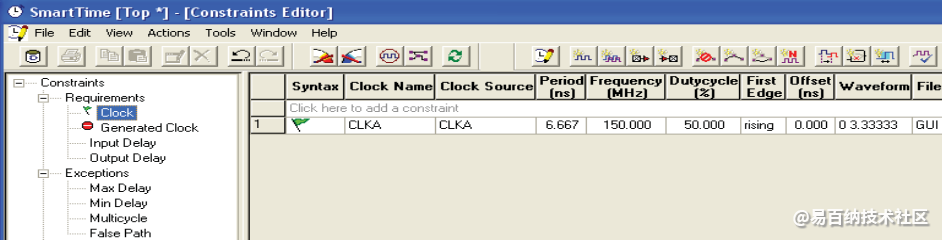

首先约束主时钟:

通过GUI界面进行约束,最终会生成如下的约束语句:

create_clock -name { CLKA } -period 20.000 -waveform { 0.000 10.000 } { CLKA }- 1

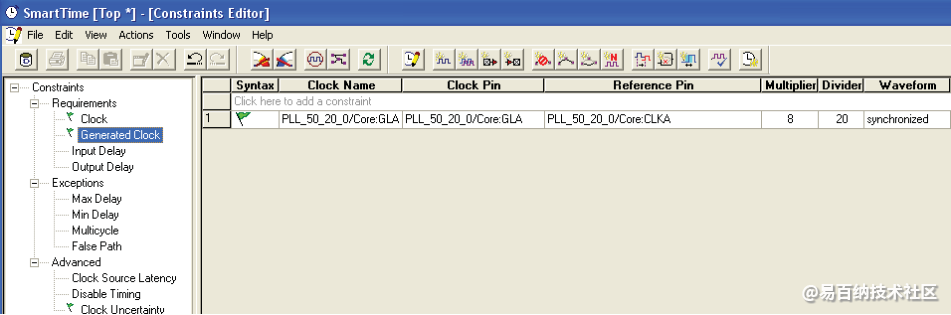

应用参考时钟约束后,SmartTime工具将自动为PLL生成生成的时钟约束。 SmartTime会读取具有PLL分频器设置的网表,然后自动填充分频器比率。但是,您仍然需要标识其他生成的时钟并应用生成的时钟约束。

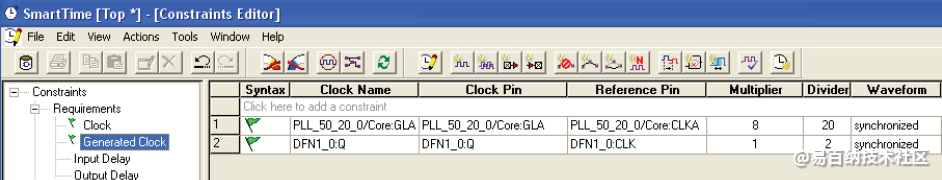

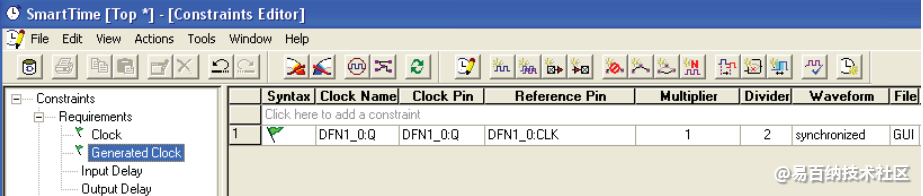

标识生成的时钟并应用生成的时钟约束。

上述约束对应的sdc约束语句为:

create_generated_clock -name {PLL_50_20_0/Core:GLA} -divide_by 20 -multiply_by 8 -

source/{PLL_50_20_0/Core:CLKA}{PLL_50_20_0/Core:GLA}

create_generated_clock -name{DFN1_0:Q}-divide_by 2 -source{DFN1_0:CLK}{DFN1_0:Q}- 1

- 2

- 3

- 4

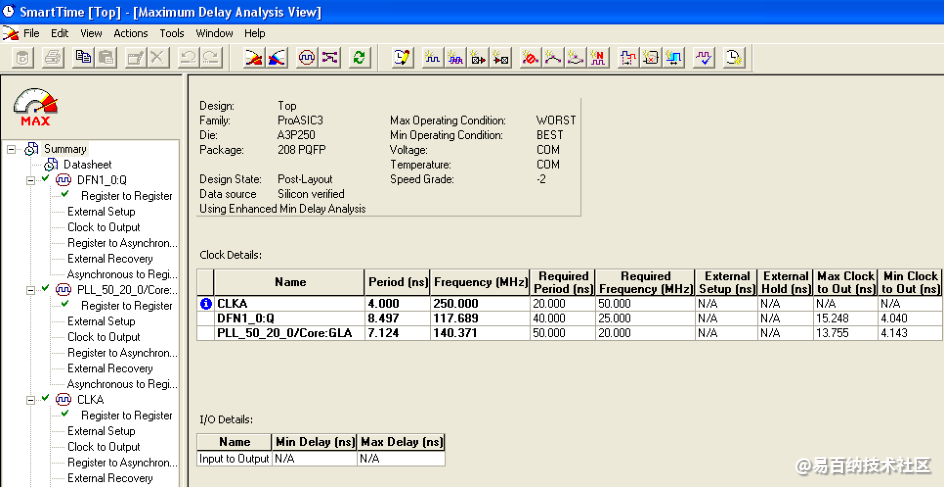

最大延迟分析视图显示参考时钟CLKA和两个生成的时钟PLL_50_20_0 / Core:GLA和DFN1_0:CLK的时序分析。

内部生成时钟的时序分析如下图所示。

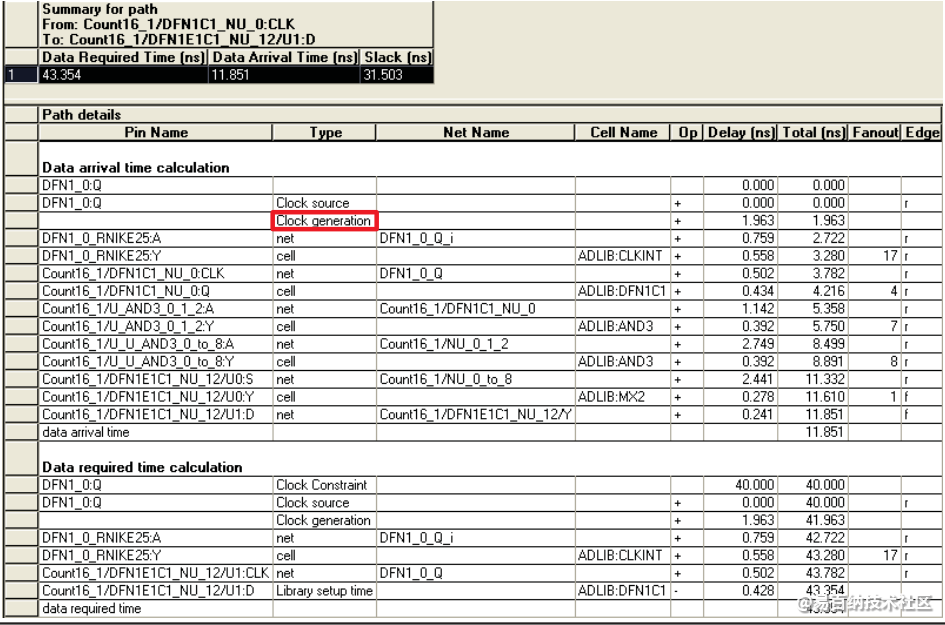

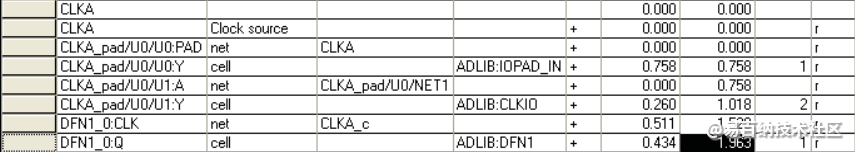

SmartTime自动计算时钟生成延迟。下图显示了从CLKA端口到时钟分频器输出引脚的延迟的计算。

具有两个异步时钟的Inter-Clock域分析(异步时钟的跨时钟域分析)

SmartTime可以对包含跨两个时钟域存在的功能路径的设计进行时钟域间时序检查(启动数据的寄存器和捕获数据的寄存器由两个异步时钟源提供时钟)。需要两个时钟的准确规范才能进行有效的时钟域间时序检查。

注意:默认的SmartTime设置不显示时钟域间分析。您需要更改设置以启用时钟间域分析。根据设计,某些时钟域间路径是有效的时序路径,而某些则是伪路径。设计者有责任确定这些路径并根据需要应用时序例外。

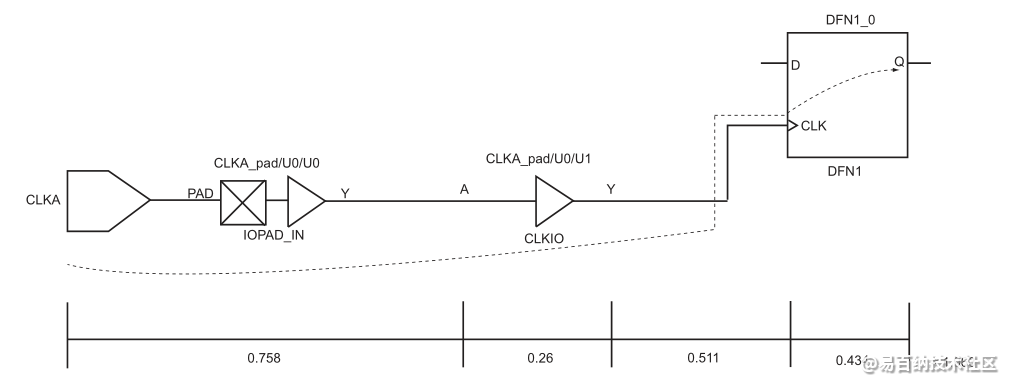

对于时钟域间路径,SmartTime将分析一个等于两个时钟周期中最小公倍数的公共周期内所有活动时钟沿之间的关系。对于建立时间检查,考虑了启动与捕获的最紧密关系,以确保数据在捕获边缘之前到达。

保持检查将验证建立关系不会被后续数据启动覆盖。用于建立和保持分析的时钟沿如下图所示。

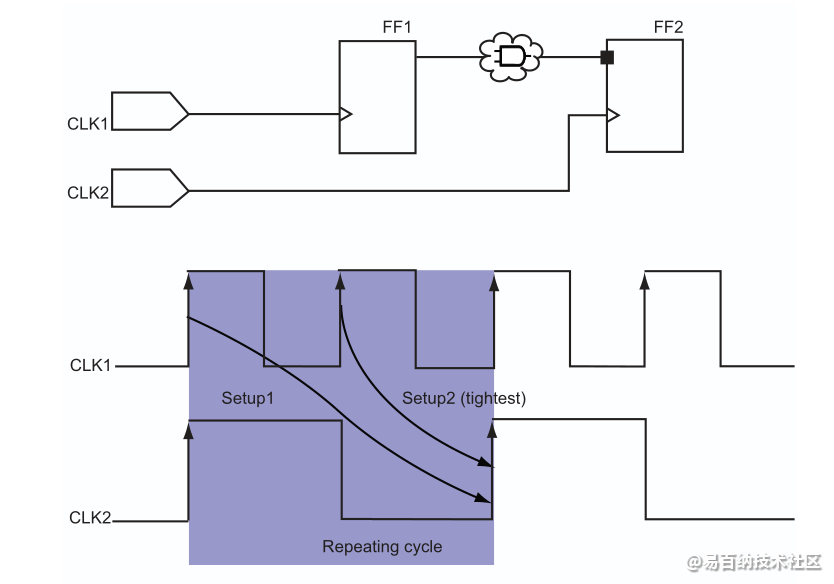

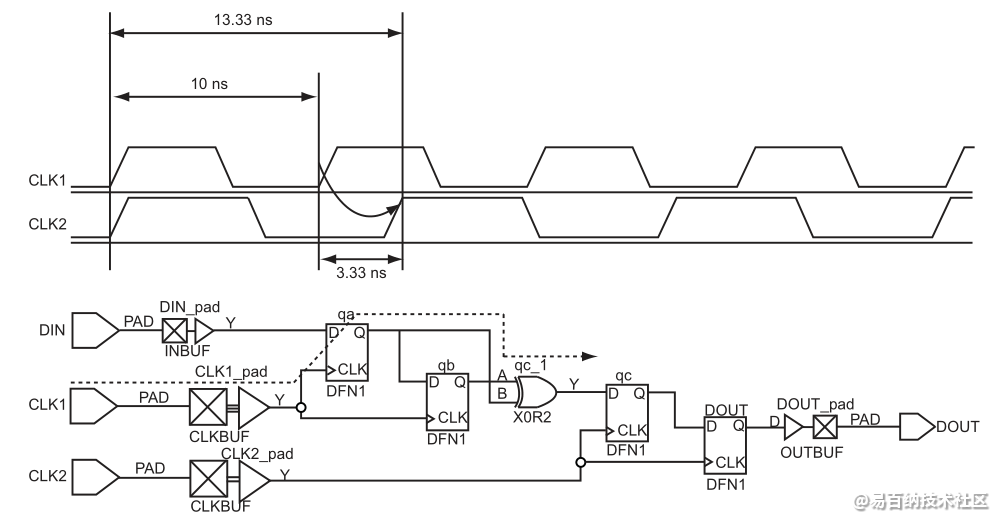

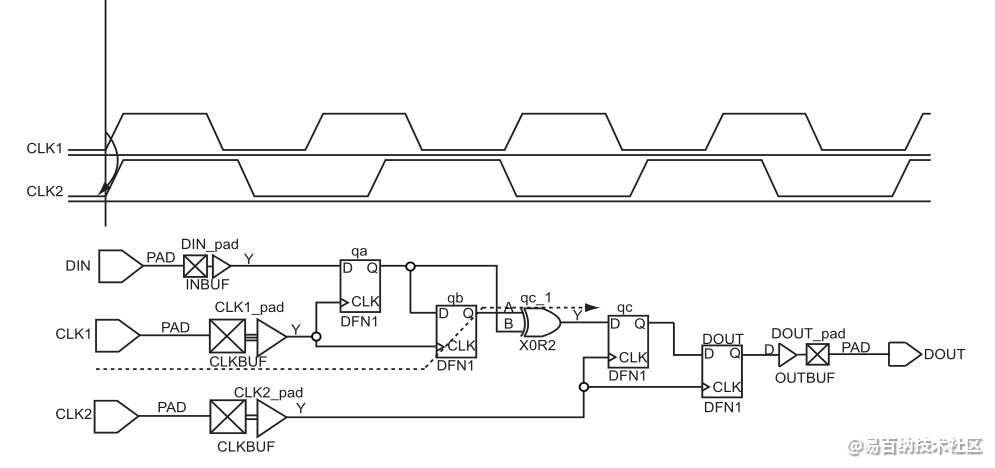

考虑下图中所示的域间设计示例。请注意,从CLK1域到CLK2域的路径是有效的时钟间域路径。假设CLK1为100 MHz,CLK2为75 MHz,并且两者均具有零偏移。

下面给出分析步骤:

使用SmartTime分析时钟间域时序

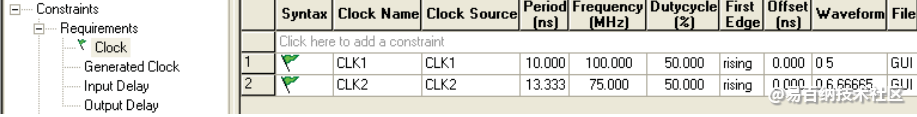

指定两个参考时钟的时钟频率和其他属性。有关使用GUI创建生成的时钟约束。

对应的sdc文件约束语句为:

create_clock -name{CLK1}-period 10.000-waveform{0.000 5.000}{CLK1}

create_clock -name{CLK2}-period 13.333-waveform{0.000 6.667}{CLK2}- 1

- 2

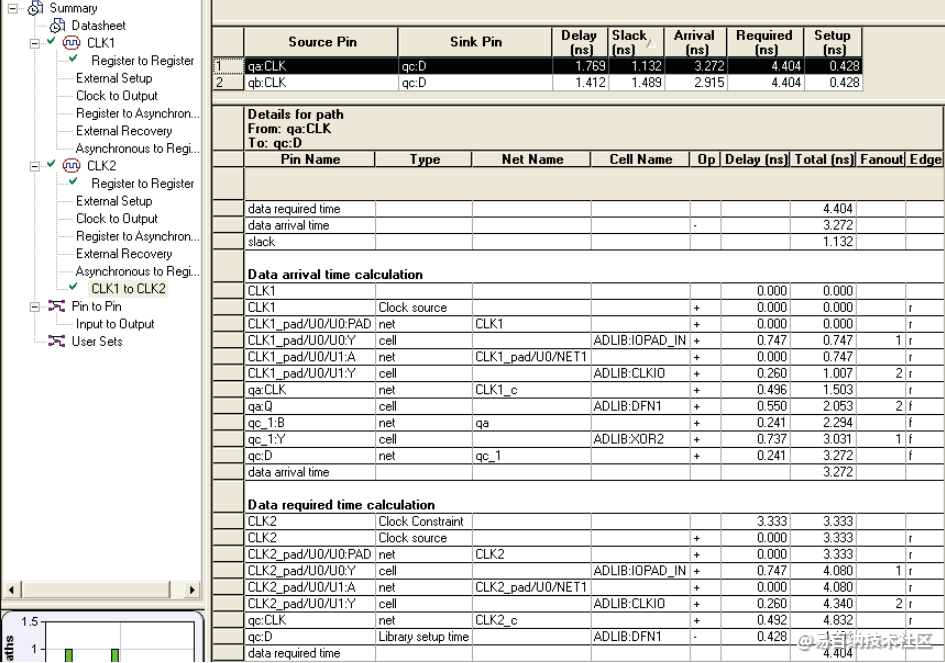

启用时钟域间分析。最大延迟分析视图显示在CLK2域分析下CLK1至CLK2的时序分析,如下图所示:

建立时间计算中使用的时钟沿和数据路径(最长的数据路径是从qa到qc寄存器)如下图所示。

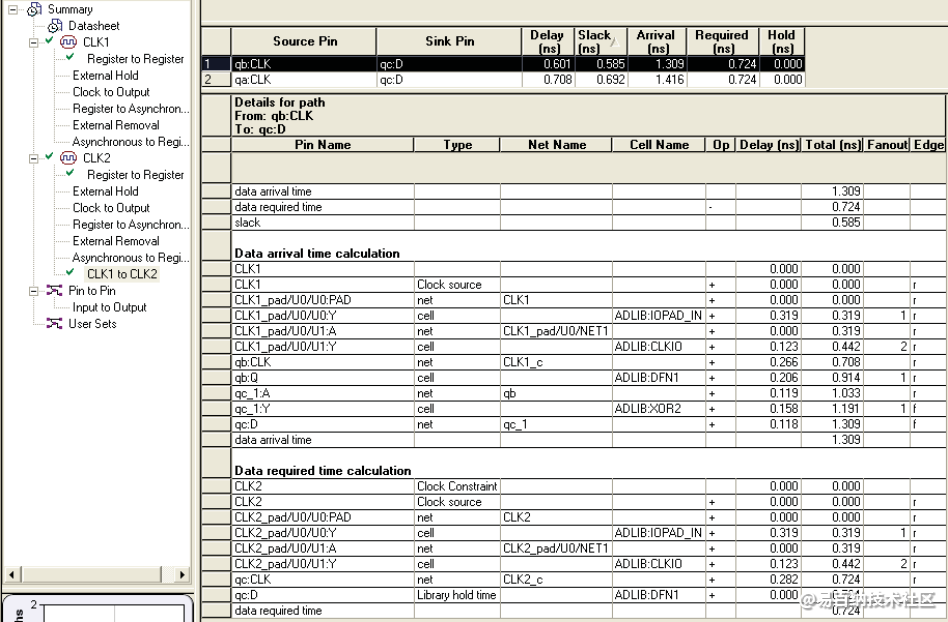

同样,最小延迟分析视图显示从CLK1到CLK2的保持分析。

从CLK1到CLK2域的保持检查如下图所示。

保持计算中使用的时钟沿和数据路径(最短的数据路径是从qb到qc寄存器)如下图所示:

生成时钟的跨时钟域分析

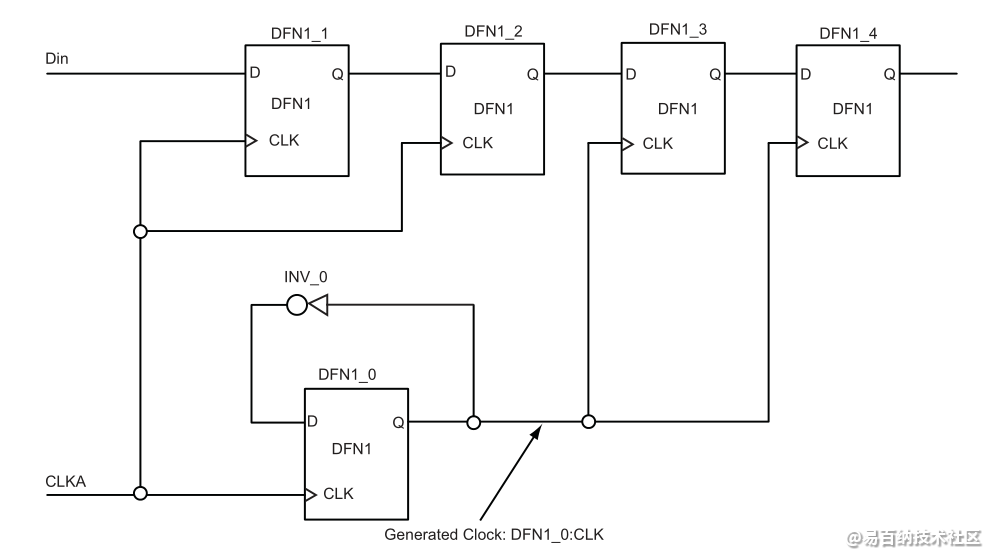

内部生成时钟的设计也可以具有跨时钟域路径。 SmartTime使您可以为内部生成的时钟指定生成的时钟约束,然后应用跨时钟域分析。如上一节所述,设计者有责任将路径标识为有效或false,并根据需要应用时序例外。考虑如下图所示的设计示例,其中CLKA是参考时钟,而DFN1_0:CLK是通过时钟分频器生成的。有一条路径可将数据从CLKA启动以捕获到DFN1_0:CLK域中。 “使用GUI的约束”部分显示了如何分析主时钟和内部生成的时钟之间的跨时钟域。

下面给出操作步骤:

指定参考时钟频率和其他属性。有关使用GUI创建生成的时钟约束。

对应的约束语句为:

create_clock -name{CLKA}-period 6.667 -waveform{0.000 3.333}{CLKA}- 1

确定生成的时钟,然后应用生成的时钟约束。

对应的约束语句为:

create_generated_clock -name{DFN1_0:Q}-divide_by2 -source{DFN1_0:CLK}

{DFN1_0:Q}- 1

- 2

启用时钟间域分析。

最大延迟分析视图显示DFN1_0:Q域分析下从CLKA到DFN1_0:Q的时序分析,如下图所示。SmartTime使用时钟之间的时钟沿自动计算时钟生成延迟和时钟约束。

总结

时序约束一般采用的语言都是tcl语言,约束格式为sdc格式,Xilinx的约束格式特殊点,ISE的约束为UCF文件,Vivado的约束文件为XDC,XDC与SDC基本等同,但无论什么格式,都可以使用GUI界面进行约束,不强求使用约束语句,重要的是懂得时序约束的原理, 或者说静态时序分析的方法。

这部分内容还不止这些,后面会继续介绍其他时序约束,例如多周期约束,抖动约束等。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:5981次2021-02-21 21:08:27

-

浏览量:10046次2021-02-20 22:37:06

-

浏览量:7187次2021-02-21 01:20:21

-

浏览量:9412次2021-02-20 17:50:13

-

浏览量:5223次2021-03-14 01:58:15

-

浏览量:6173次2021-03-22 01:26:53

-

浏览量:5601次2021-03-17 23:24:53

-

浏览量:5992次2021-02-14 01:58:16

-

浏览量:7977次2021-02-07 00:59:28

-

浏览量:5847次2021-04-27 00:06:35

-

浏览量:5065次2021-03-18 22:57:24

-

浏览量:4603次2021-06-20 20:10:03

-

浏览量:4208次2021-03-13 01:55:14

-

浏览量:4296次2021-03-12 23:39:20

-

浏览量:4750次2022-08-17 09:01:18

-

浏览量:5180次2021-05-23 23:50:14

-

浏览量:5457次2021-03-14 01:12:39

-

浏览量:4630次2021-04-27 00:05:09

-

浏览量:6805次2021-03-14 02:34:44

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友