FPGA的设计艺术(5)STA实战之时钟偏斜对建立保持时间的影响以及时序报告分析

STA回顾

70年代的时序是通过Spice仿真执行的。80年代的时序包括在Verilog仿真中,以确定设计是否足够快。两种方法都存在两个问题(动态时序):

1)分析仅与仿真一样–仅在仿真执行的情况下才发现问题

2)逻辑仿真慢5到10倍

静态时序更全面,通过计算设计中每个可能逻辑路径的延迟。最坏情况下的路径确定最大频率。

更多STA的基本问题,可以参考:

FPGA的设计艺术(4)STA实战之不同时序路径的建立保持时间计算

STA基本参数回顾

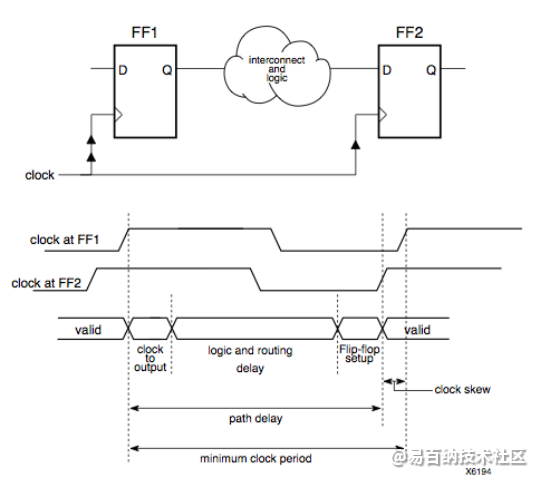

flop to flop

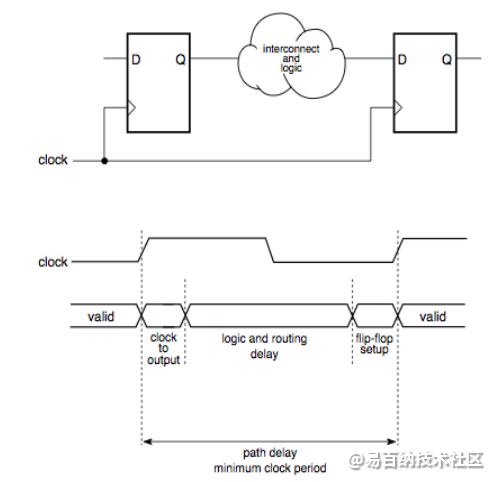

Setup Timing:Setup Timing的定义是在时钟有效沿到达之前数据需要保持稳定的时间。它的意义是检查信号是否及时到达。

如:

如果setup timing未能满足要求,则可以从以下方面处理:

- 1)降低时钟频率,

- 2)减少触发器之间的逻辑延迟

- 3)使用更快的触发器,即缩短上图中的时钟到数据输出延迟

关于setup timing的计算,链接:

FPGA的设计艺术(4)STA实战之不同时序路径的建立保持时间计算

已经给出了四种路径下的建立和保持时间要求计算。

下面为了内容的完整性,还是以不同的例子给出理解:

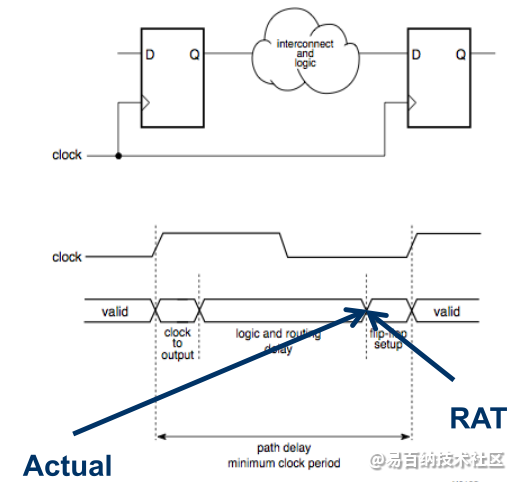

setup timing 要求是数据在捕获时钟沿之前应保持有效(稳定)的时间。计算所需的到达时间(RAT)和实际到达时间。

实际应在要求之前。你的裕量是多少。

上图中的裕量恰好为0.

RAT = T - Tsetup- 1

实际到达时间根据实际情况:

Tcq + Tcomb- 1

这里是理想模型,不考虑时钟偏斜,以及布线延迟,或者时钟偏斜为0,布线延迟在Tcomb中。

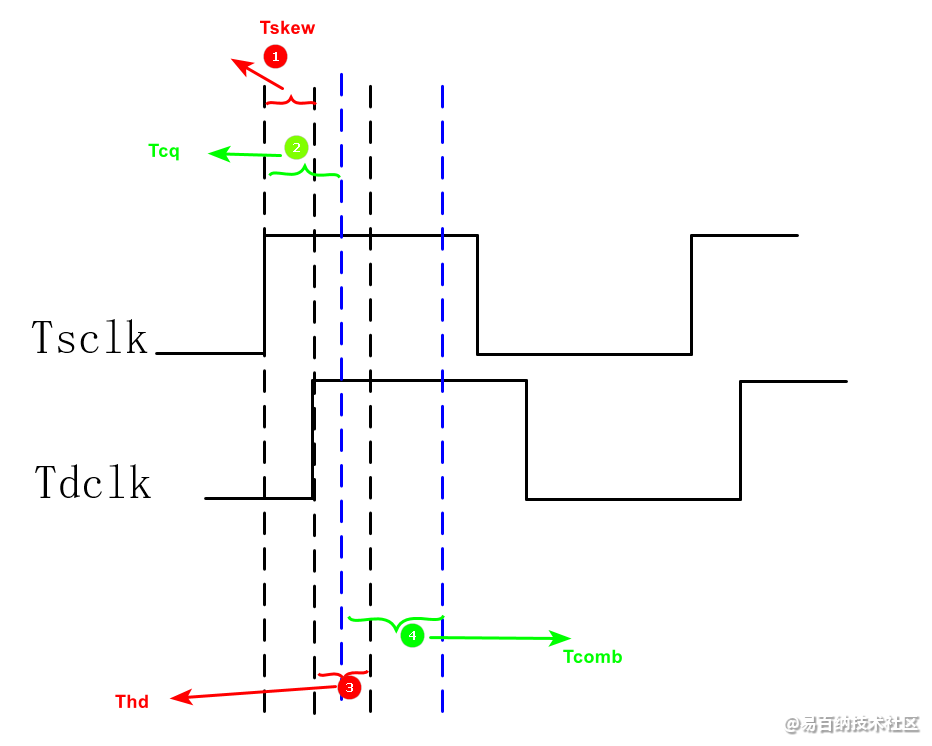

Hold Timing:Hold Timing的定义指的是在时钟有效沿之后,数据必须保持的最小时间。

保持时间要求是指数据应保持有效沿的时间后,计算所需的到达时间(RAT)和实际到达时间。实际应在要求之后。你的裕量是多少。

- 仅在时钟偏斜时发生。

- 与时钟周期或频率无关。

- 逻辑延迟通常只是启动触发器的启动延迟。

- 最坏的情况是触发器之间没有逻辑的移位寄存器。

1+3<2+4

数字代表编号- 1

- 2

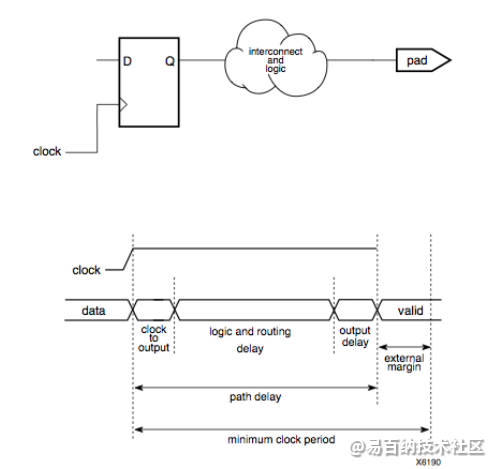

flop to output

寄存器到输出的建立时间要求类似于触发器到触发器,其意义都是检查信号是否及时到达时钟。

如上图,最小时钟周期为:

Tmin = Tcq + Tcomb + Toutdelay + Tsetup- 1

也就意味着,这些参数需满足:

Tclk > Tcq + Tcomb + Toutdelay + Tsetup- 1

如果不满足,即建立时序违规,可通过如下方式解决:

1)降低时钟频率,即增大时钟周期

2)减少逻辑延迟

3)减少外部建立时间要求

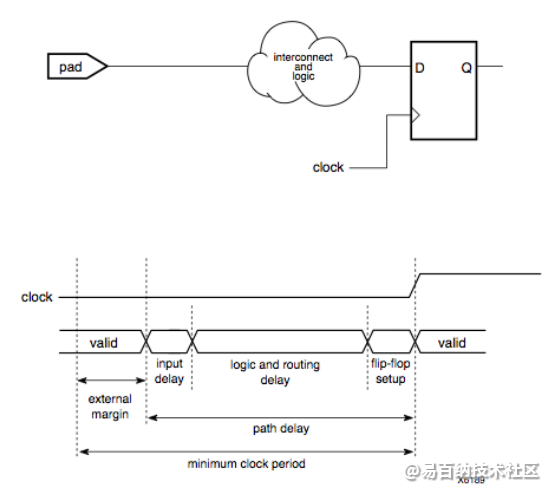

input to flop

其含义仍然是检查信号是否及时到达时钟。

不多解释,如果不满足建立时间,即external margin:

可以通过以下方法解决:

1)降低时钟频率

2)减少逻辑延迟

3)改善输入引脚上的到达时间

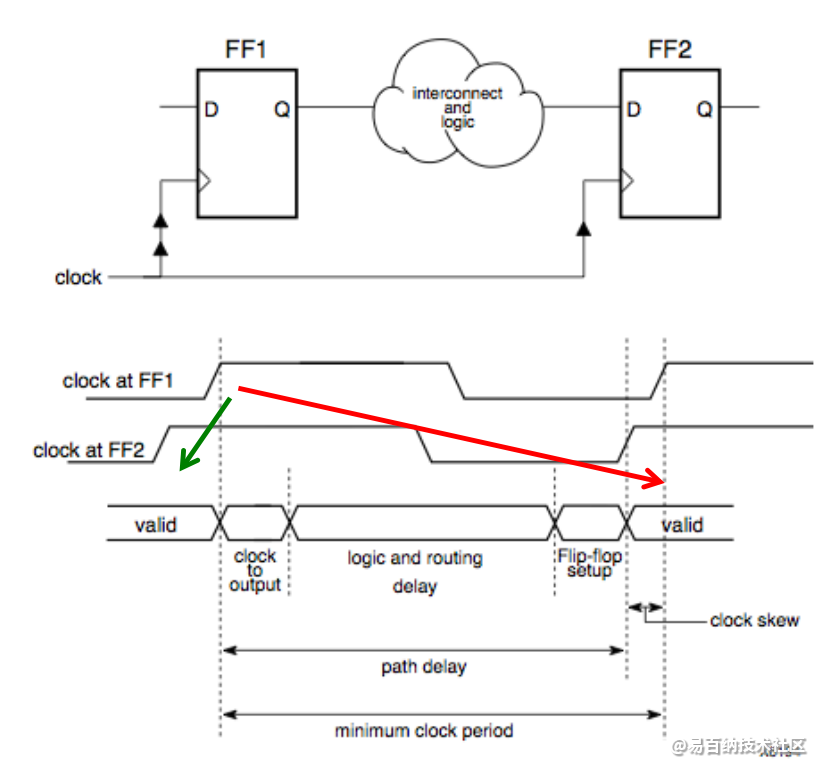

clock skew对setup以及hold timing的影响

时钟偏斜会伤害或帮助setup时间。

负时钟偏斜会减少整个工作周期,因此会损害建立时间,并且Xilinx的最大频率会忽略正偏,以进行建立时间计算。

如上,负时钟偏斜Tskew,注意Tskew是一个常数。

Tmin - Tskew = Tcq + Tcomb + Tsetup- 1

可以推论:

Tclk- Tskew > Tcq + Tcomb + Tsetup- 1

Tcq + Tcomb + Tsetup固定,Tskew越大,Tclk就要去越大。

如下图,实际分析下负时钟偏斜对建立的影响:

Bad for setups

Case 1 – Slow path

Launch = 1ns

Logic delay = 7ns slow

Setup = 1ns

Hold = 0ns (not used)

Skew = 2ns

Period = 10ns

Setup Slack = -1 nS

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

Good for holds

Case 2 – Fast path

Launch = 1ns

Logic delay = 0ns fast

Setup = 1ns (not used)

Skew = +3ns

Hold Slack = +4 nS - 1

- 2

- 3

- 4

- 5

- 6

- 7

上面的Launch可认为是Tcq。

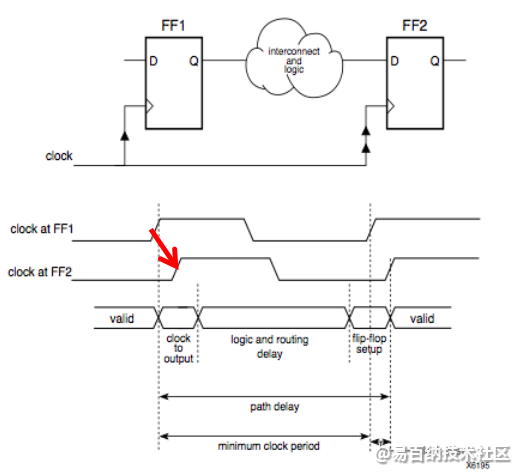

下面考虑对保持时间的影响:

保持时间的关系是:

Tcq + Tcomb > Thold + Tskew- 1

可见,保持时间裕量可以为:

Thold slack = Tcq + Tcomb - Tskew - Thold- 1

如果Tskew变大,则裕量越来越少。

- 由于正时钟偏斜,才有可能违反保持时间。

- 糟糕的问题是无法通过减慢时钟来固定预制芯片。(与时钟周期无关)

- 最糟糕的情况是具有低逻辑延迟的路径,例如移位寄存器。

在制造之前通过平衡时钟树或在逻辑中引入缓冲延迟来修复。

下面实际分析一个例子:

Good for setups:

Launch = 1ns

Logic = 9ns

Setup = 1ns

Skew = 2ns

Period = 10ns

Setup Slack = +1nS

- 1

- 2

- 3

- 4

- 5

- 6

- 7

Bad for holds:

Launch = 1ns

Logic = 1ns

Skew = 3ns

Hold Slack = -1 nS - 1

- 2

- 3

- 4

- 5

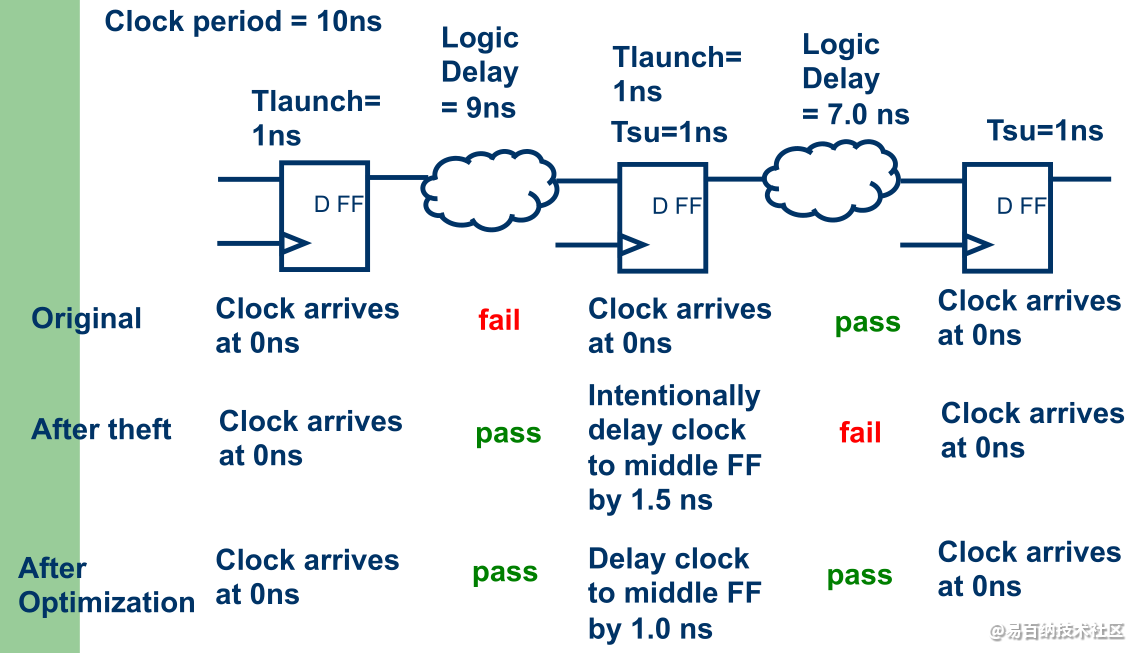

利用时钟偏斜解决时序违规

时钟偏斜理论上可以利用起来解决建立时间违规问题,如下:

保持时间同样调节,通过调节时钟偏斜,如何做呢?

插入时钟buffer。

-

时钟扇出–一个来源–数百万个触发器需要缓冲树以减少扇出和平衡

-

时钟延迟,从时钟引入到到达触发器之间的时间-对于与其他芯片同步很重要

-

时钟偏斜:任何两个触发器之间的时钟有效沿到达差异

-

时钟功耗:时钟速度快,负载最大的最活跃信号很容易消耗20-30%的功率

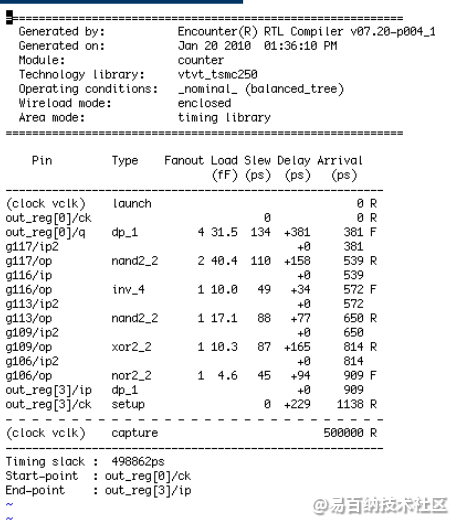

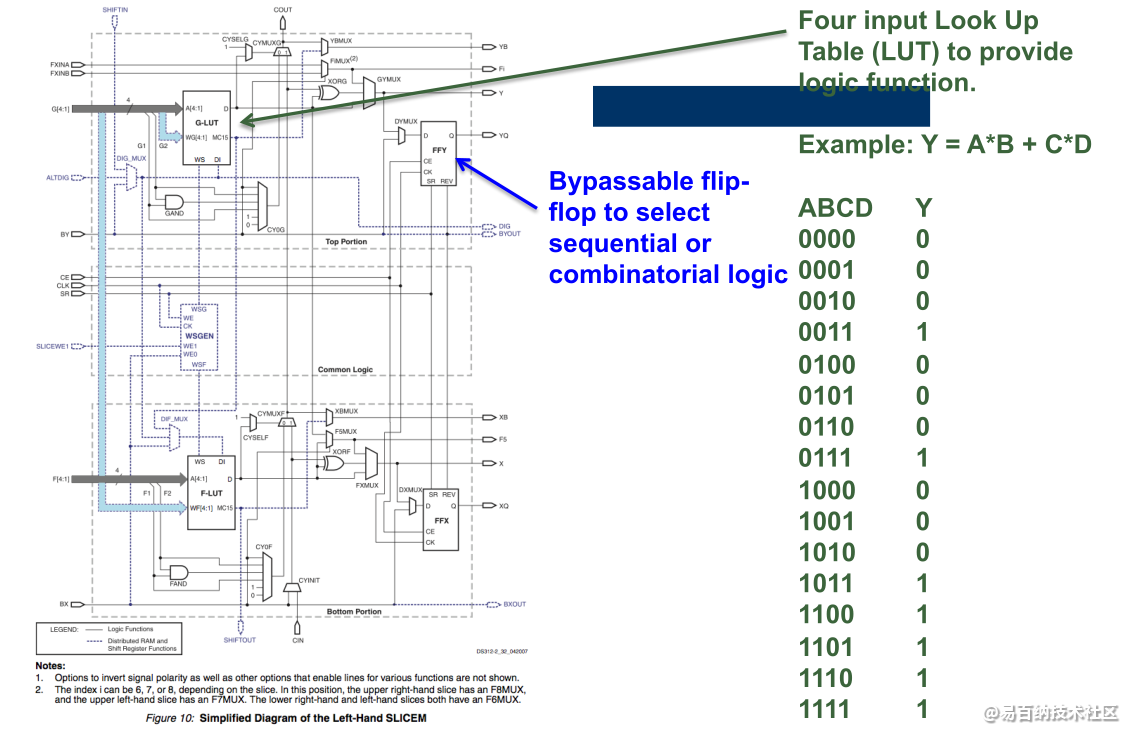

时序报告

给出Cadence的时序报告页面参考:

脚本(完整综合脚本的一部分):

define_clock –nam vclk -period 50 clk

external_delay –input 0 –clock vclk [find / -prot ports_in/*]

external_delay –output 0 –clock vclk [find / -prot ports_out/*]

report timing > timing.rpt - 1

- 2

- 3

- 4

生成报告。

报告列出了时序路径的延迟,最终存在时序裕量。

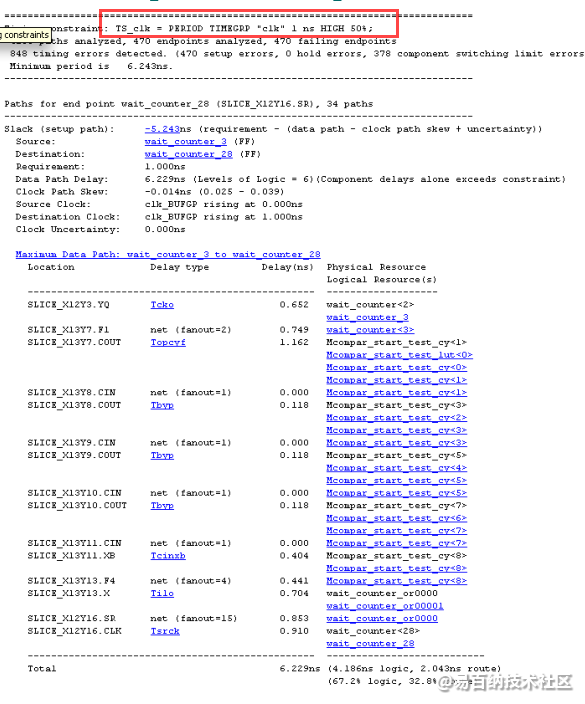

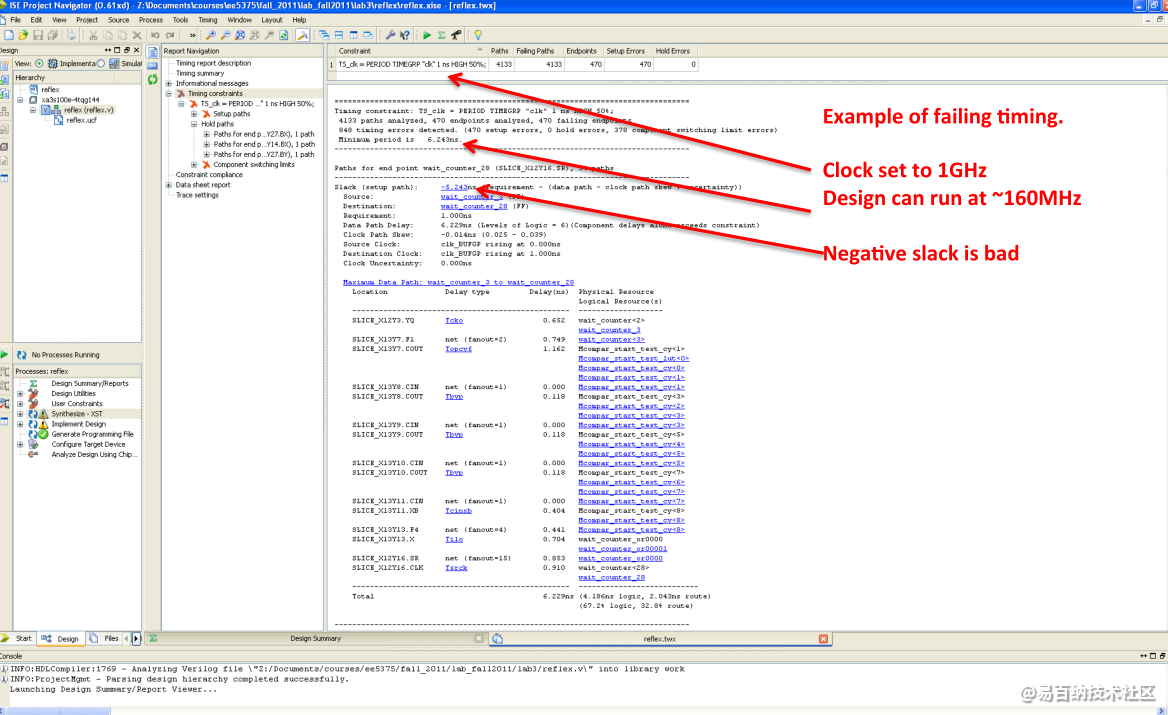

再看下图:

时序裕量就是负的,时序违规。

如上图,时钟给到了1GHz:

情况很极端,时序不过很正常。

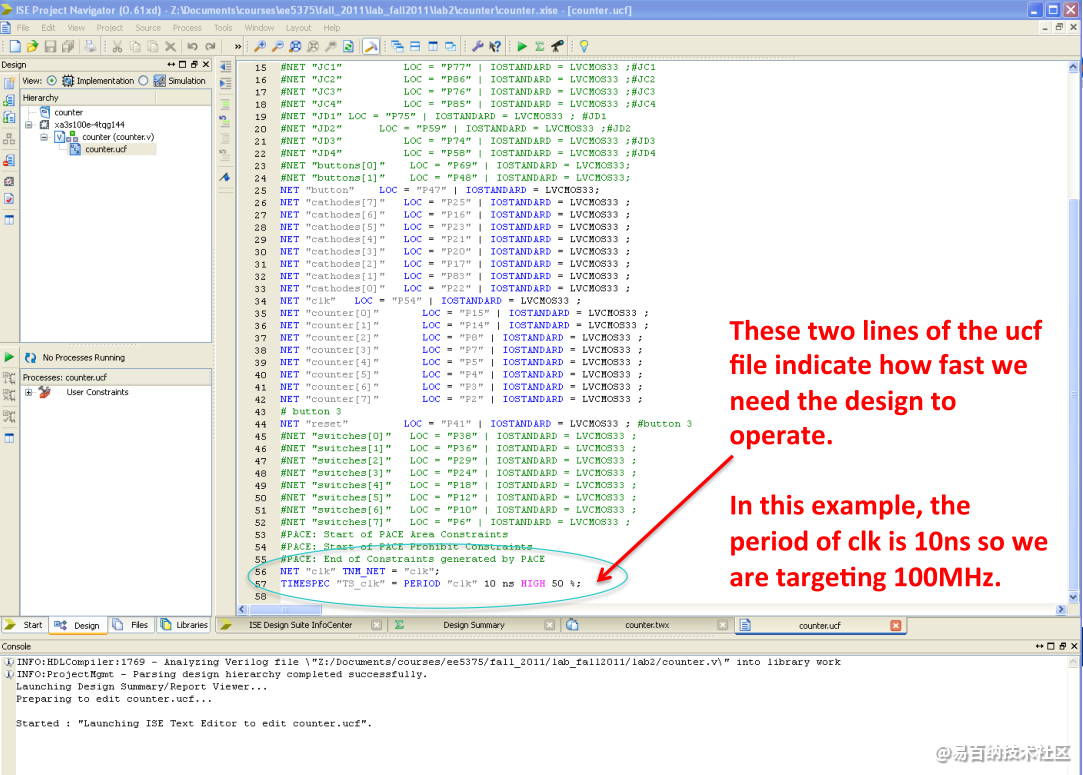

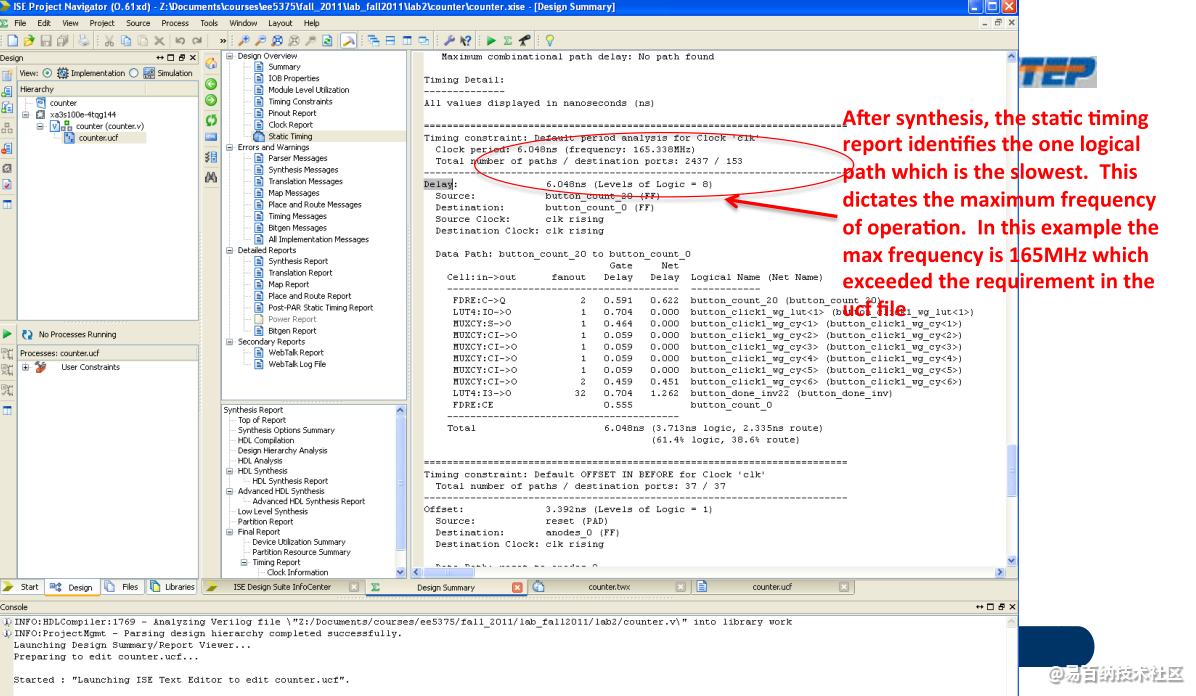

在参考Xilinx的SP6的时序报告:

SP6的时序约束使用的是UCF文件。

假如给一个如下功能的逻辑:

如下为UCF文件截图:

时序约束,周期约束为100MHz。

综合后,查看时序报告:

可见,裕量充足。

如果约束时钟周期为1GHz,则:

时序裕量不足,差很远。

最后想说的是,可以通过综合工具提供的时序分析报告来查看,哪条路径的时序不满足需求,之后通过各种方式来解决时序违规,或更改设计,减小延迟,或减小时钟频率,大致如此。

上面还说了,可以通过改进时钟偏斜,这都是工具的事情,人工不用插手。还说了,使用更快的触发器,这个选定了器件,速率就定了,一般也不用插手。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:10042次2021-02-20 22:37:06

-

浏览量:6286次2021-02-21 16:01:28

-

浏览量:5978次2021-02-21 21:08:27

-

浏览量:9407次2021-02-20 17:50:13

-

浏览量:5222次2021-03-14 01:58:15

-

浏览量:6170次2021-03-22 01:26:53

-

浏览量:13470次2021-01-01 02:53:29

-

浏览量:7974次2021-02-07 00:59:28

-

浏览量:6508次2021-03-22 00:49:53

-

浏览量:5990次2021-02-14 01:58:16

-

浏览量:5846次2021-04-27 00:06:35

-

浏览量:11116次2021-03-20 13:22:58

-

浏览量:4294次2021-03-12 23:39:20

-

浏览量:1370次2023-04-11 15:24:20

-

浏览量:4206次2021-03-13 01:55:14

-

浏览量:4603次2021-06-20 20:10:03

-

浏览量:5179次2021-05-23 23:50:14

-

浏览量:4630次2021-04-27 00:05:09

-

浏览量:6802次2021-03-14 02:34:44

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友