FPGA的设计艺术(2)FPGA开发流程

前言

本文介绍整个FPGA设计流程以及设计FPGA所需的各个步骤-从一开始到可以将设计下载到FPGA的阶段。但是在此之前,让我们首先非常快速地介绍FPGA技术。

现场可编程门阵列(FPGA)是一种半导体器件,包含逻辑块,这些逻辑块被编程为执行一组特定的功能。这些可编程逻辑块在互连矩阵的帮助下相互连接。这些互连负责连接逻辑块并促进信号在芯片上的流动。该结构以二维阵列的形式排列,该二维阵列由将其与输入和输出信号连接的逻辑块,互连和I / O块组成。逻辑块本身由查找表或LUT,触发器或FF和多路复用器组成。

使用FPGA的主要好处之一是它们是可重新编程的,这意味着可以对其进行修改,以使其功能完全不同于在设计人员每次将新代码上传到FPGA之前所执行的功能。

FPGA开发工具

不同厂家有不同的开发工具,当今世界,最有名气的FPGA厂家Altera和Xilinx都有自己的开发工具,例如,Altera的Quartues II,Xilinx的早期版本ISE(6系列以及6之前系列的FPGA)以及后来的开发工具Vivado(7系列以及7系列之后的FPGA)。现在的FPGA朝着异构的方向发展,所谓异构,也就是FPGA中嵌入许多其他的嵌入式设备,例如arm等,FPGA 的架构也发生了变化,工具也跟着更新换代,例如Xilinx工具推出的Vivado HLS,以后后面针对人工智能的Vitis。

不同的开发工具,针对自家FPGA的开发流程大同小异,本质都是一致的,差异在于编译(这里的编译指的是综合实现等过程)的过程中生成的文件不同,例如ISE在

综合过程中生成NGR和NGC网表文件,其实现(implementation)过程又可细分为翻译(主要完成统一标准工作,将各种网表文件(EDN、NGC、NMC)及约束文件翻译成Xilinx 标准的NGD文件格式,全部由各种NGD原语构成。)映射以及布局布线过程,在这些过程中生成文件多样,例如NCD,NGD等。而升级之后的Vivado工具将翻译,映射以及布局布线合并为实现,统一生成不同阶段的dcp文件。下面具体介绍。

FPGA开发流程

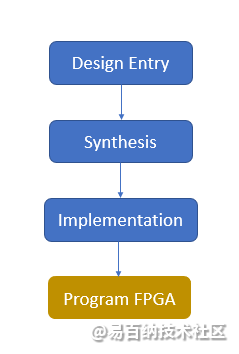

FPGA设计流程包括几个不同的步骤或阶段,包括设计输入,综合,实现和器件编程。 我们将简单探讨每个阶段。

设计输入

可以使用各种技术(例如,原理图),通过硬件描述语言或HDL进行设计输入,或者甚至可以结合使用两种方法,并使用可以将HDL转换为原理图的工具,反之亦然,这取决于您的FPGA,两者兼而有之。设计和偏好。通常,对于涉及更多复杂系统的设计,最好选择HDL,这是一种更快的基于语言的过程,使您无需在较低级别的硬件上进行设计,而示意图则是希望的人的理想选择。设计硬件,因为它为整个系统提供了更多可见性。

每种方法都有其优点和缺点。尽管基于原理图的技术更易于阅读和理解,但它往往仅适用于相对较小的项目。另一方面,基于HDL的方法往往快速且易于实现,并且今天是FPGA设计中最受欢迎的设计入口。

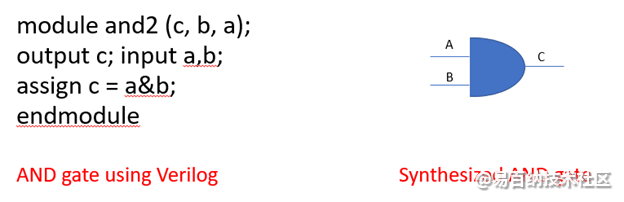

综合

在以代码形式输入设计之后,此阶段将其转换为包含诸如门,触发器和乘法器等元素的实际电路。 输入的HDL实际上已转换为网表,该网表列出了项目所需的逻辑元素以及特定层次结构中所需的互连。

一旦输入基于HDL的设计,该过程便从语法检查开始。 然后,通过减少逻辑,消除冗余逻辑以及减小设计尺寸来优化它,同时又使它更快地实现。 最后一步是通过将设计连接到逻辑,估计相关时间,并制定出随后保存的设计网表,来确定技术。

FPGA合成由专用的综合工具执行。 Cadence,Synopsys和Mentor Graphics是EDA公司,致力于开发,销售和销售FPGA综合工具。

各大FPGA厂家都有专用的FPGA综合工具,例如上面提到的Vivado,ISE等。

实现

在此阶段中,将确定设计的布局,该阶段包括三个步骤:翻译,映射以及布局和布线。该步骤由FPGA供应商提供,因为他们最了解如何将综合网表转换为FPGA。

该工具的第一步是收集用户与网表文件一起设置的所有约束。这些限制可能涉及引脚的分配和位置,有关时序的要求(例如最大延迟或时钟的输入周期)。

然后,该工具通过将文件中指定的资源需求与所使用的FPGA上实际可用的资源进行比较,来制定实现方案。该电路被分为逻辑块或子块形式的元件。结果,您的整个设计被放置在特定的逻辑模块中,并被“映射”到FPGA中。

下一步是根据用户设置的约束在所有逻辑块和IO块之间连接所有信号。

设备编程

该过程的最后一步是最终将映射出并完全布线的设计加载到FPGA中。 因此,您将需要生成一个BitSteam文件。

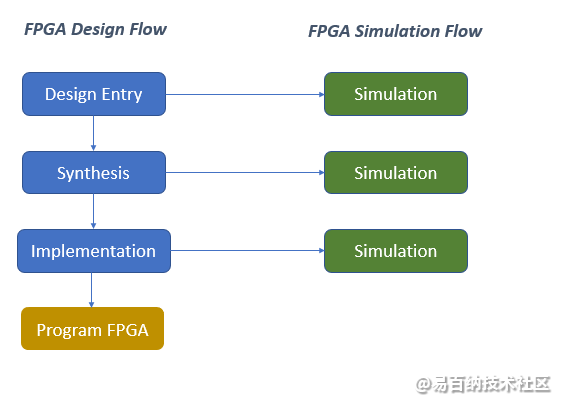

FPGA验证与仿真

这个过程穿插在FPGA的开发流程中,例如设计输入之后可以进行行为仿真,又叫功能仿真,在综合实现过程中可进行静态时序分析,其实在综合后,实现后都可以进行功能仿真,这里的功能仿真是加入了真实延迟之后的仿真,更符合实际情况。在实际操作工程中,一般只进行行为仿真以及静态时序分析,即可保证设计的功能与质量。

下面细说:

不用说,验证实现的设计是否执行了所需的功能是FPGA设计流程的重要组成部分。

行为仿真(在设计入口)

行为仿真(也称为RTL仿真)在综合之前执行。 这种快速仿真可用于无限制地检查设计的功能。 经常使用此仿真来测试您的代码并查找逻辑错误。

功能仿真(综合后)

综合过程完成后,可以使用功能仿真来验证设计的功能。 它是网表级别的仿真,忽略了与时序相关的问题。

时序仿真(实现时)

此仿真将为您提供最准确的设计行为图。 它考虑了目标FPGA芯片以及所有逻辑块的功能,布线,延迟等等。 时序仿真需要更长的时间,并且比以前的仿真提供更多的细节。

静态时序分析

运行实现设计过程后,您可以使用时序分析工具对FPGA设计进行详细分析。这样可以确保将指定的时序约束正确传递给实现工具。执行详细的分析包括以下内容:

- 验证是否满足设计中所有路径的时序要求。

- 分析设计中所有约束路径的建立和保持性能。

- 确认工作频率在组件性能约束之内。

- 分析不受约束的路径,以确定是否有任何关键时序路径不受约束。

为了有效地分析时序,建议采用自上而下的方法,首先检查设计的整体性能,然后检查不同类别的约束,单个约束,最后检查设计中的特定路径。 分析完成后,将创建该分析的详细报告,可以对其进行自定义以仅包含您需要的信息。您可以使用时序分析器对FPGA设计进行详细的分析,如下所示:

- 分析输入时序

- 分析同步元素时序

- 分析输出时序

- 分析时序异常

- 分析不受约束的路径等等。

这篇文章就到这里,我们下篇文章继续详细了解下什么是静态时序分析。

- 分享

- 举报

-

浏览量:4202次2021-03-13 01:55:14

-

浏览量:4290次2021-03-12 23:39:20

-

浏览量:7956次2021-02-07 00:59:28

-

浏览量:5218次2021-03-14 01:58:15

-

浏览量:4599次2021-06-20 20:10:03

-

浏览量:5845次2021-04-27 00:06:35

-

浏览量:5177次2021-05-23 23:50:14

-

浏览量:9398次2021-02-20 17:50:13

-

浏览量:5447次2021-03-14 01:12:39

-

浏览量:12028次2021-05-23 01:13:25

-

浏览量:4626次2021-04-27 00:05:09

-

浏览量:10605次2020-12-13 19:59:59

-

浏览量:6796次2021-03-14 02:34:44

-

浏览量:4715次2021-05-17 23:44:33

-

浏览量:7136次2021-03-15 23:18:36

-

浏览量:9290次2021-03-21 22:58:26

-

浏览量:7636次2021-04-10 01:44:48

-

浏览量:6504次2021-03-22 00:49:53

-

浏览量:6161次2021-03-22 01:26:53

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友

开工大吉~