FPGA逻辑设计回顾(10)DDR/DDR2/DDR3中的时序参数的含义

前言

上篇文章:FPGA逻辑设计回顾(9)DDR的前世今生以及演变过程中的技术差异有提到,制造商会以一系列由破折号隔开的数字来宣布存储时序(例如5-5-5-5、7-10-10-10等)。 CAS延迟始终是这些序列中的第一个数字。

那其他的数字呢?这篇文章会讲这些数字代表的含义讲解清楚。

内存参数标识含义

DDR、DDR2和DDR3内存是根据其工作的最高速度和时序来分类的,时序是3-4-4-8、5-5-5-15、7-7-7-21或9-9-9-24等数字,越低越好。下面解释这些数字的含义。

DDR、DDR2和DDR3内存遵循DDRxxx/PCyyyy分类。

第一个数字xxx表示该内存芯片支持的最高时钟速度。例如,DDR400内存的最高工作频率为400MHz,DDR2-800的最高工作频率为800MHz,DDR3-1333的最高工作频率为1,333MHz。需要注意的是,这并不是内存的真实时钟速度。DDR、DDR2和DDR3内存的实际时钟是标注时钟速度的一半。因此DDR400内存的工作频率为200MHz,DDR2-800内存的工作频率为400MHz,DDR3-1333内存的工作频率为666MHz。

第二个数字表示该内存达到的最大传输速率,单位为MB/s。DDR400内存传输数据的速度最高为3,200MB/s,因此被标记为PC3200。DDR2-800内存传输数据的速度为6400MB/s,他们被标注为PC2-6400。而DDR3-1333内存可以以10664MB/s的速度传输数据,它们被标注为PC3-10600或PC3-10666。正如你所看到的,我们在 "DDR "或 "PC "后面用数字 "2 "或 "3 "来表示我们说的是DDR2或DDR3内存,而不是DDR。

第一个分类,DDRxxx,是用来划分内存芯片的标准,而第二个分类,PCyyyy,是用来划分内存模块的标准。

这在上一篇文章中也说了:

从理论上讲,该命名系统DDRx-yyyy(其中x是技术世代,yyyy是DDR时钟速率)仅用于存储芯片。内存模块(用于焊接内存芯片的小印刷电路板)使用不同的命名系统:PCx-zzzz,其中x是技术代号,zzzz是最大理论传输速率(又称最大带宽)。

下图中,可以看到一个PC3-10666内存模块,它使用的是DDR3-1333内存芯片。注意时序(7-7-7-18)和电压(1.5V)。

存储器模块的最大传输速率可以通过以下公式计算。

- 最大理论传输率 = 时钟 x 位数 / 8

由于DIMM模块一次传输64位,所以 "位数 "将是64位。由于64 / 8 = 8,我们可以将这个公式简化为。

- 最大理论传输率 = 时钟 x 8 ...

如果将内存模块安装在内存总线以较低的时钟速率运行的系统上,内存模块实现的最大传输速率将低于其理论上的最大传输速率。实际上,这是一个非常常见的误判。

比如说,你买了一对DDR3-2133/PC3-17000内存。尽管它们被标注为DDR3-2133,但它们不会在你的系统上以2133MHz的速度自动运行。这是它们支持的最大时钟速率,而不是它们运行的时钟速率。如果你将它安装在支持DDR3内存的普通PC系统上,它们可能会以1,333 MHz(DDR3-1333)的速度运行--这是DDR3的最高标准速度--实现10,664 MB/s的最大传输速率。所以,它们不会自动运行在2,133 MHz,也不会自动达到17,000 MB/传输速率。

那么,为什么有人会买这些模块?有人会买他们的超频。由于制造商保证这些模块将运行到2,133兆赫,你知道你可以提高内存总线时钟到1,066兆赫,以实现更高的性能与您的系统,但是,你的主板必须支持这种超频。因此,如果您不打算对系统进行超频,那么购买标示时钟频率高于系统支持的内存模块是没有用的。

对于普通用户来说,这就是你需要知道的关于DDR、DDR2和DDR3内存的一切。对于高级用户来说,还有另一个特点:内存的时序或延迟。

内存时序参数含义

由于时序的原因,两个理论上最大传输速率相同的内存模块可以达到不同的性能水平。为什么在两者以相同的时钟速率运行的情况下会出现这种情况?

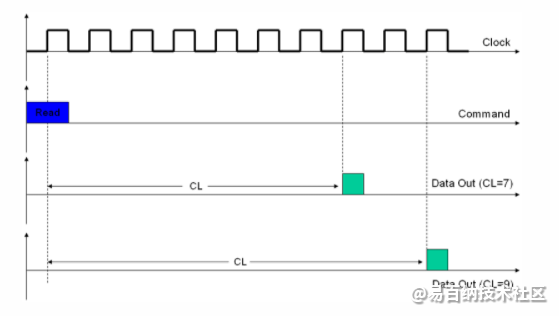

时序衡量的是内存芯片在内部做某事的延迟时间。下面是一个例子。考虑到最著名的参数,它被称为CAS Latency(或CL或 "访问时间",“列选通延迟”),它告诉我们内存模块在返回CPU请求的数据时将延迟多少个时钟周期。一个CL为9的内存模块将延迟9个时钟周期来提供请求的数据,而一个CL为7的内存模块将延迟7个时钟周期来提供数据。虽然这两个模块可能以相同的时钟速率运行,但第二个模块的速度会更快,因为它将比第一个模块更快地交付数据.这个问题被称为 "延迟"。正如你在下图中看到的,那里的模块的CL为7。

内存时序是通过一系列数字给出的,例如,4-4-4-8,5-5-5-15,7-7-7-21或9-9-9-24。这些数字表示内存执行某项操作所需的时钟周期数。数字越小,内存的速度越快。上图描绘的内存模块的时序为7-7-7-18,下图中描绘的内存模块的时序为8-8-8-24。

这些数字所表示的操作如下。CL -tRCD -tRP -tRAS -CMD。要理解它们,请记住,存储器的内部组织是一个矩阵,数据存储在行和列的交点处。

CAS延迟(CL)

CAS Latency(CL)是最著名的内存参数,它告诉我们内存将延迟多少个时钟周期来传送所请求的数据,一个CL=7的内存将延迟7个时钟周期来传送数据,而CL=9的内存将延迟9个时钟周期来执行同样的操作。因此,对于以相同时钟速率运行的两个内存模块来说,CL值最低的那个模块会更快。

请注意,这里的时钟速率是内存模块运行时的实际时钟速率,即额定时钟速率的一半。由于DDR、DDR2和DDR3内存在每个时钟周期内可以提供两个数据,因此它们的额定时钟速率是实际时钟速率的两倍。

下图中,可以看到CL的工作原理。我们举了两个例子,一个是CL=7的内存模块,一个是CL=9的内存模块。蓝色的命令将是一个 "读 "的命令。

考虑到两者在相同的时钟速率下运行,CL=7的内存将比CL=9的内存延迟提高22.2%。

你甚至可以计算出内存延迟到开始传输数据的时间,每个时钟周期的周期可以通过公式轻松计算出来。

T = 1 / f

因此,DDR3-1333内存在1333 MHz(666.66 MHz时钟)下运行的每个时钟周期的周期为1.5 ns(ns=纳秒;1 ns=0.000000001 s)。所以,这个DDR3-1333内存如果CL=7的话,会延迟10.5 ns开始传输数据,如果CL=9的话,则延迟13.5 ns。

RAS到CAS延迟(tRCD)

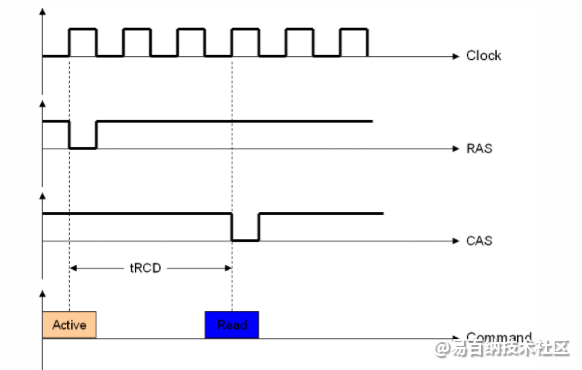

每个存储芯片内部都是以矩阵的形式组织的。在每一行和每一列的交叉点,我们有一个小电容,负责存储 "0 "或 "1"--数据。在存储器内部,访问存储数据的过程是通过先激活行,再激活列来完成的。这种激活是通过两个控制信号来完成的,这两个信号被称为RAS(Row AddressStrobe)和CAS(Column Address Strobe)。这两个信号之间的时间间隔越短越好,因为数据会被更快地读取。RAS到CAS延迟或tRCD测量这个时间。如下图,我们说明了这一点,显示了一个内存,RCD=3。

正如您所看到的,RAS到CAS延迟也是 "活动 "命令和 "读 "或 "写 "命令之间的时钟周期数。

与CAS Latency一样,RAS到CAS Delay的工作原理是内存实际时钟(是标记时钟的一半)。该参数越低,内存速度越快,因为它将更早地开始读取或写入数据。

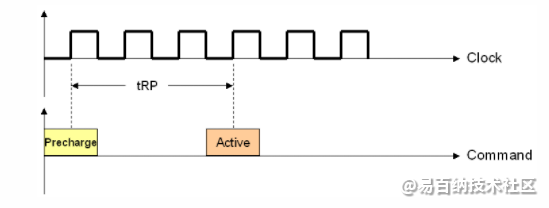

RAS预充电(tRP)

从内存中取出数据后,需要发出一条名为Precharge的命令,关闭正在使用的内存行,允许新的行被激活。RAS预充电时间(tRP)是指从Precharge命令到下一个Active命令可以发出的时间。正如之前所了解到的,Active命令启动了一个读或写周期。

上图中,我们以tRP=3的存储器为例。

与其他参数一样,RAS预充电与内存实际时钟(是标注时钟的一半)一起工作。这个参数越低,内存的速度就越快,因为它会更早地发出Active命令。

加上我们所看到的一切,从发出Precharge命令到实际得到数据之间的时间将是tRP + tRCD + CL。

其他参数

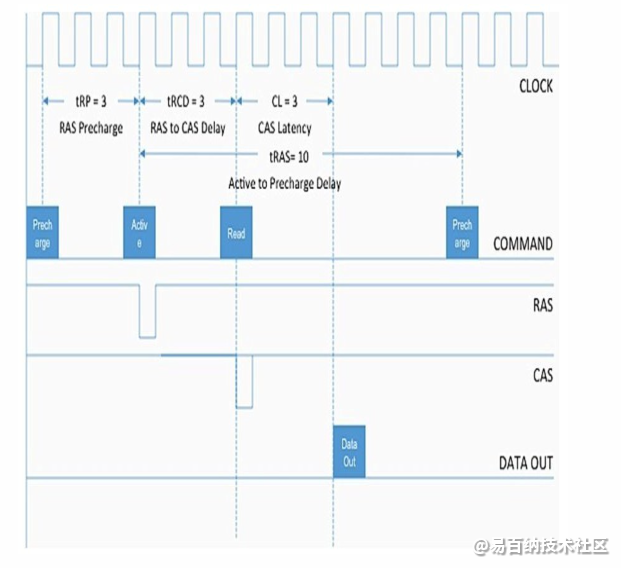

我们再来看看另外两个参数,Active to Precharge Delay(tRAS)和Command Rate(CMD)。与其他参数一样,这两个参数与内存实际时钟(即内存标示时钟的一半)有关。这些参数越低,内存的速度就越快。

Active到预充电延迟(tRAS)。发出一条Active命令后,在tRAS过后才能发出另一条Precharge命令。所以,这个参数限制了内存何时可以开始读取(或写入)不同的行。

命令速率(CMD)。它是指内存芯片从被激活(通过CS-芯片选择-引脚)到可以向内存发出任何命令所需的时间。该参数带有字母 "T"。可能的值是1T或2T,分别表示一个时钟周期或两个时钟周期。

为了更好地理解,下图为时序参数为3-3-3-10(假设)的存储器的时序图。

在文章的最后,我们可以将时序参数总结如下。

-

CAS延迟(CL)是指在正确的行已经打开的情况下,从DRAM中读取第一个内存位所需的时间。

-

在没有任何活动行的情况下,从DDR中读取第一个内存位的时间为tRCD+CL。

-

从一个没有活动行的DRAM中读取第一个内存位的时间是tRP + tRCD + CL。

-

从发出 "活动 "命令到发出 "预充电 "命令所需的时钟周期数为tRAS。

这些信息都可以从上图中得到。

- 分享

- 举报

暂无数据

暂无数据-

浏览量:6385次2021-01-30 01:09:16

-

浏览量:10581次2020-12-13 19:59:59

-

浏览量:7031次2021-01-31 01:07:50

-

浏览量:848次2023-10-09 18:20:20

-

浏览量:1694次2023-10-09 18:13:57

-

浏览量:8210次2021-02-06 22:29:19

-

浏览量:8336次2020-12-27 18:30:21

-

浏览量:5858次2021-01-31 04:24:47

-

浏览量:19332次2020-12-06 18:59:36

-

浏览量:6143次2021-03-22 01:26:53

-

浏览量:3183次2021-11-20 15:15:21

-

浏览量:4706次2021-11-20 15:17:49

-

浏览量:3845次2021-11-20 15:05:18

-

浏览量:5051次2021-03-18 22:57:24

-

浏览量:10785次2021-01-17 00:16:33

-

浏览量:8711次2021-01-09 02:07:52

-

浏览量:9366次2021-02-20 17:50:13

-

浏览量:13451次2021-01-01 02:53:29

-

浏览量:6780次2021-03-14 02:34:44

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友