高速串行总线实践(1)Xilinx Virtex-4 RocketIO的端口和属性

前言

从本篇开始,正式进入Xilinx的具体器件MGT的实践篇,从数据手册、demo例程、网站论坛以及实践经验入手,一起体会MGT知识之浩瀚!

用户手册约定事项

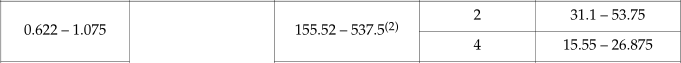

用户手册会约定一些共识(如Channel与Transceiver之间的关系:在Xilinx器件中等价!),供使用者参考,例如下面是Xilinx FPGA 器件Virtex-4手册约定的一些共识:

端口和属性名称 RocketIO收发器原语的所有输入和输出端口均以大写字母表示。 RocketIO收发器的属性可以用带下划线的大写字母或所有大写字母表示。当假定为相同频率时,RXUSRCLK和TXUSRCLK称为USRCLK,可以互换使用。 RXUSRCLK2,TXUSRCLK2和USRCLK2也是如此。

Comma定义 逗号是收发器使用的 "K "字符,用于对齐字节/半字边界上的串行数据(取决于使用的协议),以便将串行数据正确解码为并行数据。

抖动定义 抖动的定义是信号的重要瞬时与理想位置在时间上的短期变化(ITU)。抖动通常用单位间隔(UI)的小数点表示,例如,0.3 UI。

总抖动(DJ + RJ)定义

确定性抖动(DJ)– DJ是与数据模式有关的抖动,由于介质的损耗效应而产生的符号间干扰(ISI))。DJ是线性加成的。 随机抖动(RJ)– RJ是由于随机源引起的,例如热噪声和闪烁噪声等。 RJ是平方和的加法并遵循正态分布。

MGT定义 MGT术语是指Virtex-4 RocketIO千兆位收发器。明确指出了前几代产品:Virtex-II Pro RocketIO或Virtex-II Pro X RocketIOX。

RocketIO收发器基本架构

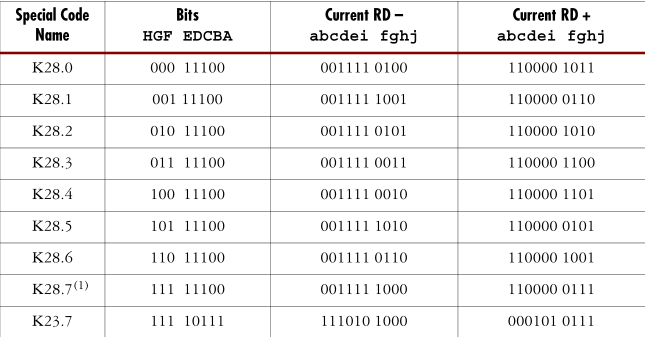

Virtex-4 FPGA MGTs 数量

V4 FPGA不同型号设备具有不同数量的FPGA,如下图:

上图XC4VFX60型号的FPGA具有不同数量的MGT核,这是根据不同封装而区分的。

MGT支持的通信标准

收发器模块设计为可以在每个通道622 Mb / s至6.5 Gb / s的任何串行比特率下工作,包括下表所列的通信标准所使用的特定比特率。

注:通道和Transceiver对应,一个通道即为一个收发器。

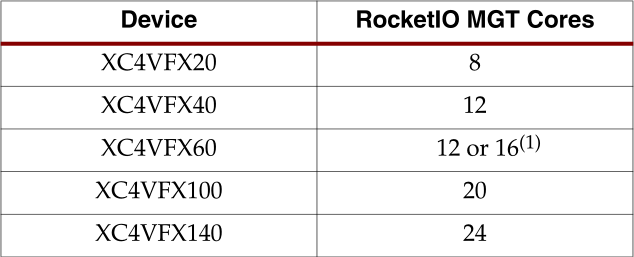

MGT架构框图

注:不支持64B/66B编解码;

有关收发器(Transceiver)架构框图在之前的MGT通用架构中就提到过,高速串行总线设计基础(三)SERDES的通用结构介绍, 如接收端的解串行化、Comma检测、8B/10B解码、通道绑定与时钟校正等;发送与接收是一个互逆的过程,发送端有8B/10B编码、缓冲FIFO、解扰、并串转换等。

在Xilinx Virtex-4的Transceiver结构中,还支持动态重配置等其他功能;

不得不提的是Xilinx中MGT的具体结构的专业术语,Xilinx V4 RocketIO MGT收发器由PMA以及PCS组成。

通俗而言:

PMA(Physical Media Attachment )由一些较为硬(模拟)的部分组成; PCS(Physical Coding Sublayer)由一些较为软(数字)的部分组成;

下面具体解释:

PMA包含串行/解串器(SERDES)、TX和RX输入/输出缓冲器、时钟发生器和时钟恢复电路。PMA包含串行器/解串器(SERDES)、TX和RX输入/输出缓冲器、时钟发生器和时钟恢复电路。PCS包含8B/10B编码器/解码器和支持通道绑定和时钟校正的环形缓冲器。 不知大家看到结构中Gearbox这个结构了没有?从字面上看,Gearbox是变速箱的意思,可是并不是太好理解,Gear是齿轮,Box是盒子,箱子,可以理解为一个模块罢了。有了这些通俗的印象,可以告诉你Gearbox是Xilinx GTX/GTH提供的支持其他编码方式(如64B/66B编码等)的模块,Gearbox的知识远非这些,更多内容后续会有专题。

本节不重点介绍这些内容,具体介绍参考后续博文。

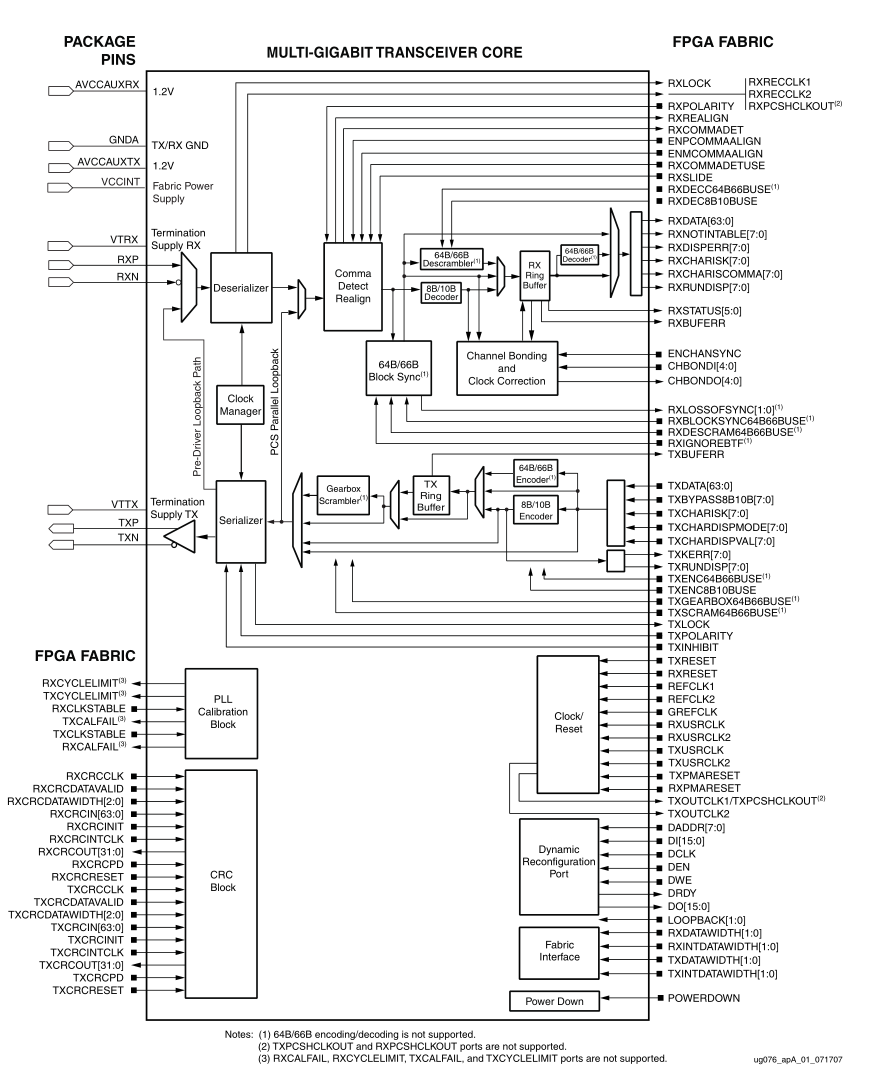

并行数据时钟与数据速率之间的关系

这个话题在过往的博客中也提到过:FPGA设计心得(13)aurora的线速率及其用户时钟之间的关系?

这篇博客中讲的是用户时钟,其实就是MGT中的并行数据时钟,数据速率也指的是串行数据速率,即线速率。 至于数据速率与并行数据时钟之间的关系,可以由下面一句话总结:

如果MGT采用的是8B/10B编码,则线速率v与并行数据时钟频率Fp之间的关系为v =Fp x W x (8 + 2) ,其中W为数据位宽,以字节为单位 。其中8d的含义是一个字节具有的比特数,2的含义是一个字节通过编码得到的比特数。如果不采用编码,则公式:v =Fp x W x 8

在之前的博客中是通过Verilog逻辑以及aurora IP核一起得出该关系,这里通过Virtex-4支持的通信协议来入手,一起来看下这种关系:

去两个典型的来说明问题:

对Aurora发射而言, 如下截取一栏,数据速率为0.622-1.075,如果并行数据为2字节,则经过8B/10B编码后的数据比特数为20bit,据此可推算并行数据的频率为31.1MHz至53.75MHz,一个简单的乘除法,没有问题吧。

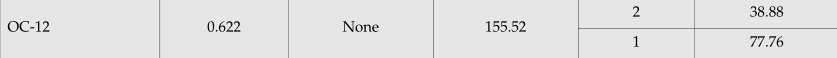

在举一个没有编码的通信协议OC-12,如下图,如果并行数据位宽为2,即16bit,数据速率为0.622Gbps,则并行数据速率为38.88。

以上足以说明此关系,其他请自行验证。

RocketIO MGT的配置方式

配置RocketIO收发器有两种方法:

静态配置。在设计时使用端口绑定和属性设置的组合配置收发器,以支持特定协议。 动态配置。通过驱动端口和操作动态重配置端口(DRP)来配置收发器,以修改MGT的运行时配置。

RocketIO MGT原语的端口

RocketIO MGT原语包含105个端口。差分串行数据端口(RXN,RXP,TXN和TXP)直接连接到外部焊盘。其余101个端口均可从FPGA逻辑访问。

配置端口的详细信息可见数据手册:UG076,这里不全部给出,仅仅挑出感兴趣的几个作为示例: 例如有关时钟状态的端口(PMA端口):

RXLOCK:输出端口,设置为逻辑1时,表示接收器已锁定到参考时钟或已锁定到输入数据。逻辑0表示接收器未锁定。可能的原因包括没有参考时钟,不正确的参考时钟频率,不正确的属性配置,未施加PMA电源或接收器无法锁定数据,并且正在重新锁定本地参考时钟。切换RXLOCK信号表示成功“粗略”锁定到本地参考时钟,但未成功锁定输入数据。

RXRECCLK1 :输出端口,从输入数据中恢复时钟;

RXRECCLK2 :输出端口,从输入数据中恢复时钟。不应用于为用户逻辑;而是使用RXRECCLK1。

TXLOCK:当设置为逻辑1时,表示发送器PLL被锁定到参考时钟。在锁定获取期间,此输出在逻辑0和逻辑1之间循环。当输出保持逻辑1状态时,发送器PLL被锁定。无法获取或保持锁定可能是由于没有参考时钟,参考时钟频率不正确,属性配置错误或未施加PMA电源引起的。

TXOUTCLK1:基于发送器参考时钟从PLL导出的发送器输出时钟。

TXOUTCLK2:从PCS中的PCS TXCLK域发送输出时钟。时钟源取决于PCS时钟配置。

如有关8B/10B编解码的端口(PCS端口):

RXCHARISK:输出端口,位宽为8,如果启用了8B/10B解码,断言则表示接收到的数据是一个 "K "字符。 TXCHARISK:如果TXENC8B10BUSE=1(8B/10B编码器使能),TXCHARISK[7:0]在相应的字节通道中发出TXDATA字节的K定义信号。

接收发送数据相关端口:

RXDATA:输出端口,64位,在FPGA用户结构上接收数据。 RXDATA [7:0]始终是接收到的第一个字节。 RXDATAWIDTH:输入端口,2位,指示FPGA并行总线的宽度。 TXDATA:从FPGA用户结构发送8字节宽的数据。 TXDATA [7:0]始终是发送的第一个字节。 TXDATAWIDTH:指示FPGA并行总线的宽度。

与状态时钟相关的端口:

RXUSRCLK:输入端口,用于读取RX环形缓冲区的时钟。它还向收发器提供时钟CHBONDI和CHBONDO的时钟。通常,与TXUSRCLK相同。 RXUSRCLK2:输入端口,时钟输出为收发器和FPGA核之间的接收数据和状态提供时钟。通常,与TXUSRCLK2相同。 TXUSRCLK:与参考时钟同频的时钟输入。该时钟用于写入TX缓冲区,必须与参考时钟锁频。 TXUSRCLK2:时钟输入,为FPGA核与收发器之间的发送数据和状态提供时钟。通常与RXUSRCLK2相同。 GREFCLK:参考时钟(不建议在1G以上运行时使用备用时钟)。 REFCLK1:参考时钟(低抖动输入时钟)。 REFCLK2:参考时钟(低抖动输入时钟)。

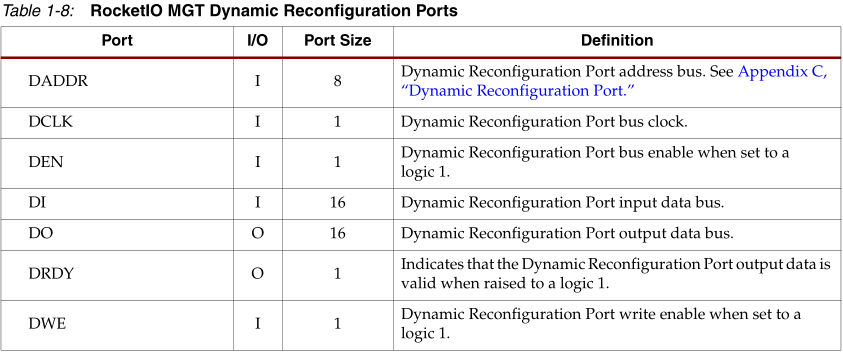

动态重配置端口:

DADDR:输入端口,8位,动态重配置端口地址总线。 DCLK:输入,动态重配置端口总线时钟。 DEN:输入,设置为逻辑1.时动态重新配置端口总线启用。 DI:输入,动态重配置端口输入数据总线。 DO:输出,动态重配置端口输出数据总线。 DRDY:输出,表示动态重新配置端口输出数据提高到逻辑1时有效。 DWE:输入,设置为逻辑1时动态重配置端口写使能。

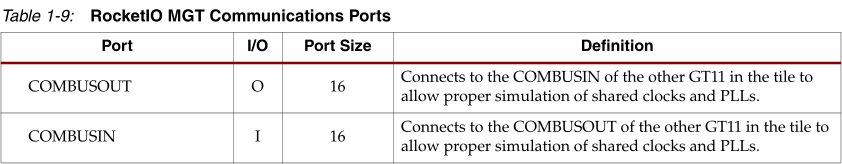

以上部分是针对MGT原语端口的部分介绍,更具体的有CRC端口,PMA端口,PCS端口,全局信号端口以及动态重配置端口,通信端口等。

前面说了,MGT原语拥有101个可访问端口,如此之多,定要从数据手册获得关键信息,用多少熟悉多少,暂时未用也可浏览以熟悉,如此可掌握。 下面是UG076提供的表格部分举例,各位有兴趣的可前往数据手册了解详情:

RocketIO MGT原语的属性

要完成对MGT原语的配置,光靠端口是不够的,还要有属性的配置。

属性是用于配置MGT的控制参数。收发器属性也是对收发器的控制,用于调节数据宽度和编码规则, 但它们是通过调用原语以 "软 "形式配置成组的控件。

MGT还包含默认情况下设置为特定值的属性。包括通道绑定设置和时钟校正序列。下面手动介绍部分属性,具体属性的内容还请查看UG076进一步了解。

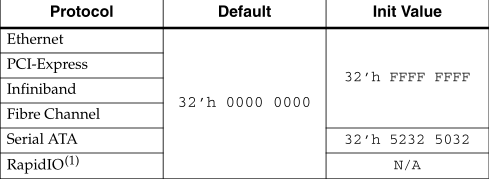

例如CRC属性:

RXCRCINITV AL:设置接收器CRC初始值。必须为每个使用32位CRC的协议定义以下内容:

RXCRCENABLE:使能RX CRC块。 FALSE:RX CRC禁用。 TRUE:RX CRC使能。 TXCRCENABLE:使能TX CRC块。 FALSE:TX CRC禁用。 TRUE:TX CRC使能。

例如PMA属性:

RXPMACLKSEL:REFCLK1,REFCLK2,GREFCLK。选择接收PLL的参考时钟输入。 REFCLK1:选择REFCLK1输入(DRP值00)。 REFCLK2:选择REFCLK2输入(DRP值01)。 GREFCLK:选择GREFCLK输入(DRP值10)。 TXABPMACLKSEL:REFCLK1,REFCLK2,GREFCLK。选择共享Tile发送PLL的参考时钟输入。 REFCLK1:选择REFCLK1输入(DRP值00)。 REFCLK2:选择REFCLK2输入(DRP值01)。 GREFCLK:选择GREFCLK输入(DRP值10)。 TXPHASESEL :FALSE:选择GREFCLK作为同步时钟TRUE:选择PCS TXCLK作为同步时钟

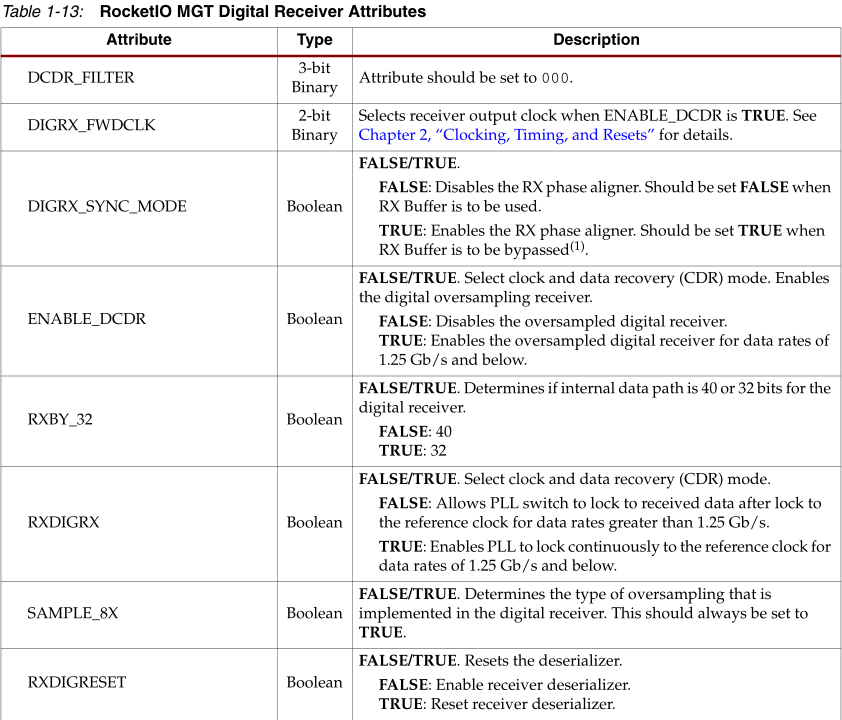

例如PCS属性:

CHAN_BOND_SEQ_LEN:整数(1、2、3、4、8)定义通道绑定序列的字节长度。这定义了收发器匹配以检测信道绑定机会的序列的长度。

CLK_CORRECT_USE:FALSE:永久禁用时钟校正(速率匹配)的执行。在这种情况下,时钟RXUSRCLK必须与RXRECCLK1 / RXRECCLK2锁频。 TRUE:启用时钟校正(正常模式)。

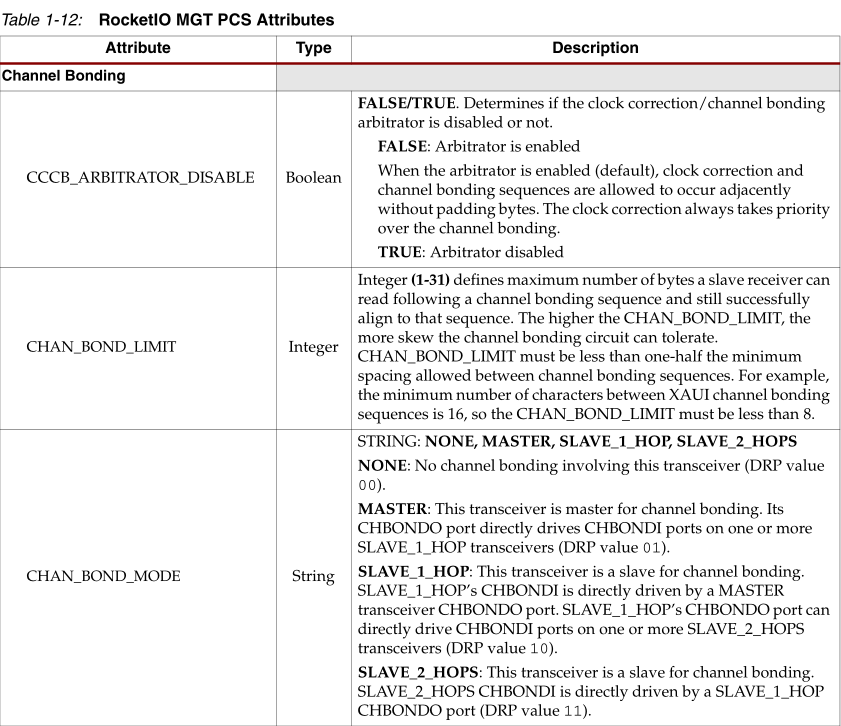

RocketIO MGT数字接收器属性

ENABLE_DCDR:FALSE/TRUE。选择时钟和数据恢复(CDR)模式。启用数字过采样接收器。 FALSE:禁用过采样的数字接收器。 TRUE:为1.25 Gb / s及以下的数据速率启用过采样的数字接收器。

同理,下面给出预览表:

- 分享

- 举报

暂无数据

暂无数据-

浏览量:13133次2020-12-05 03:10:25

-

浏览量:12467次2020-11-30 23:56:05

-

浏览量:19827次2020-12-07 00:56:53

-

浏览量:10278次2020-12-20 00:26:35

-

2020-07-01 11:02:45

-

浏览量:15094次2020-12-16 01:39:47

-

浏览量:17772次2020-12-03 00:29:52

-

浏览量:11119次2020-12-12 23:47:07

-

浏览量:13433次2020-12-10 00:29:44

-

浏览量:15824次2020-12-15 01:26:18

-

浏览量:8815次2020-12-20 14:19:53

-

浏览量:14153次2020-12-07 00:58:01

-

浏览量:12463次2020-12-19 13:31:48

-

浏览量:1933次2021-11-25 09:46:32

-

2020-07-17 10:40:24

-

浏览量:3852次2022-06-08 14:16:22

-

浏览量:6740次2021-07-09 15:17:28

-

浏览量:2509次2022-09-26 15:03:03

-

浏览量:16402次2021-07-12 23:53:03

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友