高速串行总线设计基础(八)揭秘SERDES高速面纱之CML电平标准与预加重技术

前言

对于数字工程师来说,我们可能关注的仅仅是本文中的差分信号电平标准以及预加重技术,CML电平标准是Transceiver技术的首选,在Xilinx的GTX/H以及以此为底层架构的众多协议,发送以及接收差分信号线都是以此为标准,在管脚约束页面上,也是没有开放出来的。至于预加重技术,毫无疑问,是高速串行技术的必然选择,这是因为在高速链路中处于过渡阶段的bit会受到ISI的影响等。

可能对于数字工程师来说,本文过于硬件化,过于物理化,应该是一般硬件工程师应该关注的内容,但作为FPGA上的数字工程师来说,我们几乎每天都与高速串行总线打交道,而你却不知无论是X家提供的或者A家提供的Transceiver或Serdes背后是怎么的硬核电路,未免也太不专业了!

物理信号

吉比特SERDES的物理实现通常采用基于差分的电接口的形式。共有三种常见的差分信号形式:

低压差分信号(LVDS); 低压伪发射极耦合逻辑(LVPECL); 电流模式逻辑(CML);

吉比特链路首选CML。它是最常见的接口类型,通常提供交流或直流终端和可选择的输出驱动。一些输入提供内置的线路均衡和/或内部端接。通常,终端阻抗也是可选的。

LVDS是一般差分信号常用的接口类型,例如Xilinx的管脚约束中时常对差分引脚的约束,其电平选择为:

而CML即电流模式逻辑;基于差分的电接口,非常适合吉比特链路。

我们知道,在上述引脚约束页面,Transceiver的TXP/TXN以及RXP/RXN的引脚电平标准是不可选的,其实只是没有开放选择,人家固定好了,不需要你选择,如下相关数据手册也有体现:

RocketIO™ Transceiver User Guide

基于高速的需求和传统技术的弊端,Xilinx在Virtex2 Pro以及更高系列的部分FPGA内部集成了能实现高速数据收发RocketI/O模块,采用了CML(CurrentModeLogic)、CDR、线路编码(8B/10B)和预加重等技术的RocketI/O硬核模块,可极大地减小时钟扭曲、信号衰减和线路噪声对接收性能的影响,从而使传输速率进一步提高,最高可达10Gbps以上,可用于实现吉比特以太网、PCI-Express等常用接口。

基于高速的需求和传统技术的弊端,Xilinx在Virtex2 Pro以及更高系列的部分FPGA内部集成了能实现高速数据收发RocketI/O模块,采用了CML(CurrentModeLogic)、CDR、线路编码(8B/10B)和预加重等技术的RocketI/O硬核模块,可极大地减小时钟扭曲、信号衰减和线路噪声对接收性能的影响,从而使传输速率进一步提高,最高可达10Gbps以上,可用于实现吉比特以太网、PCI-Express等常用接口。

这便是Xilinx的高速互联解决方案。

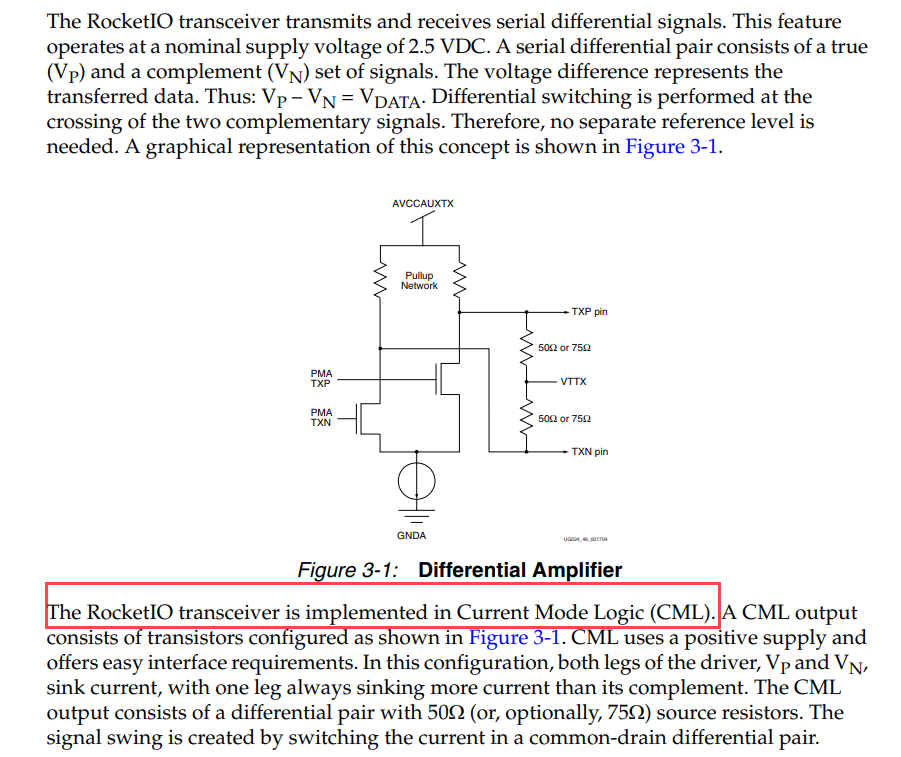

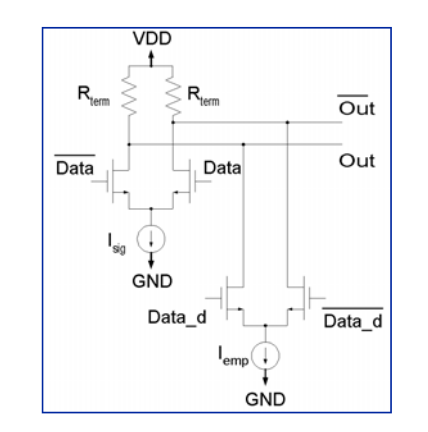

下图显示了CML类型的驱动程序。高速驱动器的概念非常简单,两个电阻之一始终流过的电流与另一个电阻流过的电流不同。

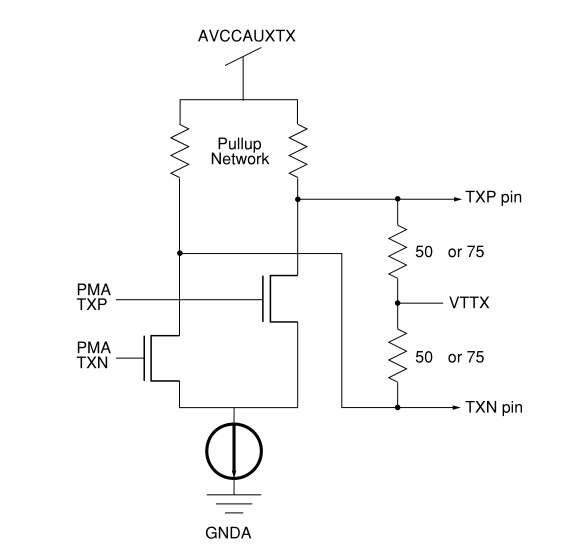

下图说明了MGT接收器。

预加重

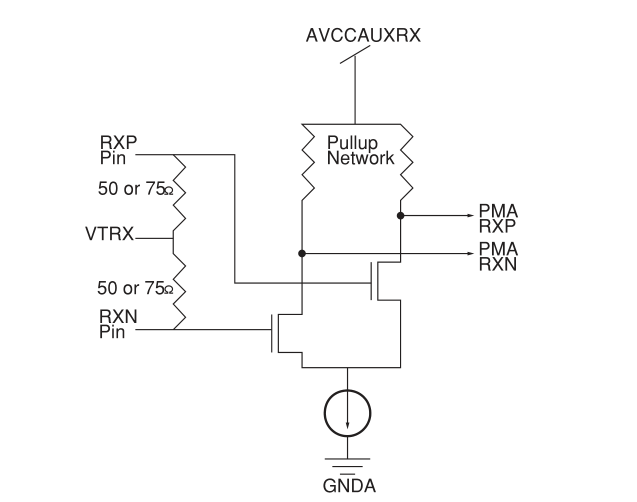

吉比特驱动器的最重要的特性也许是其执行预加重的能力。预加重是指在过渡开始时故意过度驱动。在没有经验的人眼里,它看起来像一个故障,它看起来像过冲和欠冲,可以表明设计不好。为了理解为什么要这样做,我们需要了解符号间干扰(ISI)。

当串行流中包含若干个相同值的位时间,然后是短的(1或2)相反值的位时间时,就会发生ISI(符号间干扰)。在较短的值时间内,介质(传输路径电容)的充电时间较短,所以产生的振幅较低。

如下图所示:

由上图可见,在多个连续的比特之后有一个持续时间较短的比特,这个比特就会受到ISI的干扰,产生较小的幅值。

由于存在ISI,持续时间较长的比特允许较大的充电时间,但是单比特的时间无法补偿。解决这个问题的办法是对每个过渡进行过载,而对任何连续的相同值的比特进行欠载,这有时称为去加重。

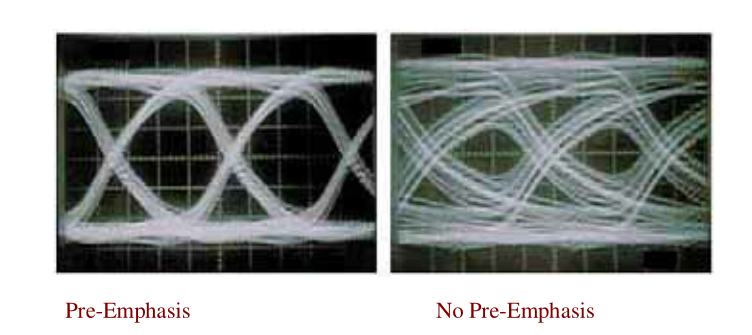

但使用了预加重后,眼图对比:

可见,预加重之后,信号的眼图轮廓变得更加的清晰,眼图的各项指标自然就好多了,这也是众多高速总线对外部高速串行信号进行处理的一种常见的办法,经过预加重等操作,让原本可能不达要求的信号变得质量好了起来。

可见,预加重之后,信号的眼图轮廓变得更加的清晰,眼图的各项指标自然就好多了,这也是众多高速总线对外部高速串行信号进行处理的一种常见的办法,经过预加重等操作,让原本可能不达要求的信号变得质量好了起来。

关于眼图的相关内容,可见:高速串行总线设计基础(四)眼图的形成原理

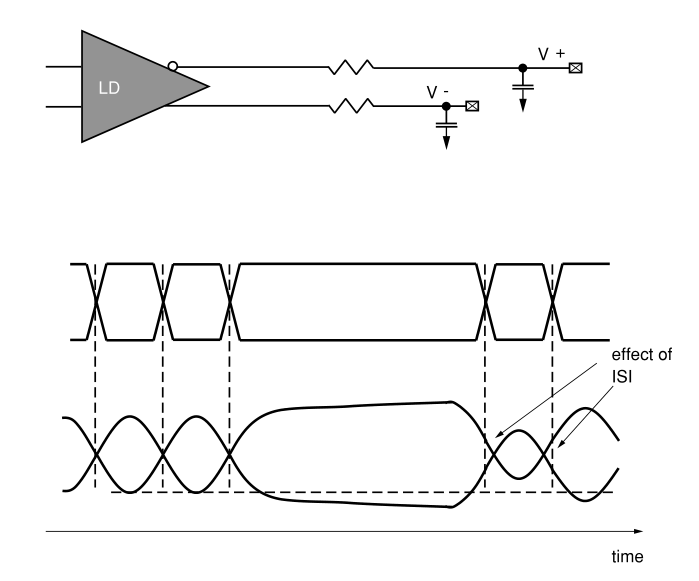

预加重可以通过使用两个CML驱动器并联来实现,其中一个驱动器在另一个驱动器之后延迟一个比特时间。下图显示了一个示例电路和驱动晶体管获得输出的波形。

差分传输线

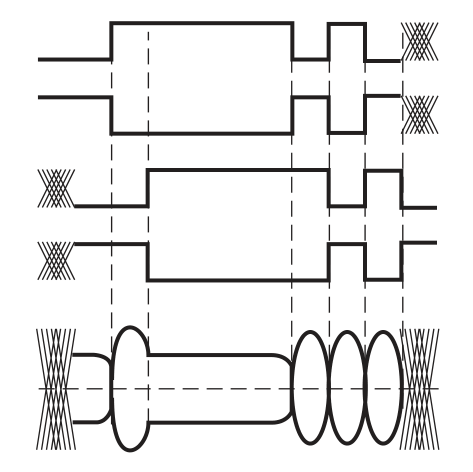

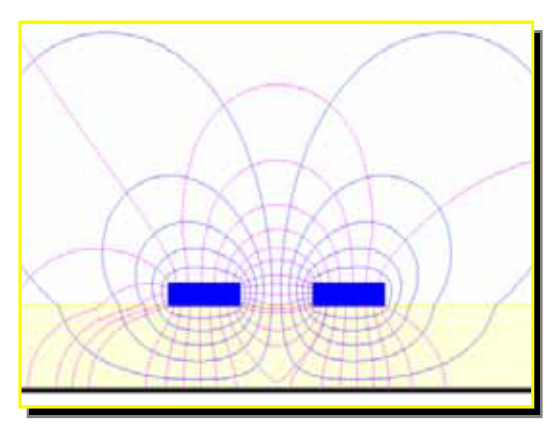

数字设计工程师和PCB设计人员曾经认为迹线(traces)是简单的互连或导线。事实上,原型的建立是使用一种被称为线经(wire warping)的技术。传输线和传输线理论不一定被应用。当迹线的传播延迟是信号上升时间的极小部分时,这是令人满意的。但随着信号频率的增加,传输线理论不得不进入PCB设计过程。对于吉比特操作来说,这不仅包括传输线和受控阻抗,还包括差分对受控阻抗。差分对阻抗匹配迹线是指相邻运行的两条迹线。线对之间的间距允许迹线之间发生耦合。如果迹线相距较远,则称为弱耦合。如果迹线较近,则称为强耦合。

弱耦合:

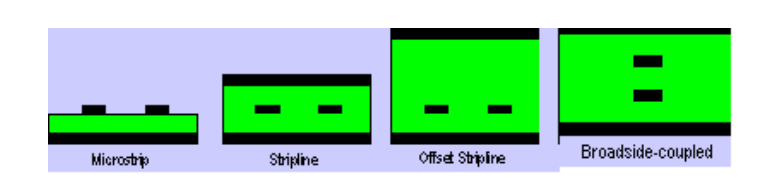

如果给定的走线长度和叠层会产生给定的阻抗,则耦合也会影响走线的阻抗。差分对的相同几何形状将具有不同的阻抗。任何给定阻抗的确切尺寸会因材料而异,但电路板制造商通常可以提供确切尺寸。称为场求解器的工具/数学模型也可以计算数字。下图显示了受控阻抗差分迹线的主要类型-微带,带状线,偏移带状线和宽边耦合。

下表包含受控阻抗差分走线类型。

参考资料

A Comparison of CML and LVDS for High-Speed Serial Links

- 分享

- 举报

暂无数据

暂无数据-

浏览量:14235次2020-12-16 01:39:47

-

浏览量:12950次2020-12-10 00:29:44

-

浏览量:10689次2020-12-12 23:47:07

-

浏览量:13580次2020-12-07 00:58:01

-

浏览量:12418次2020-12-05 03:10:25

-

浏览量:8321次2020-12-20 14:19:53

-

浏览量:9605次2020-12-20 00:26:35

-

浏览量:11855次2020-11-30 23:56:05

-

浏览量:19270次2020-12-07 00:56:53

-

浏览量:17027次2020-12-03 00:29:52

-

浏览量:11706次2020-12-19 13:31:48

-

2020-12-27 02:15:14

-

浏览量:3159次2020-11-25 10:03:26

-

浏览量:3445次2020-08-17 12:21:14

-

浏览量:1722次2023-12-25 13:44:26

-

浏览量:2263次2023-12-25 13:49:55

-

浏览量:314次2024-11-25 11:46:32

-

浏览量:2005次2019-11-11 10:43:40

-

浏览量:3119次2020-11-19 09:51:59

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友