高速串行总线设计基础(三)SERDES的通用结构介绍

前言

上一篇文档,介绍了MGTs,我们知道它的一个别名为SERDES,就是如此,这篇文章我们来谈一下通用的SERDES架构。无论是X家的Transceiver还是A家的SERDES,或者其他什么家的某某吉比特收发器,原理其实都是大同小异,离不开一些共同的结构。

最后我们也会同时展示大家常用的SERDES或者Transceiver的结构,它们通常都是通用架构的扩展。

SERDES的基本构造

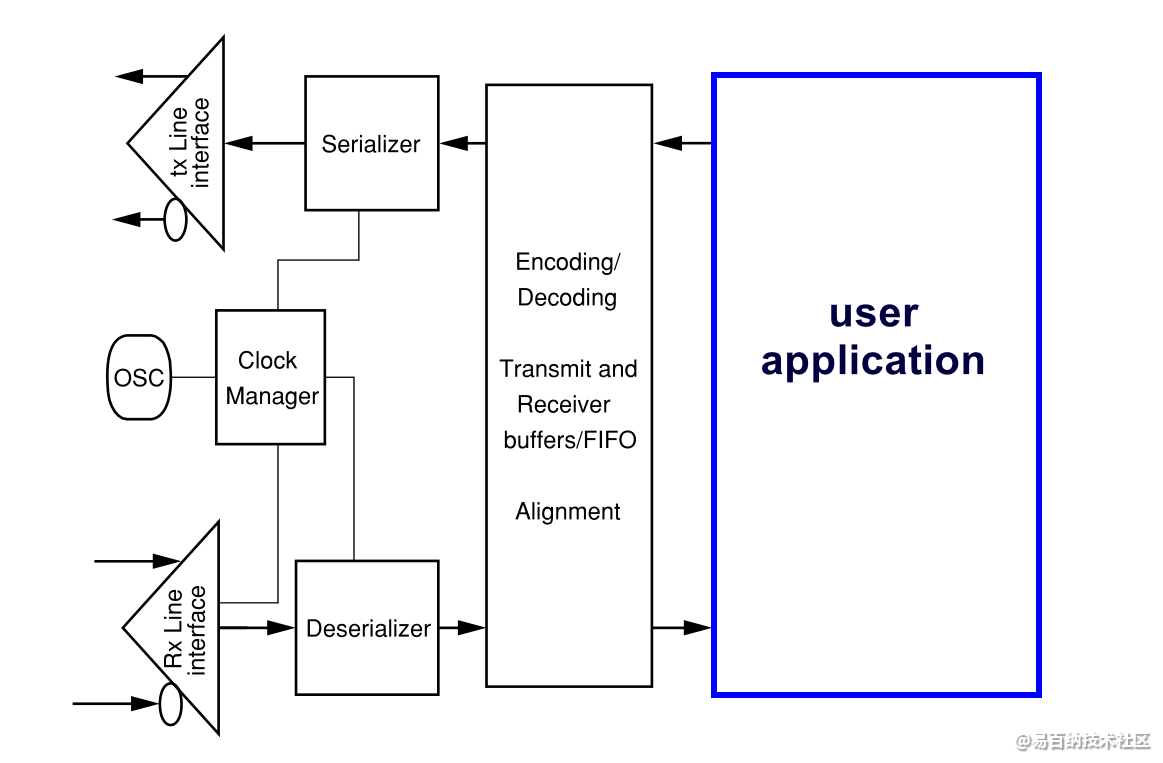

简单说来,SERDES的基本框图如下:

大概就是由发送线,接收线,串行化模块和解串行化模块,时钟管理模块,编码解码模块,发射接收缓冲模块(FIFO)以及Alignment模块。

其实还有一个由用户根据接口协议的具体内容而自定制的用户逻辑模块,用来产生发送数据以及解析接收数据,这是唯一用户可以灵活处理的地方,也是逻辑工程师可以进行电路设计(Verilog设计)的地方。

如下图:

其中,发送线即图中tx Line interface以及接收线(Rx Line Interface)是与外部芯片进行交互的串行线路,具体可以分别由一对或者多对差分信号线组成。一般而言,1对称之为X1模式,2对X2,以此类推,n对即Xn。这类差分信号线越多,传输数据的带宽就越大,假如一对差分信号线的传输带宽为3.125Gbps,则n对为n*3.125Gbps。

串行化模块(Serializer)即并串转换(PISO)模块,用户逻辑产生待发送数据,经过8B/10B编码或者其他类型的编码,加扰,进入缓冲区等待操作,最终经过并串转换模块,转换成串行数据通过发送线发送出去。

同理,解串行化模块(Deserializer)是串行化模块的逆过程,就是将串行差分线接收的串行数据经过串并转换(SIPO)模块转换为并行数据,之后经过解码,解扰,等操作后的并行数据,交给用户接口,用户进行对该并行数据进行解析。

为什么会有上图中的Transmit and Receiver buffers/FIFO呢?

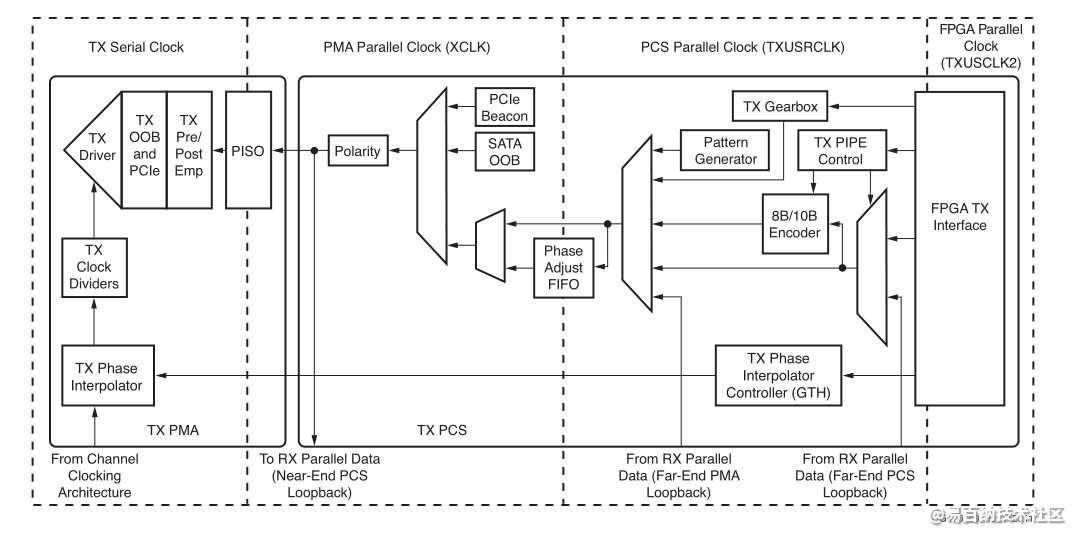

该模块的一个最重要的作用就是进行跨时钟域转换!由于SERDES中涉及的时钟不只有一个,拿我们的Xilinx的Transceiver的一个通道的发射部分而言,如下图:

可以暂时不用管其他部分,关于Xilinx家的Transceiver,后续文章我会专门介绍。

我们仅仅看它的时钟域划分就知道,为什么存在跨时钟域处理这回事了。

上图中的Phase Adjust FIFO的作用就是通用SERDES中的Transmit and Receiver Buffers/FIFO的具体设计,解决的问题就是要在两个时钟域之间传输数据,必须进行速率匹配,并且要解决两个时钟域之间的所有相位差,简单来说,就是跨时钟域处理。

跨时钟域处理中,FIFO是两个不同时钟域之间数据传输的最常用的处理方式,这无论在什么时候都是笔试面试的重点,我在学生时期准备过相关的内容,见:

至于时钟管理模块,那就很明显了,它管理了各种时钟的问题,包括时钟分频倍频以及时钟恢复等。

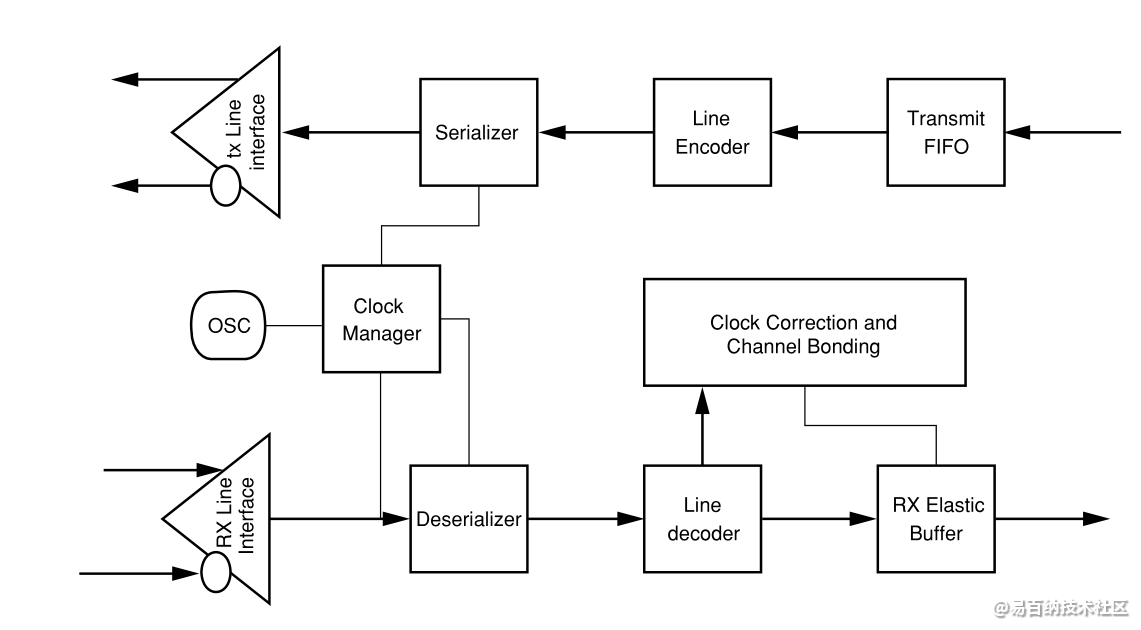

上面对SERDES的一般架构进行了简单的口述,好像没什么条理,下面给出一个通用的SERDES框图,并对各模块进行简单定义。

SERDES的通用框图

如下图,为SERDES的通用框图,它是对上一节中的SERDES框图的一个细化。下面给出各个模块的定义。

- 串行器(Serializer):获取n位并行数据,其速率为y,然后将它转化为串行数据流,速率为y的n倍;

- 解串器(Deserializer):以n的y的速率获取串行数据流,并将其转换为速率为y的宽度为n的并行数据;

- 接收对齐(Rx (Receive) Align):Rx(接收)对齐:将输入的数据对齐到适当的字界。可以使用几种不同的机制,从自动检测和对齐一个特殊的保留位序列(通常称为Comma)到用户控制的位滑移;

- 时钟管理器(Clock Manager):管理各种时钟需求,包括时钟倍频,时钟分频和时钟恢复;

- 发送FIFO(Transmit FIFO):允许在发送之前存储传入的用户数据;

- 接收FIFO(Receive FIFO):允许在删除之前存储接收到的数据(缓存数据);在需要时钟校正的系统中至关重要;

- 接收线接口:模拟接收电路包括差分接收器,并且可以包括有源或无源均衡;

- 发送线接口:模拟发射电路通常允许不同的驱动强度。它还可以允许预加重发射;

- Line Encoder:将数据编码为更友好的数据格式。这通常涉及消除长序列的不变位。可能还会调整数据,以实现一平衡和零平衡。 (这是一个可选块,有时不包含在SERDES中。);

- 线路解码器:从线路编码数据解码为纯数据。 (这是一个可选块,有时在SERDES之外完成。);

- 时钟校正和通道绑定:允许校正发送时钟和接收时钟之间的差异。还允许在多个通道之间进行偏斜校正。 (通道绑定是可选的,并不总是包含在SERDES中。)

可以包括其他可能的功能,例如循环冗余校验(CRC)生成器,CRC检查器,4b / 5b,8b / 10b,64b / 66b的多种编码和解码,可设置的加扰器,各种对齐方式和菊花链选项以及可配置时钟的前端和后端。

市场上的SERDES或Transceiver展示

下面列举了两家的吉比特收发器的架构,但本文暂时不做具体解释,具体内容会在本系列的后面介绍。

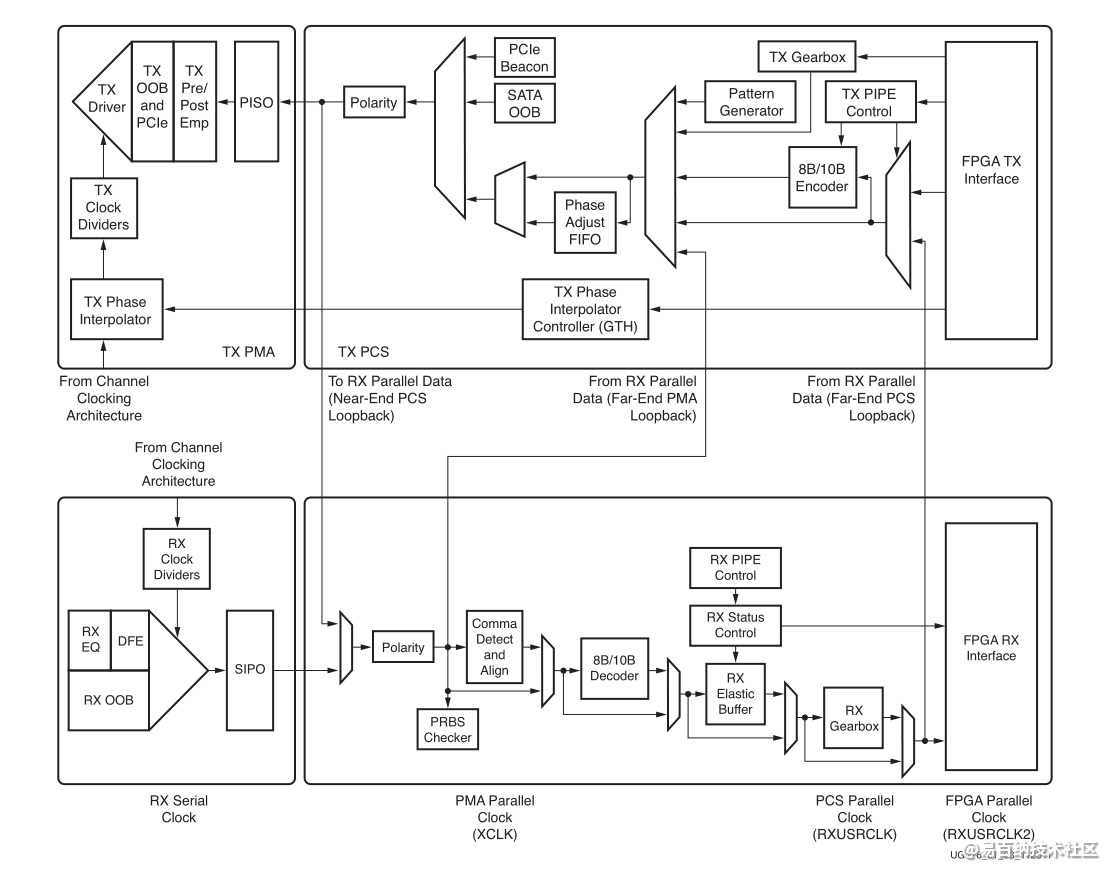

Xilinx的Transceiver架构展示

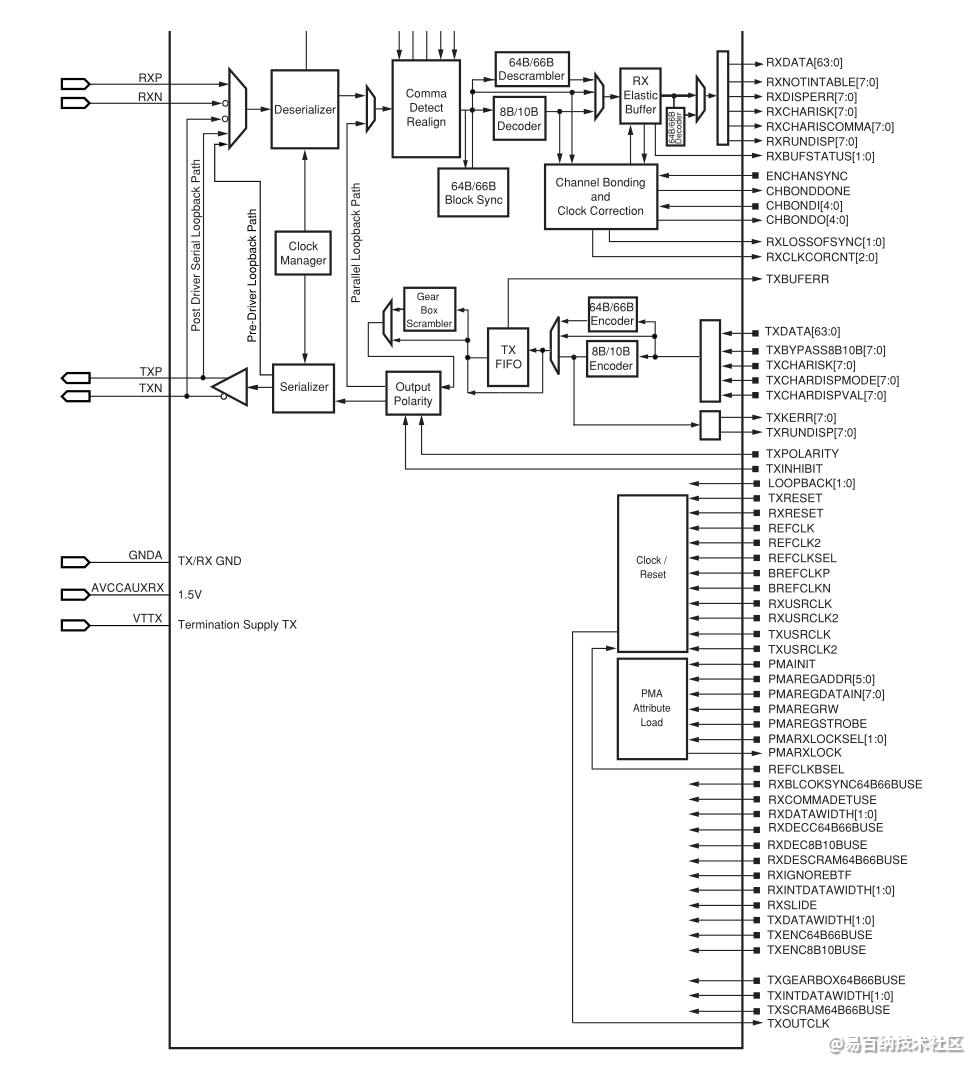

为了简化浏览,我们仅仅给出一个通道的Transceiver的结构(7系列FPGA为例):

Altera的SERDES介绍

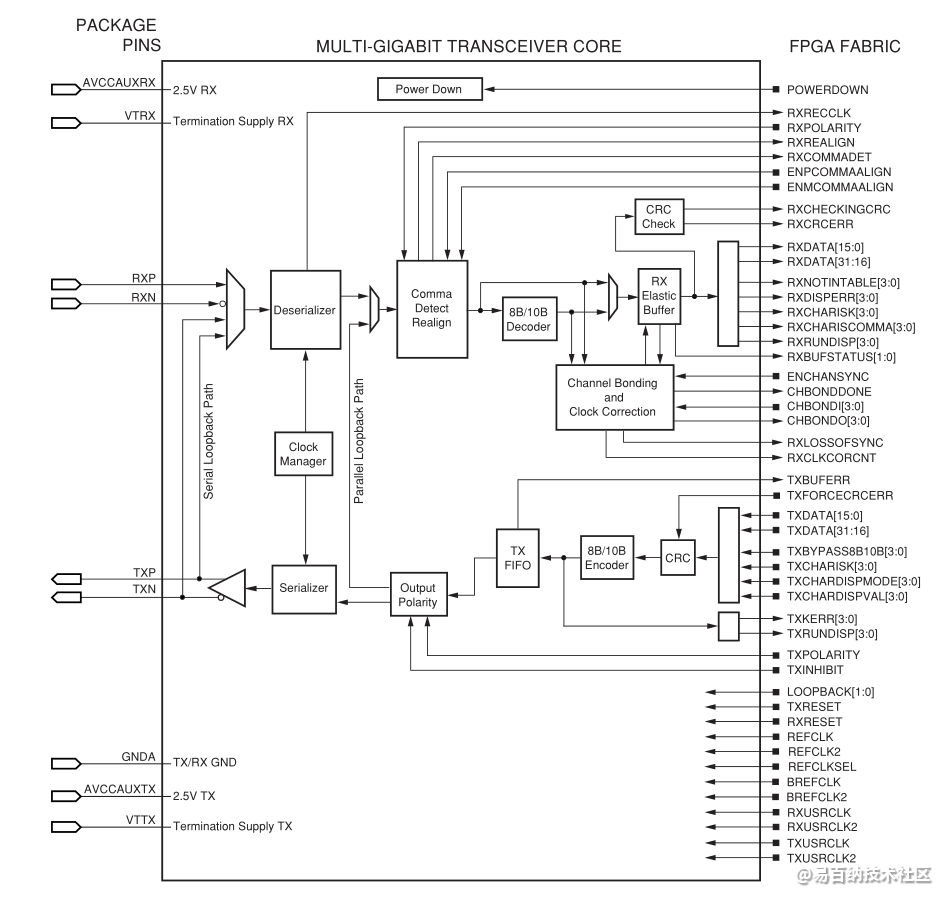

Virtex™-II Pro X RocketIO™ SERDES结构框图:

Virtex-II Pro RocketIO SERDES结构框图:

往期回顾

高速串行总线设计基础(二)什么是MGTs以及MGTs的优势在哪里?

更新中,敬请期待!

参考文章

UG476

UG576

FPGA基础知识极简教程(7)详解亚稳态与跨时钟域传输

- 分享

- 举报

暂无数据

暂无数据-

浏览量:11855次2020-11-30 23:56:05

-

浏览量:14235次2020-12-16 01:39:47

-

浏览量:10689次2020-12-12 23:47:07

-

浏览量:12950次2020-12-10 00:29:44

-

浏览量:15250次2020-12-15 01:26:18

-

浏览量:9605次2020-12-20 00:26:35

-

浏览量:13580次2020-12-07 00:58:01

-

浏览量:19271次2020-12-07 00:56:53

-

浏览量:8321次2020-12-20 14:19:53

-

浏览量:17027次2020-12-03 00:29:52

-

浏览量:11708次2020-12-19 13:31:48

-

2020-12-27 02:15:14

-

浏览量:2266次2023-12-25 13:49:55

-

浏览量:1723次2023-12-25 13:44:26

-

浏览量:881次2023-06-02 11:37:34

-

浏览量:3445次2020-08-17 12:21:14

-

浏览量:4090次2020-11-19 09:54:23

-

浏览量:3119次2020-11-19 09:51:59

-

浏览量:2583次2020-11-18 09:34:34

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友