高速串行总线设计基础(二)什么是MGTs以及MGTs的优势在哪里?

前言

话说,很久以前,并行总线称霸电子行业的方方面面,无论是芯片之间的通信还是板间通信。

就连大名鼎鼎的PCI Express总线也是从并行总线PCI发展而来,诸如此类的例子很多,有兴趣的可以参考:总线的各种基础问题

为什么后来就往高速串行总线方向发展了呢?

几乎任何地改变都是趋利避害:拿芯片间通信为例,过去几乎完全是并行总线,碍于技术限制,使用串行总线所需的serialize(串行化)以及deserialize(解串行化)所需的逻辑量远远超过了减少引脚数量所带来的节省。得不偿失!

这样的时代过去了,如今芯片能做到7nm以下,在极小的硅中可以实现数量惊人的逻辑,serdes可以以非常低的成本包含在零件中,优势还远非如此,总之,技术的突破让高速串行总线技术引领了未来。

如今,高速串行总线应用于电子行业的各个领域,例如,医疗、网络、视频、通信以及军事等,并成为高速设计的首选。

下面正文内容将正式介绍高速串行总线的各方面优势。

在介绍MGT之前,想介绍下并行传输和串行传输的概念:

并行传输

avalon总线,axi总线以及axi 总线的变体axi stream以及axi framing等都是芯片内进行并行传输,以aurora的用户端信号axi framing以及axi streaming总线为例,它们在转换成串行比特流之前都是以并行的形式存在,所以,串并行总线都是相辅相成的,用途不同。

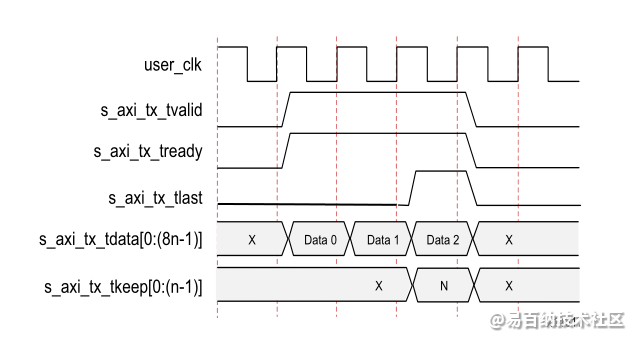

在并行传输中,通常使用附加的控制线为数据赋予不同的含义。如下图axi framing的通过valid,ready以及last等一系列控制信号控制数据的传输。

串行传输

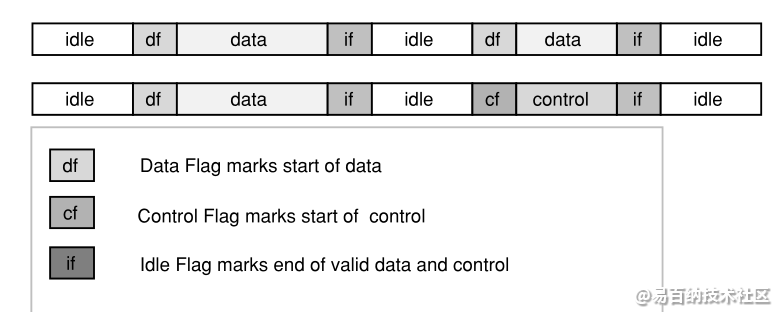

在串行传输中,通常添加一些标志将数据与空闲字符或控制字符区分开,标志话可以用于标记不同类型的信息,例如数据和控制字符:

MGTs是什么?

在讲MGT之前,先提出一个专业术语Gigabit,可以翻译为千兆比特,也可以直译为吉比特。我们平时听移动电信公司所说的千兆网,百兆网里的千兆就是Giga,同理,百兆即Mega。

Gigabit

为什么提吉比特这个术语呢?当然是和我们的高速串行总线有关,目前我们的高速串行总线的传输速率都是以Gbps为单位,即Gigabit per second,千兆比特每秒。

高速串行通道的一个常见的表达为transceiver,字面意思是收发通道,这几乎成为一个专用于高速串行总线的术语。

MGT Bank

后面我们会知道,在Xilinx以及其他平台(国产)的fpga上,这种transceiver不只一个,Xilinx的一个bank上就继承了4个通道的transceivers,我们称这样的Bank为MGT Bank。

显而易见,所谓的MGT Bank就是Mlti-gigabit transceivers Bank,含有多个串行收发专用通道的Bank。

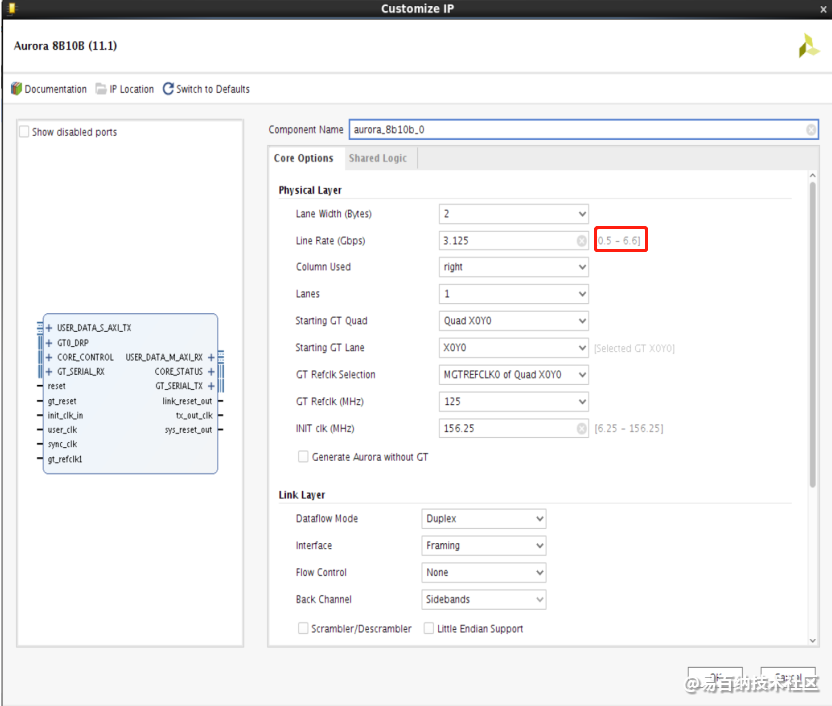

每个通道的串行速率可达数G比特,例如如下aurora的IP核定制页面:

多个通道呢?则是倍数关系!

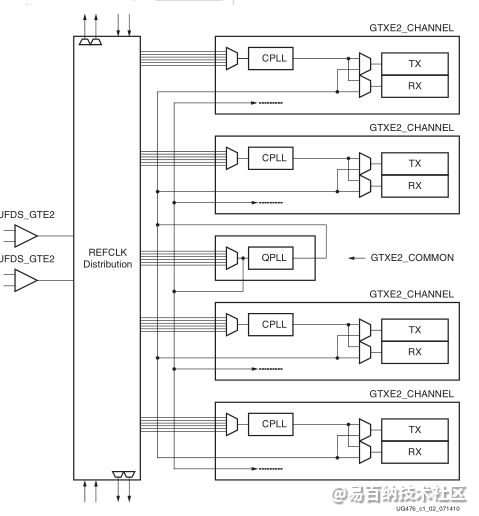

在Xilinx的Transceivers中,我们还可以知道,Xilinx芯片内部会把4个Transceiver通道原语(专用硬件结构)(GTXE2_CHANNEL)以及时钟模块(GTXE2_COMMON)合称为一个Quad,十分好理解,Quad就是四的意思呀。

详细信息可以参考文章:

GTX/GTH 物理层结构分析

MGTs

好了,现在知道什么是MGT了吧。

这里再次给出定义:

多吉比特SERDES的别称。接收并行数据,并允许通过串行链路传输高带宽数据。

后面,我们一般提到SERDES,就默认是MGT了,或者提到Transceiver,也统统都是高速串行收发器,。于时,别人问你,transceiver,就不要犹豫是transceiver还是Multi-gigabit transceivers,或者serdes了。

MGTs的优势何在?

说了这么多,还没有说为什么现在大家都首选高速串行总线?固然是优势决定,有哪些呢?

带宽高

这个就不用赘述了吧,上了以Xilix的FPGA为例,说了随随便便一个7系列的FPGA,就有很多个MGT Bank,每个Bank上都有4通道的Transceiver,一个通道的数据率就能达到好几Gbps,多个呢?

更何况Ultrascale架构的FPGA呢?

带宽大的优势很明显,对于雷达领域,视频领域等都是刚需。

引脚数量少

引脚数是试图将大量数据移入或移出芯片或电路板时遇到的第一个问题。输入和输出引脚的数量始终受到限制。串行总线相对于并行总线而言,很明显的一个优势就是节省引脚,尽管高速串行总线总是使用差分总线来进行数据传输,但相对于并行总线,引脚使用量仍然微不足道。

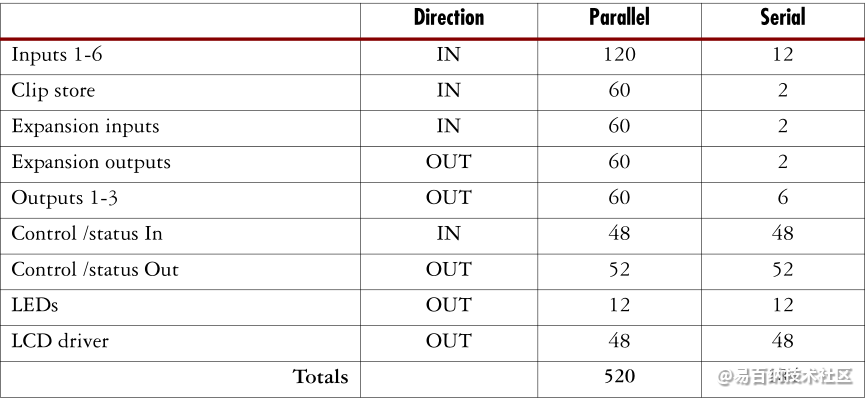

给个直观的对比,下面是某场景下的串并行总线使用引脚情况的对比:

SSO

SSO是Simultaneous Switching Outputs的缩写,这是电路设计人员需要考虑的问题。

单端并行总线输出在同时切换的时候,如果切换太多,接地反弹会产生大量噪声,解决这个问题,可以使用差分总线,但是使用差分总线会增加一倍的引脚使用量。引脚的加倍使用,在很多场景下,是不合适的。

EMI

同样,这也是电路设计人员必须考虑的问题,电磁干扰问题。

经验表明,随着时钟变得越来越快,EMI越来越严重。因此,千兆位设计似乎几乎是不可能的。但是,高速串行链路通常比运行速度较慢的大型总线表现出更少的辐射。这是因为正常运行的千兆链路需要出色的信号完整性。正如一位专家所说,“辐射发射问题实际上只是信号完整性问题。”

详细内容,可参考:

EMI

成本

使用MGT通常会降低总体系统成本。采用更小,更便宜的封装,连接器可以具有更少的引脚,并且电路板设计也可以更简单。

多协议

使用MGT的另一个好处是可以使用预定义的协议和接口标准。从Aurora到XAUI,已经存在可以满足许多不同需求的设计。

展望

MGTs具有高速,更少的引脚,更低的EMI和更低的成本使其成为许多通信设计中的理想选择。这些优势将确保它在未来的通信应用中继续使用。

参考文章

嵌入式高速串行总线技术:基于FPGA实现与应用

aurora数据手册

- 分享

- 举报

暂无数据

暂无数据-

浏览量:9611次2020-12-20 00:26:35

-

浏览量:19277次2020-12-07 00:56:53

-

浏览量:12426次2020-12-05 03:10:25

-

浏览量:11863次2020-11-30 23:56:05

-

浏览量:11718次2020-12-19 13:31:48

-

浏览量:8327次2020-12-20 14:19:53

-

浏览量:14238次2020-12-16 01:39:47

-

浏览量:10692次2020-12-12 23:47:07

-

浏览量:15254次2020-12-15 01:26:18

-

浏览量:12954次2020-12-10 00:29:44

-

浏览量:13586次2020-12-07 00:58:01

-

浏览量:3057次2022-08-17 09:00:19

-

2020-12-27 02:15:14

-

浏览量:2490次2020-06-22 14:08:18

-

浏览量:1999次2019-08-21 18:07:07

-

浏览量:1878次2019-07-09 14:09:17

-

浏览量:2377次2020-01-17 09:30:59

-

浏览量:1384次2020-11-04 15:32:57

-

浏览量:2055次2019-08-08 17:11:28

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友