高速串行总线的设计基础(一)同步时序模型介绍

前言

高速信号设计涉及到方方面面的知识积累,也许你认为即使没有掌握甚至没有听过一些高速设计的专业术语,也没有关系?因为专业集成的IP可以帮你解决这一问题,但殊不知,根基不牢,地动山摇!基础不牢固,你可能永远成不了一个expert,甚至难以成为一位出色的工程师。

本系列文章通过联系高速串行的相关知识,从基础到进阶,可以助你很好地理解高速串行设计中的重难点。

短期可助于理解各厂家集成IP,高速协议等,长期有助于技术积累,提高技术修养。

相信无论新手还是行家,都会有所收益。

以下是本系列第一篇,同步时序模型介绍。

芯片间通信的时序模型

大体上,有三种时序模型用于芯片间通信,那就是系统同步,源同步以及自同步,下面分别介绍:

系统同步

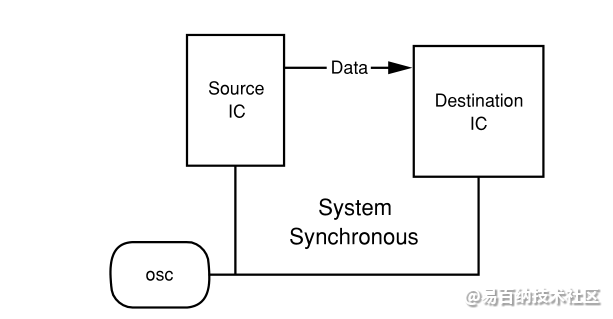

所谓的系统同步,即在IC之间通信中,外部公共时钟应用于两个IC之间,并用于数据发送以及接收。

系统同步是最常用的同步方式,其示意图如下:

这是一种很常见的电路模型,在IC应届生招聘时,这种类型的时序分析题,也最为常见。

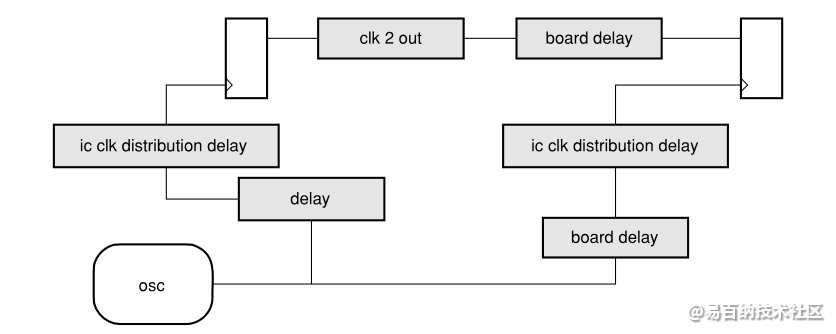

如下图为上图的详细时序模型:

阴影部分为必须要考虑的延迟。

由于具体时序分析计算非本文重点,因此不在多余赘述,如有需要可以参考:

时序分析基础概念

源同步

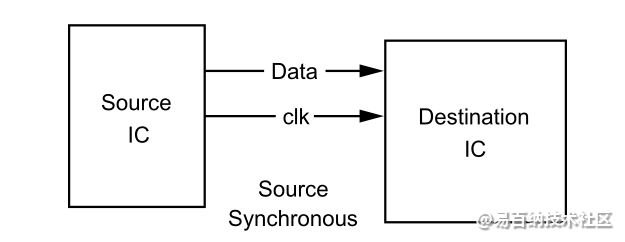

所谓的源同步,即两个IC之间通信,发送IC会生成一个伴随数据的时钟,接收IC使用此转发时钟进行数据接收。

源同步电路图如下:

这种同步方式的特点是时钟副本与数据一同发送到目的IC。

由于数据与时钟一起发送,因此需要调整转发时钟的输出时间,数据线与时钟线的走线长度必须匹配。

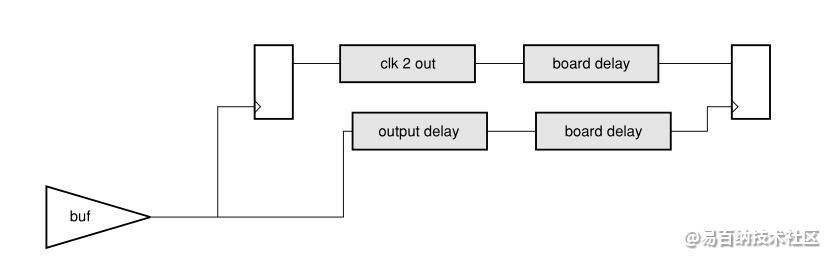

其时序模型如下:

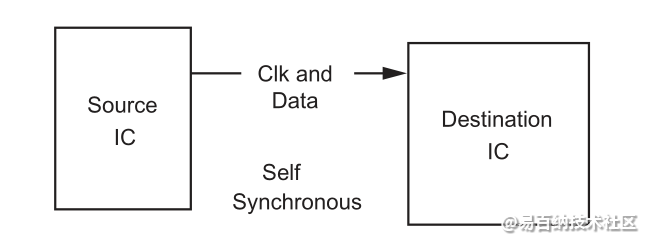

自同步

所谓自同步,即两个IC之间同步,其中发送IC生成的包含数据和时钟的流发送至接收IC。

自同步的电路图如下:

如果你曾使用过高速串口相关的IP或者高速串口相关的协议,你会发现很多高速串口使用这种方式进行数据传输。例如Xilinx的Transceiver以及基于Transceiver的几乎所有其他高速协议,如aurora,srio等。

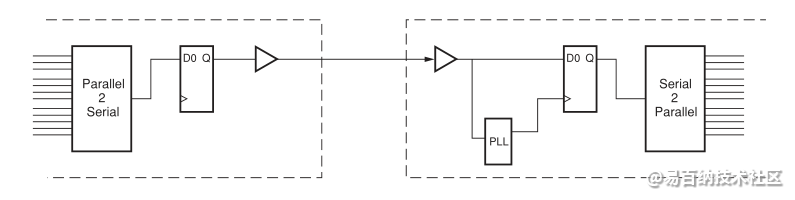

其时序模型如下:

可见,自同步接口主要有三个部分:

- 并串转换

- 串并转换

- 时钟数据恢复

下面分别解释:

并串转换

并串转换的原理十分简单,可以使用移位寄存器实现,即将并行数据不断进行移位,取最高位或最低位(最高或最低取决于左移还是右移)作为串行输出即可。

下面给出部分Verilog描述的简单示例,以助于理解:

// Verilog example

assign sDOut = shift[7];

always@(posedge clk8x)

begin

if(en == 1'b1) // 1 pulse every 8 clk8x period

begin

shift <= pDout; // MSB first

end

else

begin

shift <= {shift[6:0], 1'b0};

end

end- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

这仅仅是给出一个简单的理解方式,实际应用肯定会更加灵活,例如并行数据需要更新,则使用可加载数据的移位寄存器,

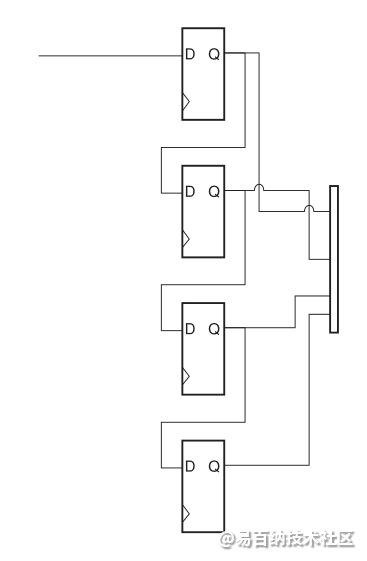

如下示意图:

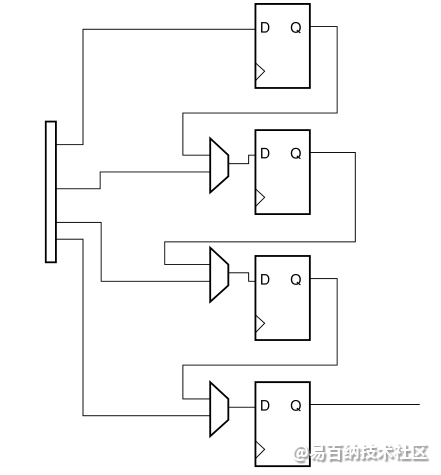

当然还有除了移位寄存器以外的其他方式实现并串转换,例如旋转选择器(Revolving Selector),如下示意图:

其设计方式可自行谷歌。

串并转换

相对于并串转换,串并转换让人更加的熟悉,这源于学习过程中更加的常见,就连应届生笔试题也更加青睐于此,所谓懂了串并转换,还不懂并串转换?

确实如此,二者是一个逆过程,串并转换自然可以使用移位寄存器实现,串行数据不断移位形成并行数据,如下同样给出一段简单的串并转换Verilog部分设计,以助于理解:

always @ (posedge clk) begin

qtemp <= {qtemp[6:0], din};

end

- 1

- 2

- 3

- 4

- 5

时机一到,便取出并行数据。

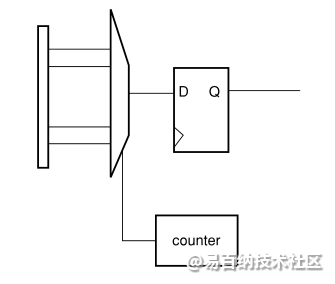

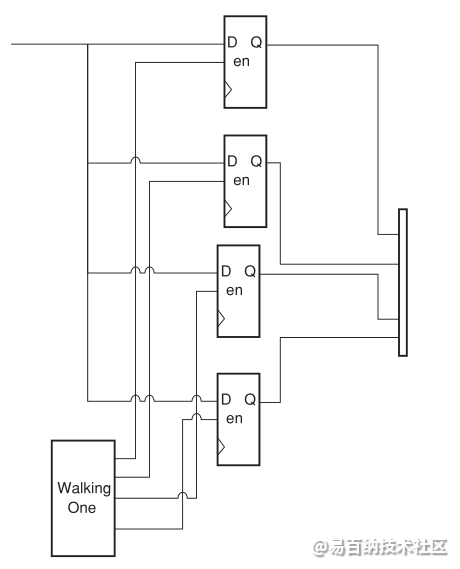

如下为串并转换示意图:

相对于并串转换的旋转选择(Revolving Selector)实现方式,串并转换对应的有旋转使能(Revolving Enables)方式,示意图如下:

时钟/数据恢复

与系统同步提供的公共时钟以及源同步提供的同数据一起发送的时钟不同,时钟恢复过程使用锁相环(PLL)来合成与生成输入串行数据流的时钟频率相匹配的时钟。

锁相环就有这个能力,为什么呢?

这里不再给出繁琐的锁相环原理图,只给出锁相环的定义即可体会:

锁相环是一种采样参考时钟和输入信号并创建一个锁定到输入信号的新时钟的电路。

参考文章

- 分享

- 举报

暂无数据

暂无数据-

浏览量:12420次2020-12-05 03:10:25

-

浏览量:9605次2020-12-20 00:26:35

-

浏览量:19271次2020-12-07 00:56:53

-

浏览量:8321次2020-12-20 14:19:53

-

浏览量:14235次2020-12-16 01:39:47

-

浏览量:17027次2020-12-03 00:29:52

-

浏览量:10689次2020-12-12 23:47:07

-

浏览量:12950次2020-12-10 00:29:44

-

浏览量:15250次2020-12-15 01:26:18

-

浏览量:11709次2020-12-19 13:31:48

-

浏览量:13580次2020-12-07 00:58:01

-

2020-12-27 02:15:14

-

浏览量:3446次2020-08-17 12:21:14

-

浏览量:9365次2021-02-20 17:50:13

-

浏览量:2267次2023-12-25 13:49:55

-

浏览量:768次2023-08-30 18:29:45

-

浏览量:3731次2021-12-22 09:00:26

-

浏览量:2649次2021-12-24 09:00:17

-

浏览量:3453次2022-08-16 19:12:41

-

广告/SPAM

-

恶意灌水

-

违规内容

-

文不对题

-

重复发帖

李锐博恩

微信支付

微信支付举报类型

- 内容涉黄/赌/毒

- 内容侵权/抄袭

- 政治相关

- 涉嫌广告

- 侮辱谩骂

- 其他

详细说明

微信扫码分享

微信扫码分享 QQ好友

QQ好友